# GMD – Forschungszentrum Informationstechnik GmbH

European Research Consortium for Informatics and Mathematics

# GMD Report 91

Stefania Gnesi, Ina Schieferdecker, Axel Rennoch (Eds.)

5th International ERCIM Workshop on Formal Methods for Industrial Critical Systems

Proceedings of FMICS'2000 April 3-4, 2000 in Berlin © GMD 2000

GMD – Forschungszentrum Informationstechnik GmbH Schloß Birlinghoven D-53754 Sankt Augustin Germany Telefon +49 -2241 -14 -0 Telefax +49 -2241 -14 -2618 http://www.gmd.de

In der Reihe GMD Report werden Forschungs- und Entwicklungsergebnisse aus der GMD zum wissenschaftlichen, nichtkommerziellen Gebrauch veröffentlicht. Jegliche Inhaltsänderung des Dokuments sowie die entgeltliche Weitergabe sind verboten.

The purpose of the GMD Report is the dissemination of research work for scientific non-commercial use. The commercial distribution of this document is prohibited, as is any modification of its content.

Anschriften der Herausgeber/Addresses of the editors: Dr. Stefania Gnesi Istituto di Elaborazione della Informazione CNR - Consiglio Nazionale delle Ricerche Area della Ricerca di Pisa Via Alfieri, 1 I-56010 Ghezzano - Pisa E-mail: gnesi@iei.pi.cnr.it

Dr. Ina Schieferdecker Axel Rennoch Institut für Offene Kommunikationssysteme GMD – Forschungszentrum Informationstechnik GmbH Kaiserin-Augusta-Allee 31 D-10589 Berlin E-mail: {schieferdecker, rennoch}@fokus.gmd.de

ISSN 1435-2702

# Preface

The European Research Consortium for Informatics and Mathematics (ERCIM) has recently celebrated its 10th anniversary. The ERCIM Working Group on Formal Methods for Industrial Critical Systems (FMICS) is organizing its 5th International Workshop. FMICS workshops are dedicated to interested researchers at ERCIM sites, universities and industry active in the industrial application of formal methods. Among a variety of formal methods conferences and workshops FMICS is increasing its popularity. The idea of FMICS workshops is to attract people with industrial relevant topics, with internationally well-known invited speakers and with high-quality technical papers in combination with a discussion podium for the exchange of ideas. The workshop character of FMICS is realized on a minimal cost base. This time, FMICS is organized right after ETAPS'2000 - the European Joint Conferences on Theory and Practice of Software in Berlin.

After starting the FMICS workshop series 1996 in Oxford (UK) further workshops followed 1997 in Cesena (I), 1998 in Amsterdam (NL) and 1999 in Trento (I). In 2000, the workshop is hosted and organized at the GMD Research Institute for Open Communication Systems (FOKUS) in Berlin, Germany.

This year' workshop includes sessions on modelling, verification, testing and software development, MSC/SDL, and various applications and case studies. We are pleased to present two interesting invited talks: Günter Karjoth, IBM Zurich (CH), addresses the value of formal methods for security properties such as confidentiality and authenticity. Holger Hermanns, University of Twente (NL), investigates in the performance and reliability model checking and construction.

We wish to thank the members of the programme committee, especially the FMICS working group chairman Hubert Garavel, for the excellent assistance during the planing of the workshop, the invited speakers, the authors and the reviewers for their scientific contributions, the people from the GMD Fokus Competence Center TIP for preparing the workshop event, and ERCIM and GMD for their financial and organizational support of FMICS.

Berlin, April 2000

Stefania Gnesi, Ina Schieferdecker, Axel Rennoch

**Keywords:** Formal Methods, Formal Description Techniques (FDT), Modelling, Specification, Verification, Prototyping, Testing, Software development, Industrial applications.

Further information: FMICS homepage http://www.inrialpes.fr/vasy/fmics/

# Vorwort

Das Europäische Forschungskonsortium für Informatik und Mathematik (ERCIM) hat gerade sein 10jähriges Jubiläum gefeiert und die ERCIM Arbeitsgruppe zu Formalen Methoden für Industrie-kritische Systeme (FMICS) organisiert bereits ihren fünften internationalen Workshop. FMICS Workshops wenden sich an interessierte Forscher aus ERCIM Instituten, Universitäten und der Industrie, die sich aktiv an der Anwendung formaler Methoden für industrielle Anwendungen beteiligen. Trotz der Vielzahl von Konferenzen und Workshops über formale Methoden erfreut sich FMICS wachsender Beliebtheit. Es ist der Gedanke von FMICS Workshops die Fachleute mit industrierelevanten Themen anzusprechen, mit international anerkannten eingeladenen Vortragenden und mit hochqualifizierten technischen Beiträgen in Kombination mit einem Forum für den Austausch von Ideen. Der Workshop Charakter von FMICS wird auf der Basis niedriger Kosten durchgeführt. Diesmal wird FMICS direkt im Anschluß an ETAPS'2000 - den Europäischen Konferenzen für Softwaretheorie und -praxis in Berlin organisiert.

Nach dem Start der FMICS Workshops 1996 in Oxford (UK) folgten Workshops 1997 in Cesena (I), 1998 in Amsterdam (NL) und 1999 in Trento (I). Im Jahr 2000 findet der Workshop beim GMD Forschungsinstitut für Offene Kommunikationssysteme (FOKUS) in Berlin statt.

Der diesjährige Workshop umfaßt die Themengebiete Modelling, Verification, Testing und Software Entwicklung, MSC/SDL, sowie vielfältige Anwendungen und Fallstudien. Wir freuen uns sehr zwei interessante eingeladene Vorträge zu präsentieren: Günter Karjoth, IBM Zürich (CH), erörtert den Wert formaler Methoden für Sicherheitsaspekte wie Vertraulichkeit und Authentizität. Holger Hermanns, Universität Twente (NL), geht ein auf die Konstruktion und Überprüfung von Leistungs- und Zuverlässigkeitsmodellen.

Abschießend möchten wir den Mitgliedern des Programmkommitees danken, insbesondere dem Vorsitzenden der FMICS Arbeitsgruppe Hubert Garavel, für die hervorragende Unterstützung bei der Vorbereitung des Workshops, außerdem den eingeladenen Vortragenden, den Autoren der Beiträge und den Gutachtern für ihre wissenschaftlichen Beiträge, den Mitarbeitern des GMD Fokus Competence Center TIP bei der Ausrichtung des Workshops, sowie ERCIM und der GMD für ihre finanzielle und organisatorische Unterstützung von FMICS.

Berlin, April 2000

Stefania Gnesi, Ina Schieferdecker, Axel Rennoch

**Schlagworte:** Formal Methods, Formal Description Techniques (FDT), Modelling, Specification, Verification, Prototyping, Testing, Software development, Industrial applications.

Weitere Informationen: FMICS homepage http://www.inrialpes.fr/vasy/fmics/

# **Programme Committee**

Juan Bicarregui (CLRC Abington, UK) Lars-åke Fredlund (SICS Stockholm, S) Hubert Garavel (INRIA Rhone-Alpes, F), FMICS chair Stefania Gnesi (CNR/IEI Pisa, I), PC co-chair Jan Frisco Groote (CWI Amsterdam, NL) Diego Latella (CNR/CNUCE Pisa, I) Axel Poigné (GMD/AiS Birlinghofen, D) Ina Schieferdecker (GMD/Fokus Berlin, D), PC co-chair Jan Tretmans (University of Twente, NL) Ulrich Ultes-Nitsche (University of Southampton, UK) Adam Wolisz (TU Berlin, D)

# **List of Reviewers**

Axel Belinfante, Pierfrancesco Bellini, Juan Bicarregui, Michael J. Butler, Gennady Chugunov, Alessandro Fantechi, Lars-åke Fredlund, Hubert Garavel, Pablo Giambiagi, Stefania Gnesi, Jan Friso Groote, Dilian Gurov, Izak van Langevelde, Diego Latella, Gabriele Lenzini, Mang Li, Giuseppe Manco, Andrew Martin, Mieke Massink, Radu Mateescu, Brian M. Matthews, Franco Mazzanti, Thomas Noll, Axel Poigné, Jaco van de Pol, Michel Reniers, Axel Rennoch, Brian Ritchie, Eric Rutten, Ina Schieferdecker, Jan Tretmans, Ulrich Ultes-Nitsche, Adam Wolisz.

# **Organizing Committee**

(GMD/Fokus Berlin, D)

Birgit Benner Axel Rennoch Ina Schieferdecker Theofanis Vassiliou-Gioles

# Contents

# **Invited Talks**

| •  | <i>G. Karjoth:</i><br>From Dining Philosphers to Dining Cryptographers                                                                                      | 9   |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| •  | <i>H. Hermanns:</i><br>Performance and reliability model checking and model construction                                                                    |     |

| Se | ession 1: Applications                                                                                                                                      |     |

| •  | A. <i>Requet</i> :<br>A B Model for Ensuring Soundness of a Large Subset of the Java Card<br>Virtual Machine                                                | 29  |

| •  | <i>F. Maraninchi, Y. Rémond</i> :<br>Applying Formal Methods to Industrial Cases:<br>The Language Approach (The Production-Cell and Mode-Automata)          | 47  |

| Se | ession 2: Verification                                                                                                                                      |     |

| •  | <i>R. Mateescu, M. Sighireanu:</i><br>Efficient On-the-Fly Model-Checking for Regular Alternation-Free<br>Mu-Calculus                                       | 65  |

| •  | <i>F. Baray, P. Wodey</i> :<br>Verification in the Codesign process by means of LOTOS based<br>model-checking                                               | 87  |

| •  | <i>D. Gurov, G. Chugunov</i> :<br>Verification of Erlang Programs: Factoring out the Side-effect-free Fragment                                              | 109 |

| Se | ession 3: Testing & Software development                                                                                                                    |     |

| •  | L. du Bousquet, F. Ouabdesselam, I. Parissis, JL. Richier, N. Zuanon:<br>Specificaton-based Testing of Synchronous Software                                 | 123 |

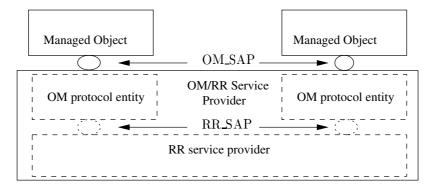

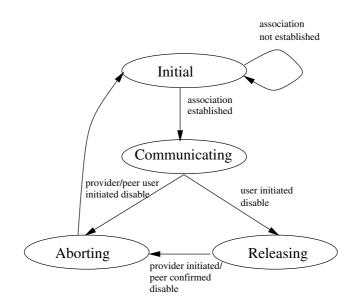

| •  | <i>I. Schieferdecker, M. Li, A. Rennoch:</i><br>Formalization and Testing of Reference Point Facets                                                         | 141 |

| •  | <i>B. Wu, L.M. Lai, D.R.W. Holton</i> :<br>Towards a Mechanised Software Development Method                                                                 | 161 |

| •  | <i>P. Bertoli, A. Cimatti, P. Traverso</i> :<br>Integrating formal methods into the development cycle of a safety-critical<br>embedded software system      | 187 |

| Se | ession 4: MSC / SDL                                                                                                                                         |     |

| •  | <i>L. Hélouët, C. Jard</i> :<br>Conditions for synthesis of communicating automata from HMSCs                                                               | 203 |

| •  | <i>M.M. Gallardo, P. Merino</i> :<br>A Practical Method to Integrate Abstractions into SDL and MSC based Tools                                              | 225 |

| •  | <i>R. Schröder, M. v. Löwis of Menar</i> :<br>Experiences with Tool development of SDL in Combination with ASN.1<br>for Communication Protocol Applications | 247 |

# Session 5: Modelling

| • | <i>R.J. Back, C. Cerschi</i> : Modeling and Verifying a Temperature Control System using Hybrid Action System                                                | 265 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | D. Beyer, C. Lewerentz, H. Rust:<br>Modelling and Analysing the Railroad Crossing in a Modular Way                                                           | 287 |

| • | S. Gnesi, D. Latella, G. Lenzini, C. Abbaneo, A. Amendola, P. Marmo:<br>A Formal Specification and Verification of a Safety Critical Control System          | 305 |

| S | ession 6: Cases Studies                                                                                                                                      |     |

| • | <i>T. Willemse, J. Tretmans, A. Klomp</i> : A Case Study in Formal Methods:<br>Specification and Validation of the OM/RR Protocol                            | 331 |

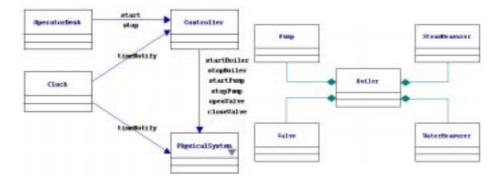

| • | <i>P. Carreira, M. Costa:</i> Automatically Verifying an Object-Oriented Specification of the Steam-Boiler System                                            | 345 |

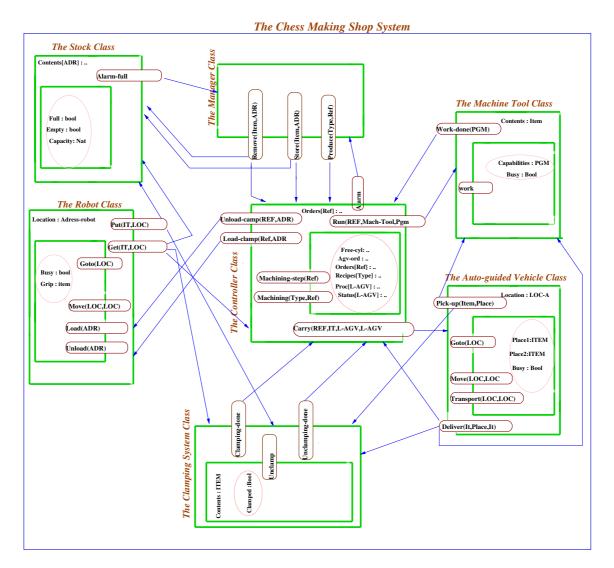

| • | <i>N. Aoumeur, G. Saake</i> :<br>Cooperative Information Systems Modelling and Validation Using<br>the Co-nets Approach: The Chessmen Making Shop Case Study | 361 |

# From Dining Philosophers to Dining Cryptographers

Günter Karjoth IBM Research Zurich Research Laboratory

#### Abstract

In theory, formal methods give us the ability to determine whether properties we ascribe to specifications or software systems hold for certain. However, the assurance that can be obtained from formal methods comes at a price. In the eighties, the computer networks community invested a lot in tools, theories, and case studies. They used formal methods to provide a rigorous and unambiguous way of designing and documenting protocols, to allow formal analysis (verification/performance analysis) before protocols are implemented, and to allow automatic code generation from the formal specification. The seminal work on Communicating Finite State Machines was followed by approaches based on process algebra and temporal logic, to give an example. In the last decade, however, attention shifted to computer security as an application area where the expense of faulty software would make the application of formal methods cost-effective. But security properties such as confidentiality and authenticity are often difficult to characterize formally (or even informally). In our presentation, we review ways in which above communities describe their domain-specific properties, how mechanisms are captured, and how protocols are analyzed. We conclude that despite the different objectives, even "traditional" methods can be sucessfully applied in the field of computer security. As an example, we describe our work on giving an operational semantics of the JavaCard Virtual Machine and using a well-known model checker for analysis.

# Performance and reliability model checking and model construction

#### H. Hermanns

University of Twente, Faculty of Computer Science, Formal Methods and Tools Group, P.O. Box 217, 7500 AE Enschede, the Netherlands

hermanns@cs.utwente.nl

#### Abstract

Over the last decade formal methods have been extended towards performance and reliability evaluation. This paper tries to provide a rather intuitive explanation of the basic concepts and features in this area. The intention is to give an illustrative introduction to the basics of stochastic models, to stochastic modelling using process algebra, and to model checking as a technique to analyse stochastic models.

## 1 Introduction

Modern industrial systems, such as communication networks, transport systems, or manufacturing systems, are more and more operating in a stochastic context: communication lines can break, buffers can overflow, a lorry with material for a just-in-time production line might get stuck in a traffic jam. Each of these phenomena is stochastic by nature, its absence or presence can only be predicted up to some probability. Since these stochastic phenomena have impact on the system under consideration, it is nowadays commonly agreed that the systems themselves exhibit stochastic behaviour. As a consequence, performance and reliability studies of industrial systems have to take into account that rigid assessments ("It is impossible that the system fails") only hold under unrealistic assumptions.

The construction and analysis of models suited for performance and reliability studies of real-world phenomena is a difficult task. To a large extent this problem is attacked using human intelligence and experience. Due to increasing size and complexity of systems, this tendency seems even growing: performance as well as reliability modelling becomes a task dedicated to specialists, in particular for systems exhibiting a high degree of irregularity. Traditional performance models such as queueing networks lack hierarchical composition an abstraction means, significantly hampering the modelling of systems that are developed nowadays.

On the other hand, for describing the plain functional behaviour of systems various specification formalisms have been developed that are strongly focussed on the facility to model systems in a compositional, hierarchical manner. A prominent example of such specification formalisms is the class of *process algebra* [14]. Developed on a strong mathematical basis, process algebra has emerged as an important framework to achieve compositionality. Process algebra provides a formal apparatus for reasoning about structure and behaviour of systems in a compositional way.

During the last decade, stochastic process algebra (SPA) has emerged as a promising way to carry out compositional performance and reliability modelling, mostly on the basis of continuous time Markov chains (CTMCs). Following the same philosophy as ordinary process algebra, the stochastic behaviour of a system is described as the composition of the stochastic behaviours of its components.

To analyse properties of formally specified models *model checking* is a very successful technique to establish the correctness of the model, relative to a given set of temporal logic properties the model is supposed to satisfy [9, 10]. Using efficient encoding techniques, model checking has been applied to industrial size designs involving more than  $10^{100}$  states.

It appears valuable to apply efficient model checking techniques also to performance and reliability properties of industrial systems. Since performance and reliability models are stochastic in nature, the properties of interest are stochastic as well, and have to be described in an appropriate extension of a temporal logic. The model checking algorithm then involves the calculation (or approximation) of probabilities of certain properties to hold.

This paper tries to provide a rather intuitive explanation of the basic concepts and features of stochastic models, of stochastic modelling using process algebra, and of model checking as a technique to analyse stochastic models. For the sake of being illustrative the paper tends to treat various fine points much more simplistic than the advanced reader probably desires.

The paper is organised as follows. Section 2 introduces the basic concepts of stochastic models. Section 3 exemplifies the use of process algebra for modelling stochastic phenomena by means of a real-world example, and Section 4 describes the model checking approach to analyse stochastic models. Section 5 concludes the paper.

## 2 Stochastic models

A stochastic model is basically a means to describe the evolution of a real-world phenomenon as time<sup>1</sup> passes, with a particular emphasis on phenomena with stochastic timing characteristics. In other words, repeated observations of the same phenomenon can have varying timing characteristics, but their variation exhibits a specific kind of randomness.

Figure 1: At the door of a gambler

As an example, consider a gambler that throws a die every minute. Observing the gambler, one might wish to study a phenomenon, such as the time that it takes to throw a six. Starting the observation at some arbitrary minute, one counts the minutes till the

<sup>&</sup>lt;sup>1</sup>It is a bit narrow minded to consider the time domain as the only possible domain of variability. Spatial Markov processes, for instance, are used to describe the evolution of some phenomenon as its position in some appropriate space changes, as opposed to the time.

die shows a six. Obviously, repeated observations will usually lead to different results, at least if gambling with a fair die. Nevertheless, the variation among these observations exhibits a specific kind of randomness: The time needed to throw a six is known to follow the so-called geometric probability distribution.

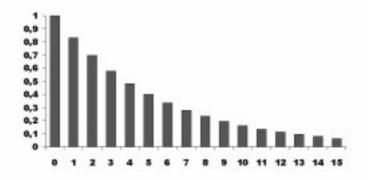

**Probability distribution** A probability distribution is a function that assigns a probability (a real value between 0 and 1) to each element of some given set. For instance, the geometric probability distribution P assigns probabilities to natural numbers. For the gambler, these numbers enumerate the minutes he is already gambling (remind that he throws the die once per minute). For some t, P(t) is the probability to see the first six after t minutes, and is given by:

$$P(\text{see the first six after } t \text{ minutes}) = 1 - \left(\frac{5}{6}\right)^t$$

,

or complementary,

$$P(\text{still no six after } t \text{ minutes}) = \left(\frac{5}{6}\right)^t$$

For instance, the probability of not having seen a six after t = 2 minutes (i.e. after throwing the die twice) is 25/36.

To make the example a bit more interesting, assume that the gambler is throwing the die somewhere outside his office. Before leaving his office he has put a note on the door, as depicted in Figure 1. In fact, his intention is to return to his office as soon as the die shows a six. Now let us assume that someone arrives at his door, finding the door closed. How long will he have to wait for the gambler? Probably just a minute, but probably (more likely) more than a minute, probably (unlikely) more than ten minutes. Since this experiment is governed by the above geometric distribution, the probability of having to wait more than a minute is 5/6, the probability of waiting more than ten minutes is  $(5/6)^{10}$ . Figure 2 depicts these probabilities for the first 15 minutes.

Figure 2: A geometric probability distribution: Will the gambler still be absent at time t?

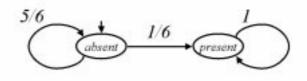

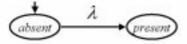

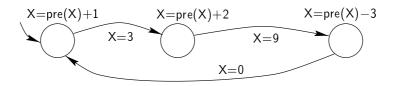

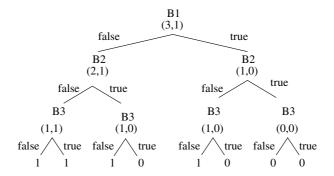

**Markov chain** Having explained the gambler's behaviour, we are now in the position to specify a stochastic model of his behaviour. It is depicted in Figure 3. As many other (formal or semi-formal) models, the model is a graph, consisting of states and transitions. There are two states in this model. One state represents the absence of the gambler, one represents his presence in the office. The model contains three transitions representing possible events that might induce a change of state. One transition indicates that every

minute the absent gambler has a 1-out-of-6 chance to return to his office. Another transition indicates that with probability 5/6 the absent gambler will miss the six, and hence has to stay absent for at least another minute. In case he is back in his office, the third transition indicates that he stays there (ad infinitum). The small arrow on top of the left state indicates the initial state. i.e. the state occupied at time zero.

Figure 3: A discrete-time Markov chain describing the gambler's behaviour

The stochastic model of the gambler's behaviour is a very simple one. It is a Markov chain, named after A.A. Markov who studied models of this kind in the beginning of the last century. More specific, it is a discrete-time Markov chain (DTMC), since state changes are only possible at discrete points in time: The gambler can return to his office precisely every minute only. DTMCs restrict the possible time points for state changes to a discrete subset of dense real time. As in our example, these time points are often (but not necessarily) equidistant.

**Markov chain analysis** For a given stochastic model, such as a Markov chain, there is usually a variety of interesting properties that one might want to study. Two substantially different classes of properties can be distinguished. *Transient analysis* investigates the evolution of the model up to a given point in time. On the contrary, *steady-state analysis* focusses on the long-run average behaviour. It requires that on the long-run initial start-up effects (the transient phase) do not have a measurable impact.

A trivial steady-state property for the gambler is that with probability 0 he will be absent on the long-run. As an example for a transient property, we have already indicated that the probability of still being absent after 10 minutes is  $(5/6)^{10}$ . A variant of transient analysis gives us that on the average it takes the gambler six minutes to throw a six. So, the sign on the office door is essentially right, the gambler will be back in six minutes, on the average.

**Analysis techniques** In practice, three fundamentally different techniques are used to analyse stochastic models. They differ with respect to accuracy, applicability and computational requirements. Here, we only give a concise subjective summary on differences and similarities, and refer to Jain's textbook [25] for a more elaborate discussion.

- Simulation The stochastic model is mimicked by a simulator throwing dice and producing statistics of simulation time spent in states. The fraction of simulation time spent in a particular state is used as an estimate for the state probability. This technique is generally applicable, in particular it is suitable also for non-Markov stochastic models. However, it should be noticed that good accuracy tends to require long simulation runs, and hence limits applicability in practice.

- Numerical solution The transient or steady-state behaviour of a stochastic model is obtained by an exact or approximate algorithm where model parameters are instantiated with numerical values. This approach gives accurate results in general, up

to numerical precision. On the other hand, its applicability is restricted to finite Markov chains (with a few exceptions, see e.g. [17, 24]). Furthermore the number of states of the model is a limiting factor, because of computational requirements. A very readable textbook on numerical solution methods is [26].

Analytical solution The transient or steady state property of interest is expressed as a closed formula over the parameters of the model. This is the most simple, accurate and elegant technique. However, analytical solutions are available only for highly restricted classes of stochastic models.

Absence of memory Markov chains are widely used as stochastic models of real-world phenomena. This is mainly because they possess a distinguishing feature that simplifies both modelling and analysis. They obey the so called *memoryless property*: The future evolution of a Markov chain model is independent of the past, it only depends on the state currently occupied. This property is best explained in terms of the absent gambler. The probability that the gambler returns to his office after one minute from now is 1/6, independent of the fact that someone might be waiting for him in front of his door for ten minutes (or years) already. This is a direct consequence of the fact that a fair die has no memory; the die does not change if it has not shown a six for ages. This should not be mixed with the fact that the probability of actually having to wait for ten minutes is low,  $(5/6)^{10}$ . Under the assumption that this unlikely case becomes reality, it still needs another six minutes waiting time on the average, as the sign on the door indicates.

**Discrete vs. continuous time** Discrete-time Markov chains are convenient to describe the stochastic evolution of sequential systems. In each state, the outgoing transitions define how the probability mass will be spread at the next time instant. Since DTMCs evolve in a discrete time domain, the flow of probability is not continuous, instead it possesses jumps, and remains unchanged in the time interval between two relevant time points, such as between t = 2 and t = 3. This is relatively convenient for sequential systems. But it is not convenient in a concurrent probabilistic setting, for both theoretical as well as pragmatic reasons.

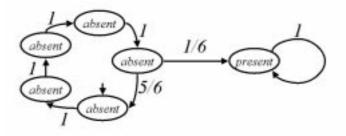

As an example, imagine that the gambler's office door is checked by some customer. In case he finds the door closed he probabilistically decides to check again after either 24 or 48 seconds. Note that the basic time unit of this DTMC is 24 seconds. For instance, one might want to study the probability that the customer finds an open door after 72 seconds.

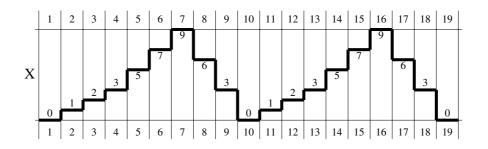

Figure 4: A discrete-time Markov chain describing the gambler's behaviour if observed every 12 seconds

Without specifying the model in all detail, we are already in the position to understand the problem: In order to develop a concurrent probabilistic model of both gambler and customer, we have to relate events that may happen at every 24 seconds to events that happen may every 60 seconds. One solution is to change the basic time unit of both models to 12 seconds, the greatest common divisor of their basic time units. In other words, the gambler's model is blown up to record in 4 additional states that while being absent, four times 12 seconds pass till he may throw the die in the last twelve seconds of the minute (cf. Figure 4).<sup>2</sup> After a similar change in the customer's sub-model, one can combine both models (by essentially taking the crossproduct of states and the products of transition probabilities). To determine the concurrent stochastic behaviour at the next point in time (i.e. after 12 seconds) one synchronously updates the respective states in the two sub-models, because state changes now occur exactly at the same time. The probability for such a joined transition is given by the product of the transition probabilities in the sub-models.

This strategy has two practical limitations, at least. First, it tends to induce a tremendous blow-up of the size of the model, caused by the number of auxiliary states needed in general. Second, it fails if there is no greatest common divisor, for instance if the customer shows up every  $\pi$  seconds, or if time points are not equidistant. As a consequence, virtually all stochastic models of concurrent systems are developed in a continuous time domain, including models of modern computer systems (even though each component of such a system can be considered as working in discrete time, changing state according to fixed frequency clock ticks).

**Continuous-time Markov chains** Continuous-time Markov chains (CTMCs) are Markov chains interpreted over continuous time, in contrast to DTMCs. They are widely used to model the stochastic behaviour of concurrent real-world phenomena, due to their mathematical simplicity, paired with modelling convenience.

How does the continuous-time variant of the gambler look like? In a continuous time setting, the absent gambler is able to return to his office at arbitrary time points. Still we may assume that he has a 1-out-of-6 chance to return within the first minute, and so on. Under these assumptions, we get the following probability distribution:

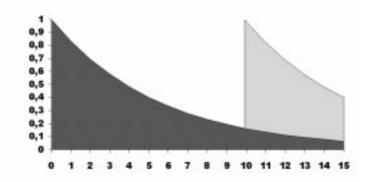

$P(\text{still no six after } t \text{ minutes}) = (5/6)^t.$

What is this? It perfectly resembles the geometric distribution appearing in the discrete time case, but it is different. The difference is that the domain of this function is the real line, instead of the natural numbers. In other words, the above function assigns a probability to all time points one may think of, instead of only to each minute. Hence, there is now a non-zero probability of returning within the first second already, namely  $1 - (5/6)^{1/60}$ . Instead of being a geometric distribution, this function belongs to the class of so-called (negative) exponential probability distributions, because  $(5/6)^t$  can be rewritten to  $e^{-\lambda t}$ , with  $\lambda = \ln 6 - \ln 5 \approx 0.18232$ . The value  $\lambda$  is a parameter of the distribution, usually called 'rate'. For t < 15, the probabilities determined by this exponential probability distribution are depicted (by the dark plot) in Figure 5. The expected value of an exponential distribution (i.e. the average duration) is  $1/\lambda$ , the reciprocal value of the rate. So, the (continuously gambling) gambler returns after 5.48 minutes on the average, not after six minutes.<sup>3</sup>

$<sup>^{2}</sup>$ Note that this change encodes some kind of memory in an otherwise memoryless model: A sequence of states is used to keep track of the time already spent in the original state.

<sup>&</sup>lt;sup>3</sup>Remark that since the probability mass is flowing continuously, a sixth of the mass leaks prior to the first minute tick. Hence, to some extent the probability mass flows earlier than in the discrete-time case, where a sixth of the probability mass jumps a bit later, at each minute tick. As a consequence, the average time needed for the continuously gambling gambler is slightly smaller than 6 minutes. To obtain an average duration of 6 minutes, one has to adjust  $\lambda$  to 1/6.

Figure 5: A negative exponential probability distribution with  $\lambda = \ln 6 - \ln 5$ : Will the gambler still be absent at time t?

A continuous-time Markov chain model of this absent gambler is depicted in Figure 6. It consists of two states, and one transition. The transition represents that the gambler can return to his office with rate  $\lambda$ . The gambler stays absent as long as needed to throw a six. According to the value of  $\lambda$  the probability mass flows from state to state as time passes, that is, a fraction of  $1 - e^{\lambda} = 1/6$  of the probability mass flows from the left state to the right state per minute.<sup>4</sup>

Figure 6: A continuous-time Markov chain describing the gambler's behaviour

Though the above example shows one of the simplest CTMCs one can think of, it exhibits all relevant ingredients: states and transitions, the latter labelled with rates of exponential distributions. It is worth to note that – in correspondence to geometric distributions – exponential distributions are memoryless: The future evolution of a CTMC model is independent of the past, it only depends on the state currently occupied. In terms of the gambler, the probability that the absent gambler returns to his office within the next minute is 1/6, independent of the fact he might have been absent for ages already.

Figure 5 allows us to illustrate the memoryless property in a graphical way [1]. Consider the case that the gambler is still gambling after minute 10. We obtain the probability that he will still be gambling at time 10 + t by stretching the tail of the distribution (from time 10 to  $\infty$ ) upwards in such a way that it reaches probability 1 for minute 10, i.e. t = 0. As a matter of fact, this stretching returns precisely the original distribution, as indicated by the light-grey plot in Figure 5, except that it is shifted by 10 minutes. (The same graphical illustration holds for the geometric distribution, but for no other discrete or continuous distribution.)

From a pragmatic point of view, the memoryless property is rather convenient. It simplifies analysis, but it also simplifies modelling. In particular, it fits well to concurrent stochastic phenomena: If two sub-models, both described in terms of CTMCs, are to

<sup>&</sup>lt;sup>4</sup>Since the gambler continuously tries to return to his office, there is no need to record by an explicit (looping) transition that he might fail for some (continuous) time. For CTMCs, this fact is implicit, while in the DTMC scenario it is not.

be considered concurrently, one can simply interleave their evolution: If one sub-model changes from one state to another, the other sub-model is not affected. The fact that the latter has been staying in some state for some time (the time it took the former sub-model to change state) does not need to be recorded somehow, because it does not alter the future behaviour of the latter sub-model, due to the memoryless property.

Anyway, it should be clearly stated that absence of memory is an assumption that is by far not always justified when modelling real-world phenomena.<sup>5</sup>

## 3 Formal specification of continuous-time Markov chains

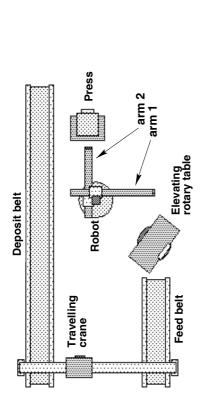

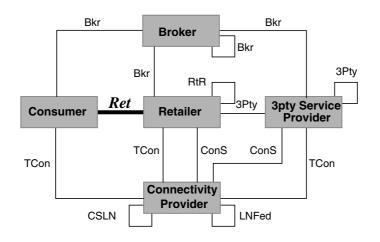

In this section we illustrate the use of formal methods to model a specific aspect of a realworld example as a CTMC. Several formal notations exist that map on CTMCs, among them stochastic Petri nets and stochastic process algebra. Here we restrict ourselves to illustrate the use of process algebra; an introduction to the Petri net based approach can be found for instance in [1]. As opposed to Petri nets, process algebra allows one to compose models out of smaller sub-models, by means of general composition operators such as parallel composition and choice [14], and also more specific constructs, such as exception handling [16]. We will make use of these operators to model a simplified view on the performance and reliability of the Hubble space telescope.

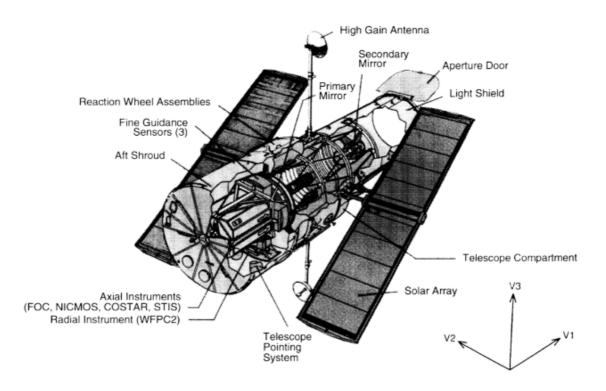

**The Hubble Space Telescope** The Hubble space telescope (HST) is an orbiting astronomical observatory operating from the near-infrared into the ultraviolet (cf. Figure 7). Launched in 1990 and scheduled to operate through 2010, the HST carries a variety of instruments producing imaging, spectrographic, astrometric, and photometric data.

The HST was first conceived in the 1940. It was designed and built in the 1970s and 1980s, aiming at a life span of 15 years with on-orbit servicing taking place on 3 year intervals. The HST is a cooperative program of the National Aeronautics and Space Administration(NASA) and the European Space Agency (ESA). Originally, the HST was designed to be returned to earth via the space shuttle every 5 years with on-orbit servicing every 2.5 years as well. This concept was later scrapped as it was felt there was a too great risk of contamination and structural load to make the concept sound. By the time it was launched the HST cost \$1.5 billion U.S. dollars.

Since the telescope has been launched in April 1990, three servicing missions were carried out: in December 1993, in February 1997, and in December 1999. During the last mission the stabilising unit of the HST was repaired. This was necessary, since severe problems with the reliability of the gyroscopes contained therein had forced the HST to turn into a sleep mode.

The gyroscopes are part of HST pointing system. They provide a frame of reference to determine where it is pointing and how that pointing changes as the telescope moves across the sky. They report any small movements of the spacecraft to the HST pointing and control system. The computers then command the spinning reaction wheels to keep the spacecraft stable or moving at the desired rate in order to avoid that the telescope pointing device staggers. This is of particular importance to avoid that pictures taken by the telescope are blurred. The gyroscopes work by comparing the HST motion relative to the axes of the spinning masses inside the gyroscopes.

$<sup>{}^{5}</sup>$ It is possible to incorporate a notion of memory into the model, similar to what we have used to realise synchronisation of DTMCs (cf. footnote 2). In this way, general non-exponential probability distributions (so-called phase-type distributions) can be represented. The price to pay for this is usually a blow up of the model.

Figure 7: The Hubble space telescope [23].

The HST has a total of six gyroscopes, grouped into three fine guidance sensors. They are arranged in such a way that any three gyroscopes can keep the HST operating with full accuracy. Two fine guidance sensors had been replaced already during the first servicing mission in 1993. Till the end of the second servicing mission in 1997, all six gyroscopes were working normally, but then one after the other failed. Starting from January 1999 the HST had been operating with only 3 functional gyroscopes. As a consequence of a fourth gyro failure on November 13, 1999, HST turned itself into a sleep mode and the science program was suspended. Without operational gyro the telescope would have run the risk to crash. In December 1999, a space shuttle mission was sent to the HST to replace (among others) the complete stabilising unit. This mission was successful.

In order to judge whether the problems of the HST could have been expected beforehand, one might want to study the reliability of the stabilising unit by means of an abstract stochastic model. Here we construct a simple Markov chain model of the gyros, and of their controller. The model is a toy example, developed to give a flavour of Markov chain modelling with process algebra. The model is developed in the algebra of interactive Markov chains (IMC) [18, 20], an extension of basic Lotos [6].

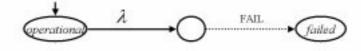

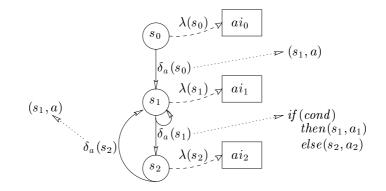

**Basic processes** Each gyro might FAIL after an exponentially distributed amount of time (it is known that exponential distributions fit relatively well to failures of technical equipment). The failure rate  $\lambda$  is the same for all gyros. A GYRO specification is as follows:

$$GYRO = (\lambda)$$

. FAIL. STOP

This specification corresponds to a graphical representation depicted in Figure 8. Apart from a transition labelled  $\lambda$  representing the delay prior to failure, there is a second kind

of transition, indicated by a dotted arrow labelled FAIL. In abstract terms, this transition represents the potential of interaction, i.e. of synchronising with a partner transition (labelled with the same name) in a different sub-model. The potential of interaction between sub-models is one of the well known features offered by a process algebraic approach [6].

Figure 8: A simple interactive Markov chain describing the gyroscope's behaviour

**Parallel composition** Six of these gyros coexist independently in the stabilising unit, together with a controller that keeps track of the status of each gyro, by means of synchronisation on FAIL. This is realized using the operator |[FAIL]| for synchronisation, and ||| to denote independent parallelism (among the gyros):

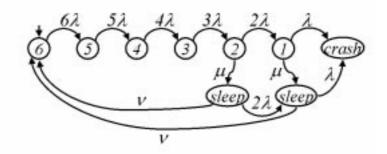

The controller counts the number of failures, and mechanically turns the telescope into sleep mode in case four gyros have failed. To turn into sleep mode requires some time. For the moment we just assume an exponential distribution with rate  $\mu$ . We will explain shortly how to deal with other distributions. After turning on the sleep mode, the controller notifies the base station by means of a SLEEP signal. In the meantime, further gyro failures might occur. If the last gyro fails, a CRASH is assumed to be inevitable. The graphical representation of the controller is depicted in Figure 9.

Figure 9: An interactive Markov chain describing the controller

CONTROLLER = FAIL. FAIL. FAIL. FAIL. FAIL.  $((\mu)$ . SLEEP. STOP ||| FAIL. FAIL. CRASH. STOP))

To complete the picture, we consider the stabilising unit of the HST in the context of the base station. The base station listens to the SLEEP notification and reacts accordingly:

launch a space shuttle mission to repair – and then restart – the telescope.

BASE = SLEEP. PREPARE. LAUNCH. REPAIR. RESTART. BASE

**Exception handling** The complete specification consists of the STABILISER and the BASE station synchronising on SLEEP. Two events may alter the functioning of the system. If a CRASH occurs, the whole system is extinguished, but if the shuttle mission manages to repair the stabilising unit in time, the whole system will be restarted anew.<sup>6</sup>

HST = trap  $CRASH \rightarrow STOP$   $RESTART \rightarrow HST$  in STABILISER |[SLEEP]| BASE

**Time constraints** Of course, preparing the shuttle mission takes time, and one might wish to incorporate the expected (random) delay in the model. To do so, we can use a constraint-oriented style, as advocated in [20]. This style allows one to add constraints on the timing of certain sequences of interactions, such as between PREPARE and LAUNCH by means of a dedicated operator. For instance,

$$\begin{array}{ll} on & \text{PREPARE} \\ delay & \text{LAUNCH} \\ by & (\nu). \text{ STOF} \\ in & \text{HST} \end{array}$$

adds an exponentially distributed delay with rate  $\nu$  between PREPARE and LAUNCH. Semantically speaking, this will have the same effect as specifying BASE = SLEEP. PREPARE. ( $\nu$ ). LAUNCH. REPAIR. RESTART. BASE, but it is much more modular and flexible, in particular because it can be used to impose very general time constraints, instead of only exponentially distributed ones, see [20]. In short, one can insert an arbitrary (phase-type distributed) delay between PREPARE and LAUNCH, by replacing ( $\nu$ ). STOP in the above expression by some appropriate term (in fact, an encoding of the distribution as a CTMC).

For the sake of the presentation we do not add further time constraints, even though a realistic model would at least impose some nontrivial delay between LAUNCH and REPAIR, (as well as a non-exponential delay to set up the SLEEP mode.)

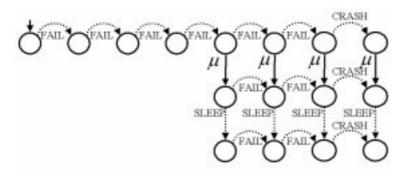

**Extracting the Markov chain** The complete HST specification gives rise to a stochastic model, a CTMC depicted in Figure 10. It is obtained from the specification by applying the formal semantics of the process algebra, and compressing the model by means of an appropriate weak bisimulation afterwards.<sup>7</sup> The states are labelled from left to right with the number of gyros that are currently operational, except if the system is *sleep*ing, or *crashed*.

Remark that in this CTMC the failure rate  $\lambda$  appears weighted with different multiplying factors. The intuitive reason is that if six gyros are operational, the time to the first failure is six times smaller than if only one gyro is left. This increased failure rate for multiple identical components is correctly derived by the formal approach outlined above.

<sup>&</sup>lt;sup>6</sup>The semantics of this exception handling is similar to [16].

<sup>&</sup>lt;sup>7</sup>As explained in [20], constructing the Markov chain requires to hide all possible interactions beforehand. This is necessary but not always sufficient to extract a CTMC, since interactive Markov chains are strictly more expressive than CTMCs (because of the absence on nondeterminism in CTMCs).

Figure 10: A continuous-time Markov chain corresponding to the stochastic behaviour of the telescope

## 4 Performance and reliability via model checking

In this section we illustrate the use of model checking to analyse performance and reliability properties of CTMC models. We discuss the main ingredients of this approach, and apply model checking to the simple Hubble space telescope example of Section 3.

**Temporal logic** The model checking approach relies on the use of temporal logic for specifying properties one is interested in. For this purpose temporal logic provides means to specify undesired (or - dually - desired) evolutions. Typical specifications of properties are 'something undesired never happens' or 'eventually a desired state is reached'. A temporal logic specification is usually considered in the context of a given model (provided by some process algebraic specification, for instance). The mechanic verification whether a model satisfies a temporal logic specification is called *model checking*. It is worth to mention that basic temporal logic does not allow one to reason about delays and time points (although the name might suggest the converse). It is 'temporal' in the sense that it allows one to refer to the ordering of events as the model evolves in time.

Temporal logics for Markov chains In the context of Markov chain models, the temporal logic approach turns into a probabilistic temporal one. It is not sufficient to decide whether 'eventually a desired state is reached'. Instead the probability of eventually reaching a desired state is much more interesting. For the gambler example in Figure 3 the standard interpretation of 'eventually the gambler will be present' would return false, because it is in principle possible to stay absent ad infinitum. However, this evolution is extremely unlikely, it has probability zero. So, a quantitative interpretation of temporal logic is needed, quantifying the likelihood of satisfying a given property. This allows one to specify properties such as 'a desired state is eventually reached with at least probability 0.95'.

Moreover, since the evolution of a Markov chain model in time is measurable (in the true sense of the word), it is possible to reason about time instances within the temporal logic. Timed properties such as 'with at most probability 0.2 the gambler will still be absent after 10 minutes' are possible.

**Continuous stochastic logic** The continuous stochastic logic (CSL), first proposed in [2] and further refined in [4, 3] provides means to reason about continuous-time Markov chain models. It is a branching time logic based on CTL [8] with dedicated means to specify time intervals, and to quantify probability. As explained in Section 2, there are

two substantially different classes of properties of a CTMC: transient and steady-state properties. Therefore, CSL provides two complementary means to quantify the probability mass: a steady-state operator S, to quantify the long-run likelihood, and a transient probability operator  $\mathcal{P}$ .

For instance, a steady-state property  $S_{\leq p}(\Phi)$  is true if the long-run likelihood of property  $\Phi$  is at most p.<sup>8</sup>  $\Phi$  can be a basic property (usually called atomic proposition) valid (or invalid) in some state. It can also be an arbitrary nested property of the logic. The transient probability operator is used to quantify the likelihood of evolving in a specified way, from a given state and a given time point on. For example  $\mathcal{P}_{\leq p}(X \Phi)$  is true in a particular state if the probability of moving (in one step) to a state where  $\Phi$  holds is bounded by p. Apart from  $X \Phi$ , there can be various other arguments for the operator  $\mathcal{P}$ , such as

- $\Diamond \Phi$  quantifies the probability mass evolving in such a way that eventually a state is reached where  $\Phi$  holds (called a  $\Phi$ -state in the sequel).

- $\Diamond^{[0,t]} \Phi$  characterises the amount of probability reaching a  $\Phi$ -state within t time units.

- $\Phi_1 \mathcal{U} \Phi_2$  characterises the amount of probability evolving only along  $\Phi_1$ -states until a  $\Phi_2$ -state is reached.

- $\Phi_1 \mathcal{U}^{[t_1,t_2]} \Phi_2$  quantifies the probability mass evolving only along  $\Phi_1$ -states until a  $\Phi_2$ -state is reached, under the additional constraint that  $\Phi_1$  holds at least up to time  $t_1$ , and  $\Phi_2$  holds at time  $t_2$  the latest.

**Model checking CSL** Model checking a CTMC with respect to a given CSL property involves different algorithms. Since the details are not of vital importance for a proper understanding of the approach – at least relative to the logical means to specify properties – we only give a concise overview of the ingredients.

As in other model checking strategies, a couple of graph algorithms are used. In addition, algorithms to quantify the probability mass of satisfying the above criteria are needed. In principle, these probabilities could be derived using simulation, numerical solution, or sometimes via analytical solutions. Since numerical solution of CTMCs is well studied and generally applicable, it seems wise to use numerical solution methods to model check CSL properties [4]. In this way, model checking involves matrix-vector multiplications (for X), solutions of linear systems of equations (for  $\Diamond$ ,  $\mathcal{U}$  and for  $\mathcal{S}$ ), and solutions of systems of Volterra integral equations (for  $\mathcal{U}^{[...]}$ ). Linear systems of equations can be iteratively solved by standard numerical methods [26]. Systems of integral equations can be solved either by piecewise integration after discretisation, or they can be reduced to standard transient analysis [3]. A prototypical model checker for CSL,  $\mathsf{E} \vdash \mathsf{MC}^2$ , is available [21], We shall make use of  $\mathsf{E} \vdash \mathsf{MC}^2$  to investigate properties of the Hubble space telescope.

**Properties of the telescope model** CSL provides a rich framework to study performance and reliability properties of the HST. Here we consider a few illustrative cases. In order to allow the calculation of numerical values, we first need to fix the model parameters  $\lambda$ ,  $\mu$ , and  $\nu$  of the CTMC in Figure 10. Assuming a basic time unit of one year, we set  $\lambda = 0.1$ , i.e. we assume that each gyro has an average lifetime of 10 years. (Remind that  $1/\lambda$  gives the average duration of an exponential distribution with rate  $\lambda$ .) To turn

<sup>&</sup>lt;sup>8</sup>Instead of ' $\leq$ ' one may use arbitrary comparison operators, or specify intervals of probabilities instead.

on the sleep mode may require a hundredth of a year (a bit more than three days and a half) on the average, whence we set  $\mu = 100$ . Further assuming that preparing the repair mission will take about two months, we set  $\nu = 6$ . Unless otherwise stated we consider the validity of CSL properties in the initial state, i.e. the state labelled 6 in Figure 10. The state labels appearing in this figure serve as atomic state propositions for the logic.

First, let us look into long-run averages. An interesting property, often called *availabil-ity*, is the probability that the system will be available – i.e. neither *crashed* nor *sleeping* – on the long-run average. In CSL we assure an availability higher than p by specifying

$$\mathcal{S}_{>p}(\neg (sleep \lor crash)).$$

None of the states of the HST satisfies this property (whatever the value of p may be). This should not be surprising, because the telescope is not constructed for the long run. In fact, the availability of the telescope is zero, because on the long run, the modelled telescope will crash, all the probability mass will eventually be cumulated in the *crash*-state (cf. Figure 10).<sup>9</sup>

While checking standard availability does not make much sense for the HST, the *instantaneous availability* is of interest. Instantaneous availability is a typical transient property, it is the probability that the system is operational at a given time point t. This time point could for instance be given by the need to observe a rare astronomic event. Assuming that an interesting comet passes the telescope in five years, we specify

$$\mathcal{P}_{>0.95}(\Diamond^{[5,5]}\neg (sleep \lor crash))$$

in order to assure that with at least probability 0.95 the telescope is neither *sleeping* nor *crashed* then. (Note that the time interval [t, t] denotes just a single time point.) This property is satisfied, we compute a probability of more than 0.98.

In the same direction, we may wonder about the probability to obtain blurred data at that time from the telescope, because less than three gyros are operational, but sleep mode is not yet turned on. This is a very unlikely situation, and one might accept at most a probability of  $10^{-6}$ . One way of characterising the relevant states is to isolate those (non-*sleep*) state that (with positive probability) can turn on the *sleep* mode in the next step. This gives us

$$\mathcal{P}_{<10^{-6}}(\Diamond^{[5,5]} (\neg sleep \land \mathcal{P}_{>0}(X \ sleep)),$$

a property that is not satisfied, because the probability of being in the specified states after 5 years is in the dimension of  $10^{-5}$ .

Another quantity of interest is the *time until first sleep*, i.e. the time span before the (fully operational) telescope has to be put into *sleep* mode for the first time. In reality, this happened within 2.7 years: All gyros were operational at the end of the second servicing mission in early 1997, and the *sleep* mode was turned on in November 1999. We specify a less than 10 % chance of such a first sleep within 2.7 years by

$$\mathcal{P}_{<0.1}(\neg sleep \ \mathcal{U}^{[0,2.7]} \ sleep)$$

It turns out that this property is valid,  $\mathsf{E} \vdash \mathsf{MC}^2$  computes that the probability of a first sleep within 2.7 years amounts to about 0.03. A related question is whether it was likely not to witness any gyro failure within the four years between the first (1993) and the second

<sup>&</sup>lt;sup>9</sup>Generally speaking, steady-state properties provide very useful insight in the model, in particular for the widespread class of models where the probability mass can flow forever without gradually leaking into some sink (so to speak), or where more than one sink exists. Each of these sink may in general consist of a set of mutually reachable states.

servicing mission (1997). We answer this question by checking whether the probability to leave the state 6 within 4 years is between, say, 0.3 and 0.7. (Notice that leaving state 6 corresponds to a gyro failure).

$$\mathcal{P}_{[0.3,0,7]}(\Diamond^{[0,4]} \neg 6)$$

In fact, this property is invalid, because the probability of a gyro failure within 4 years is approximately 0.9, thus exceeding the upper bound 0.7.

As a last example property, be reminded that the HST is planned to stay on orbit through 2010. Hence, it seems worth to study whether a *crash* before reaching the year 2010 can hardly be expected. To do so, we model check a property saying that there is at most a 1% chance that the system will *crash* within the next 10 years (given that the system was reset to state 6 in late 1999):

$$\mathcal{P}_{<0.01}(\Diamond^{[0,10]} \ crash).$$

This property is satisfied, the probability of crashing within 10 years is calculated by  $E \vdash MC^2$  to be 0.00036. Be reminded that the model is a toy example, and that its timing parameters are not claimed to reflect reality.

## 5 Concluding remarks

In this paper, we have tried to give an illustrative introduction to the basics of stochastic models, to stochastic modelling using process algebra, and to model checking as a technique to analyse stochastic models.

A few questions have not been addressed to a satisfactory extent. In particular we have negligently skipped the discussion how to label states of a CTMC generated from a process algebra in such a way that these labels can be used in temporal logic property specifications. One solution to this problem is to move from a state based logic towards a transition-based formalism [22].

Another important issue for industrial strength formal analysis is the availability of tool support. At the current state, prototypical tool support is available for both the stochastic modelling and the analysis phase: A couple of prototypes exist that allow a process algebraic modelling of CTMCs [19, 7, 5]. So far, performance models with up to  $10^7$  states have been modelled and analysed compositionally [20]. A prototypical model checker for Markov chains,  $\mathsf{E} \vdash \mathsf{MC}^2$ , is also available [21], it was used to check the above CSL properties of the Hublle space telescope. More effort is nevertheless needed to enhance modelling and analysis convenience. In addition, it seems favourable to link stochastic features to existing modelling and analysis tools with open architecture. We are currently making efforts to incorporate stochastic modelling and analysis features into the CADP toolset [13, 15].

Markov chain models have been the clear focus of this paper. Their memoryless property considerably simplifies both modelling and analysis, but the property also implies that many real-world phenomena can only roughly be approximated with Markov chains. Hence there is a need to extend the framework sketched in this paper beyond Markov models. The work of D'Argenio et al. [11, 12] develops a process algebra, called SPADES, to specify non-Markov performance and reliability models in an elegant way. So, the benefits of a process algebraic formalism extend to performance and reliability modelling in general. Anyhow, the analysis of such models needs further investigations. Since numerical solution methods are impractical in general, we are currently developing an open simulation environment to analyse SPADES specifications. **Acknowledgements** Pedro R. D'Argenio and Joost-Pieter Katoen have provided valuable comments on an earlier version of this paper.

## References

- M. Ajmone Marsan, G. Balbo, G. Conte, S. Donatelli, and G. Franceschinis. *Modelling with Generalized Stochastic Petri Nets*. Wiley, 1995.

- [2] A. Aziz, K. Sanwal, V. Singhal and R. Brayton. Verifying continuous time Markov chains. In *Computer Aided Verification (CAV 96)*, LNCS 1102, pp. 269–276, Springer, 1996.

- [3] C. Baier, B.R. Haverkort, H. Hermanns and J.-P. Katoen. Model checking continuoustime Markov chains by transient analysis. In *Computer Aided Verification (CAV 2000)*, LNCS, Springer, 2000 (to appear).

- [4] C. Baier, J.-P. Katoen and H. Hermanns. Approximate symbolic model checking of continuous-time Markov chains. In *Concurrency Theory (CONCUR 99)*, LNCS 1664, pp. 146–162, Springer, 1999.

- [5] M. Bernardo, W.R. Cleaveland, S.T. Sims, and W.J. Stewart. TwoTowers: A tool integrating function and performance analysis of concurrent systems. In Proc. of IFIP Joint Int. Conf. on Formal Description Techniques and Protocol Specification, Testing and Verification. North Holland (IFIP), 1998.

- [6] T. Bolognesi and E. Brinksma. Introduction to the ISO Specification Language LO-TOS. Computer Networks and ISDN Systems 14:25-59, 1987.

- [7] G. Clark, S. Gilmore, J. Hillston, and N. Thomas. Experiences with the PEPA performance modelling tools. *IEE Proceedings–Software* 146(1):11-19, February 1999.

- [8] E.M. Clarke, E.A. Emerson and A.P. Sistla. Automatic verification of finite-state concurrent systems using temporal logic specifications. ACM Tr. on Progr. Lang. and Sys. 8(2):244-263, 1986.

- [9] E.M. Clarke and R.P. Kurshan. Computer-aided verification. IEEE Spectrum 33(6):61– 67, 1996.

- [10] E.M. Clarke, O. Grumberg and D. Peled. Model Checking. MIT Press, 1999.

- [11] P.R D'Argenio. Algebras and Automata for Timed and Stochastic Systems. PhD-Thesis, University of Twente, November 1999.

- [12] P.R. D'Argenio, J.-P. Katoen E. Brinksma. Specification and Analysis of Soft Real-Time Systems: Quantity and Quality. In *Proc. of the 20th IEEE Real-Time Systems Symposium*, pp. 104-114, Phoenix, Arizona, December 1999. IEEE Computer Society Press.

- [13] J.-C. Fernandez, H. Garavel, A. Kerbrat, R. Mateescu, L. Mounier and M. Sighireanu. CADP (Caesar/Aldébaran Development Package): A protocol validation and verification toolbox. In *Computer Aided Verification (CAV 96)*, LNCS 1102, pp. 437-440, Springer, 1996.

- [14] W.J. Fokkink. Introduction to Process Algebra. Texts in Theoretical Computer Science, Springer, 2000.

- [15] H. Garavel. OPEN/CÆSAR: An open software architecture for verification, simulation, and testing. In B. Steffen, ed, *Tools and Algorithms for the Construction and Analysis* of Systems (TACAS 98), LNCS 1384, pp. 68–84, Springer, 1998.

- [16] H. Garavel and M. Sighireanu. On the Introduction of Exceptions in E-LOTOS. In R. Gotzhein and J. Bredereke, editors, *Formal Description Techniques IX*, pp. 469-484, Chapman and Hall, 1996.

- [17] B. Haverkort. SPN2MGM: Tool support for matrix-geometric stochastic Petri nets. In Proc. of IEEE International Computer Performance and Dependability Symposium, pp. 219–228, Urbana-Champaign, Illinois, September 1996. IEEE Computer Society Press.

- [18] H. Hermanns. Interactive Markov Chains. PhD thesis, Universität Erlangen-Nürnberg, 1998.

- [19] H. Hermanns, U. Herzog, U. Klehmet, V. Mertsiotakis and M. Siegle. Compositional performance modelling with the TIPPTOOL. *Performance Evaluation* 39(1-4):5–35, 2000.

- [20] H. Hermanns and J.P. Katoen. Automated compositional Markov chain generation for a plain-old telephony system. *Science of Computer Programming* 36(1):97–127, 2000.

- [21] H. Hermanns, J.-P. Katoen, J. Meyer-Kayser and M. Siegle. A Markov chain model checker. In Tools and Algorithms for the Construction and Analysis of Systems (TACAS 2000), LNCS 1786, Springer, 2000.

- [22] H. Hermanns, J.-P. Katoen, and J. Meyer-Kayser. Towards model checking stochastic process algebra, 2000 (submitted).

- [23] The Hubble space telescope. http://astro.sau.edu/~astro/html/MARAC/HST.html

- [24] C. Lindemann and R. German. Modeling discrete event systems with state-dependent deterministic service times. Discrete Event Dynamic Systems: Theory and Applications 3:249–270, July 1993.

- [25] Raj Jain. The Art of Computer Systems Performance Analysis. J. Wiley, New York, 1991.

- [26] W.J. Stewart. Introduction to the Numerical Solution of Markov Chains. Princeton Univ. Press, 1994.

## A B Model for Ensuring Soundness of a Large Subset of the Java Card Virtual Machine

#### Antoine Requet

Gemplus Research Laboratory, Av du Pic de Bertagne, 13881 Gémenos cedex BP 100. antoine.requet@gemplus.com

**Abstract**: Java Cards are a new generation of smart cards that use the Java programming language. As smart cards are usually used to supply security to a system, security requirements are very strong and certification can become a competitive advantage. Such a certification to a high Common Criteria or ITSEC level requires the proof of all the security mechanisms. Those security mechanisms include the byte code interpreter and verifier of the virtual machine. Previous works have been done on methodology for proving the soundness of the byte code interpreter and verifier using the B method. It refines an abstract defensive interpreter into a byte code verifier and a byte code interpreter. However, this work had only been tested on a very small subset of the Java Card instruction set. This paper presents a work aiming at verifying the scalability of this previous work. The original instruction subset of about ten instructions has been extended to more than one hundred instructions, and the additional cost of the proof has been managed by modifying the specification in order to group opcodes by properties.

Keywords: B method, Java Card, formal specification

### 1. Introduction

A smart card is a small embedded system generally used to supply security to an information system. Traditionally, the application and the operating system were developed in a secure environment by the card issuer. For few years, platforms (*e.g.*, Java Card, MultOS and Smart Card for Windows) have provided new facilities for application developers. They allow dynamic storage and execution of downloaded executable content. Those platforms are based on a virtual machine both for portability across multiple smart card micro-controllers and for security reasons. Such architecture introduces new risks: the most important one is the possibility to attack the card from an applet by exploiting some implementation faults. In order to avoid such a risk, card manufacturers have a fairly extensive qualification process. Quality insurance requirements for smart cards are very strong. To convince the customer that the system is secure enough, card manufacturers propose to evaluate their system through a certification process.

This certification is a means for the card issuer to promote its products against its competitors. Sometimes the customer or the targeted market requires the certification.

For example, the German market requires each product that uses an electronic signature to be certified at the E4 level of the ITSEC scheme. According to the certification rule and the requested level, the card issuer must provide all the elements needed by the authority to guarantee the quality of the development process. At some high levels, it is required to use formal methods and to provide the proof that security mechanisms satisfy the security policy. One of the trickiest problems is to prove the coherence of the different security mechanisms of the system. Since there are strong size constraints on the chip, the amount of memory is small. This leads Java Card to modify the security scheme. It becomes more crucial to be able to prove the correctness of the whole system security.

After a brief presentation of the Java Card security mechanisms, we sum up the stateof-the art on the formal verification of the Java byte code semantics. We emphasise the proof of the static and dynamic semantics coherence using our approach. Then, we conclude with the extension of our work and its integration in the whole Java Card model.

#### 2. Security of the Java Card

The Java Card 2.1 standard [Sun-99] defines the CAP file (Converted APplet) *i.e.*, the structure of the input files. For each byte code, the standard defines the conditions required for a correct execution, but not the way to ensure that those conditions are met. The Java Card virtual machine is specially designed for smart card; several features have been removed, compared to the Java virtual machine, while others features have been added (*e.g.*, the applet firewall). The Java Card API is a set of tools or services aimed to help programmers designing Java Card applets. Due to the limited resources of the smart card (CPU, memories...), most of the tests (the verifier and part of the loader) must be done statically, outside the card. A secure link mechanism allows the card to check the integrity of the cap file; *i.e.*, after having verified the signature, the card can safely assume that the downloaded program has the required properties, and that a valid verifier has checked it. Of course the certificate can only be provided by a trusted third-party authority.

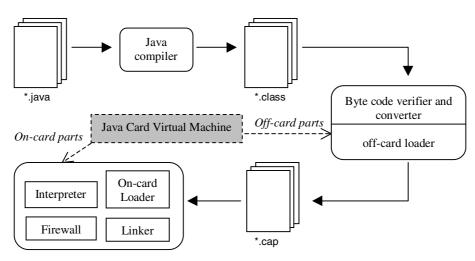

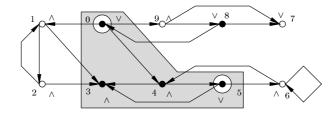

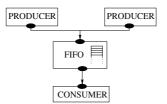

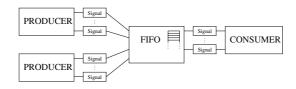

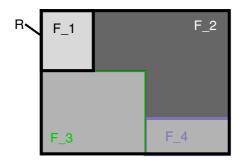

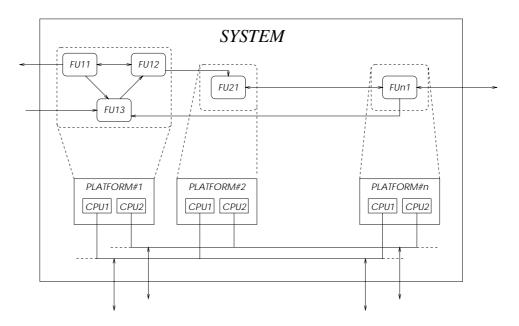

In fact, the security provisions are scattered across different components: a verifier, a converter, an on-card loader, a firewall and an interpreter (see figure 1). Moreover a specific applet is used to manage the applet: the Java Card Runtime Environment (JCRE). It is used to select and deselect applets, and also contain the registers of the selected applets and of the currently active applet.

While the virtual machine insures Java language-level security, the firewall performs additional runtime checks. This mechanism is in charge of the applet isolation and of the control of object accesses. For example, it prevents unauthorized accesses to the fields and the methods of class instances. An applet may share objects with other applets, so the applet firewall must control the access to the shareable interface of these objects. This component is of prime importance for the system security.

Fig.1: Java Card environment

The security policy has to express the correct confinement of the applets and the correct access to shared objects. The respect of the typing rules associated to the access rules of the firewall guarantee this security policy. Thus, we have to verify that the elements performing those checks are correctly implemented and that they are consistent. A formal specification of these mechanisms must be done even if the formal proof is costly. Several elements have already been modelled: the verifier [Cas-99] and partially the JCRE with an emphasis on the firewall [Mot-00]. We present here a method guaranteeing that the security policy is correctly implemented by the different mechanisms.

## 3. Related Work

There has been much work on a formal treatment of Java but no work has been done in order to formally verify whether a given security policy is correctly implemented by a virtual machine. All the works on Java and the Java byte code focus on a formal definition of the semantics. At the Java language level, [Nip-98] and [Sym-97] define a formal semantics for a subset of Java in order to prove the soundness of its type system. [Qia-98] considers a subset of the byte code and aims at proving the runtime correctness from its static typing. Then, he proposes the proof of a verifier that can be deducted from the virtual machine specification.

An interesting work has been done by [Coh-96]. He proposes a formal implementation of a defensive virtual machine. It is possible to prove that his model is equivalent to an offensive interpreter plus a sound byte code verifier. Posegga and Vogt [Pos-98] propose a verification mechanism based on a model checker. They shown the easiness of the proof process using the SMV tool. Goldberg [Gol-97] proposes a formal specification of the byte code verifier for the data flows analysis. His approach is close to the implementation but he simplifies the problem when

neglecting to check subroutines. In the Bali project [Pus-99], Push proves a part of the Java Virtual Machine using the prover Isabelle/HOL. Qian works [Qia-98] gives a specification of the byte code verifier and then proves its correctness.

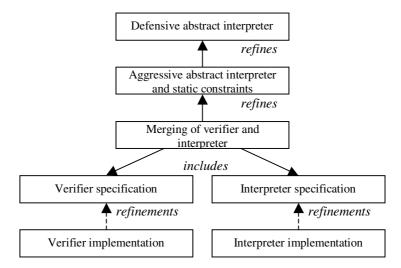

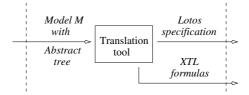

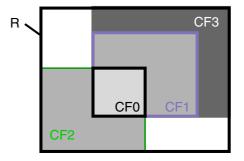

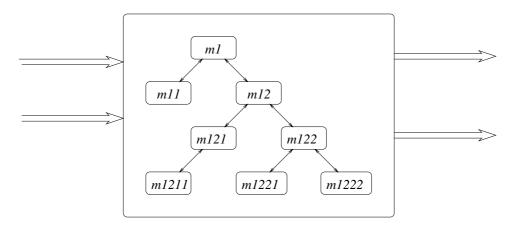

#### 4. The approach used

The main purpose of our approach is to ensure the soundness of the type system. Principles described in [Cas-99] are used to formally specify the Java byte code interpreter. The main idea is to start with a formal description of an abstract defensive byte code interpreter that defines the checks needed to ensure a safe byte code execution. This defensive byte code interpreter defines the expected security policy.

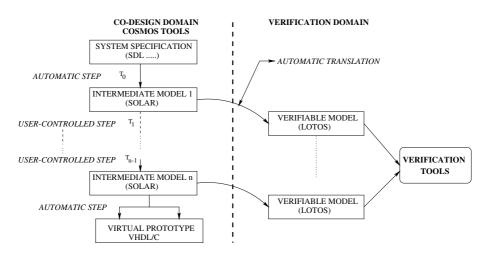

Fig 2: Overview of the approach

The runtime checks performed by the defensive interpreter are removed and converted to static constraints on the byte code during the refinement process. During this process, the proof obligations of the refinement ensure the validity of the static constraints specified.

At the last refinement step, the machine is separated in a byte code verifier, which enforces the static constraints, and an aggressive interpreter, corresponding to the implementation of the Java Card virtual machine. The refinement mechanism ensures that the security policy defined in the abstract interpreter is preserved by the aggressive one.

This approach ensures the soundness of the byte code verifier and the interpreter. That is, the byte code interpreter relies only on tests that are performed. Moreover, from the verifier point of view, this proves that the properties verified are enough to guarantee a safe byte code execution: a property that would not have been verified would generate unprovable proof obligations in the verifier part. Lastly, generating the code for the interpreter and the verifier ensures the correctness of the implementation.

Initially, a small instruction set composed of about ten instructions and a simplified lattice has been used. This approach was adapted to this small instruction set, but extending it to the whole Java Card instruction set did not scale well. More exactly, each instruction needed several manual proofs and both the response time and memory requirement of the prover was too large to completely demonstrate the proofs. The next part focuses on describing how the approach has been extended for a large subset of the Java Card virtual machine.

### 5. Machine considered

#### 5.1. Instruction set

The Java Card subset considered consists of all the stack manipulation instructions, most of the control flow instructions and instructions manipulating local variables.

As the aim of this work was to verify the scalability of the approach, instructions that would drastically increase the complexity of the model have been left out. Especially, those instructions include the instructions used for subroutines, for method calls and for objects handling. The difficulties implied by those instructions have already been widely studied, and there are known solutions for handling them. Moreover, those difficulties usually involve few instructions, and are not subject to scalability problems. The handling of exceptions and subroutines will be added later, when the scalability of the model will be resolved. We will use a model developed as an extension of [Lan-98] based on [Aba-98] and very close to [Fre-99].

So, the chosen instruction set is neither representative of the full Java Card instruction set nor representative of the tricky parts of the full instruction set. However, it appears as a valid choice to study the problems that can be encountered when extending a ten instructions subset to the full instruction set.

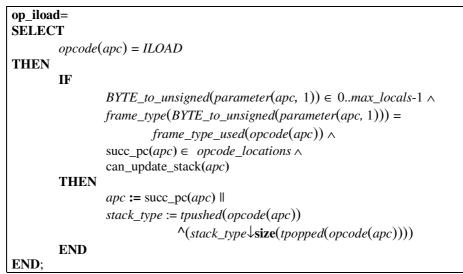

A subset of instructions manipulating the stack is created. Each of those instructions is considered as first removing elements from the stack, and adding new elements to the resulting stack. For example, the instruction *iadd*, which adds the two topmost elements of the stack together, and replaces them by the result, is considered as being an instruction that pops two integers from the stack and pushes an integer.

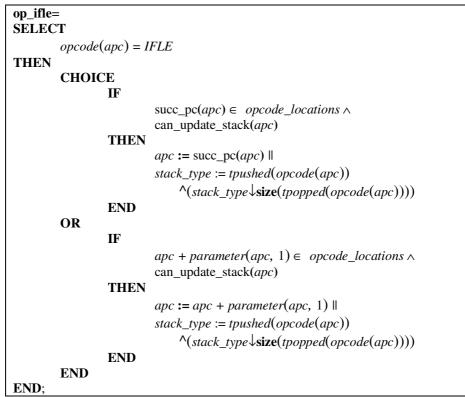

To model this, two constants have been added: *tpushed* and *tpopped*. Those constants are defined as partial maps from opcodes to sequence of types. *tpopped* defines the types that are expected to be removed from the top of the stack, and *tpushed* defines the types to be pushed onto the stack when the instruction is executed. In the previous example, *tpushed(iadd)* is equal to the one element sequence [integer], and *tpopped(iadd)* is equal to the sequence [integer].

In order to simplify the specification and the proof process, the opcodes are grouped by properties. Sets are defined to contain opcodes with similar properties. For example, the following sets are used:

- *OP\_NEXT*. This set contains opcodes that can go to the next instruction after execution. This include nearly all the instruction, excepted the unconditional jumps.

- *OP\_BRANCH* and *OP\_BRANCH\_W*: the set of opcodes that may perform a relative branch, where the target is defined by the first parameter. There are two sets, since the branch can be defined by a signed byte parameter (*OP\_BRANCH*) or a signed short parameter (*OP\_BRANCH\_W*)

- *OP\_NEXT\_FRAME\_READ*: the set of opcodes reading a value from the local variables.

A given opcode can be part of several sets. For example, instructions that perform conditional branch are both elements of *OP\_NEXT* and *OP\_BRANCH*. Although every Java Card opcodes can not fit in a group, such a grouping scheme highly simplifies the specification.

One drawback is that grouping opcodes by properties generates more complicated proof obligations that require increased manual interaction. However, those proof obligations are more generic and can usually be used to discharge nearly all the proof obligations corresponding to the opcodes within the group.

#### 5.2. State of the machine

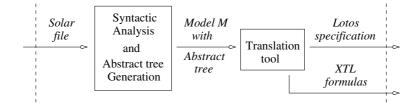

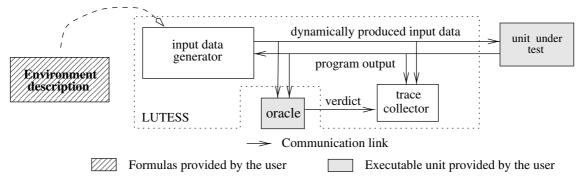

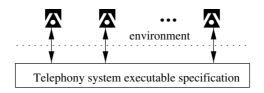

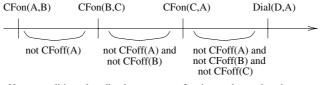

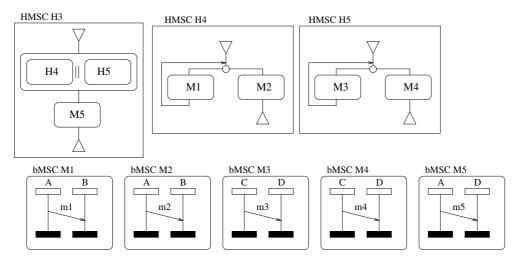

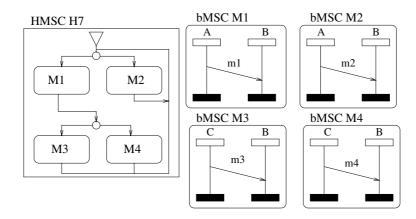

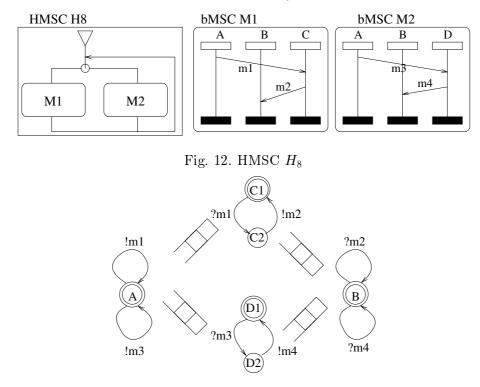

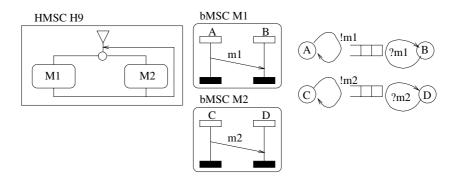

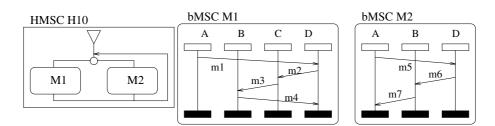

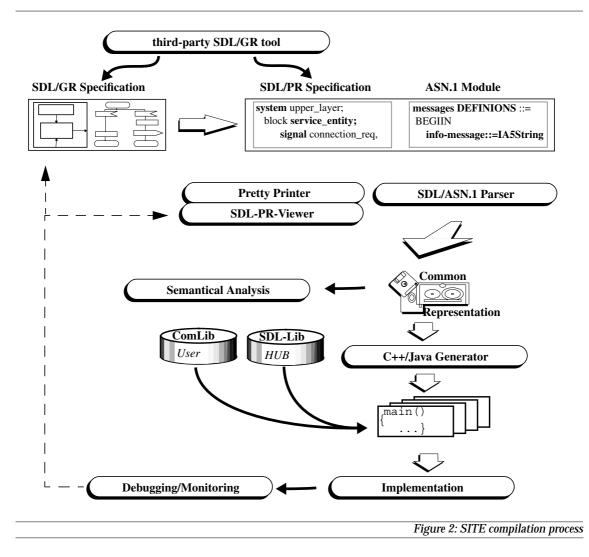

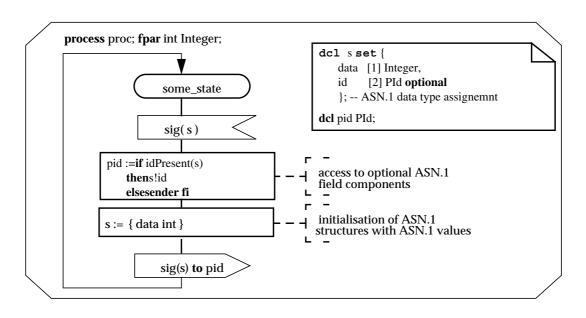

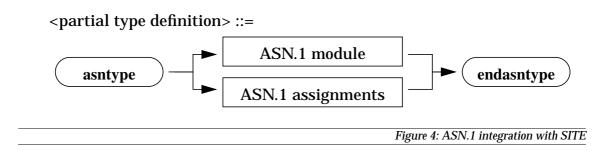

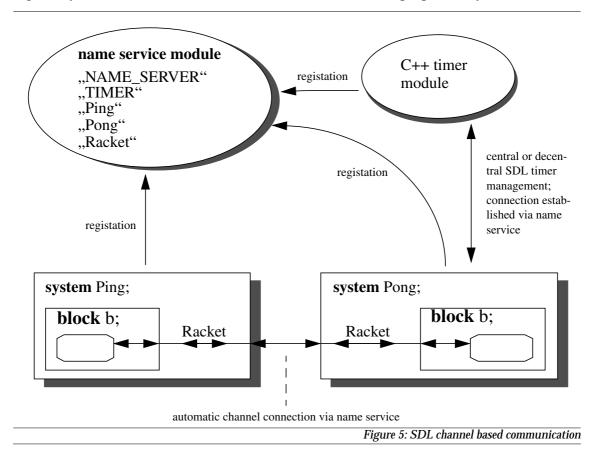

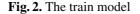

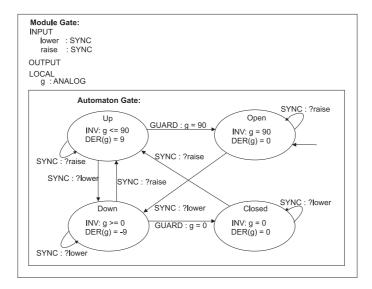

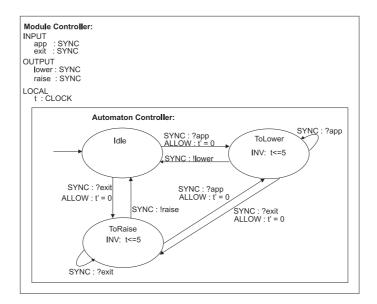

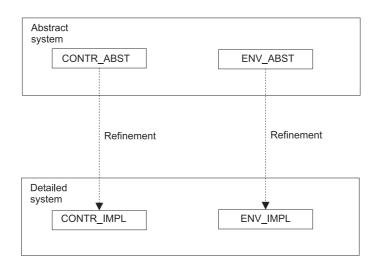

We consider the execution of one method. This is enough to verify the consistency between the interpreter and the verifier. Thus the verification can be performed a method at a time, provided that some information about the global context is accessible.