# Process and design optimization of SiC MOSFET for low on-state resistance

Tomasz Sledziewski, Tobias Erlbacher, Anton Bauer

Fraunhofer Institute for Integrated Systems and Device Technology IISB

#### Europe-Korea Conference on Science and Technology, EKC 2019

Slide 1

# Fraunhofer Society and Fraunhofer IISB

#### Fraunhofer Society

- Europe's largest application-oriented research organization

- Research according to the needs of the market

#### Fraunhofer IISB

- Leading SiC and power electronics institute

- Founded in 1985

- Located in Erlangen, Bavaria, Germany's hot spot for SiC and power electronics

- Close cooperation with FAU Erlangen-Nuremberg

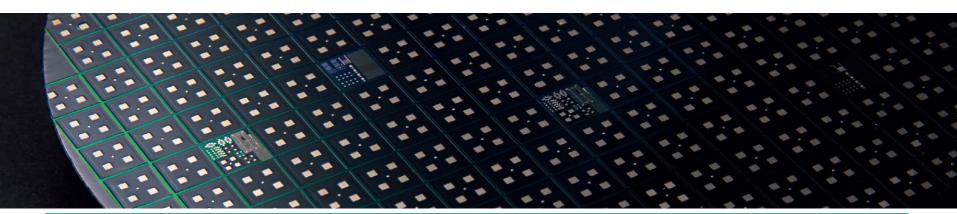

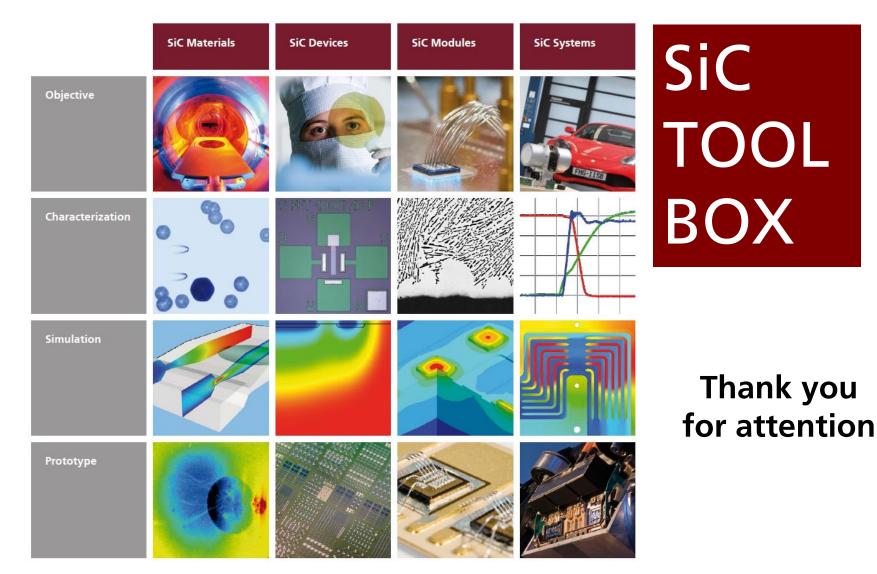

# SiC prototypes and solutions

- Materials

- Devices

- Packaging and reliability

- Modules and systems

Slide 3

### **Properties of silicon carbide**

Why SiC for power semiconductor devices?

| Parameter                 | Si              | 4H-SiC           | Benefit from SiC           |

|---------------------------|-----------------|------------------|----------------------------|

| E <sub>g</sub> (eV)       | 1.12            | 3.26             | high-temperature operation |

| E <sub>crit</sub> (MV/cm) | 0.3             | 3                | low on-state resistance    |

| к (W/cm/°C)               | 1.5             | 4.9              | excellent heat dissipation |

| v <sub>sat</sub> (cm/s)   | $1 \times 10^7$ | $2.7 	imes 10^7$ | high switching frequency   |

Slide 4

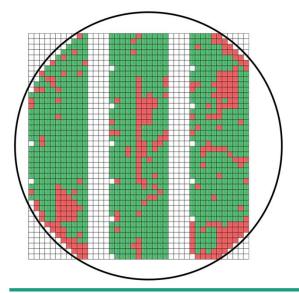

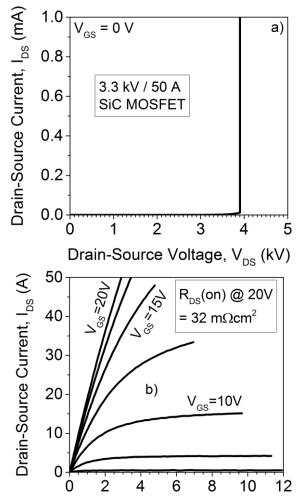

# SiC Power MOSFET at Fraunhofer IISB

- Blocking voltage: 600 V 3300 V

- Threshold voltage: 2 V 3 V

- On-state resistance:

- 10 mΩ cm<sup>2</sup> for 1.2 kV devices

- 32 mΩ cm<sup>2</sup> for 3.3 kV devices

- Yield: 80% for 4 mm<sup>2</sup> chips

working chip failure

Yield map for 1.2 kV SiC Power MOSFET, chip size = 4 mm<sup>2</sup>

Drain-Source Voltage,  $V_{DS}$  (V)

Blocking and forward characteristics for 3.3 kV SiC Power MOSFET fabricated at Fraunhofer IISB

Group Devices & Reliability, 17.07.19 © Fraunhofer IISB

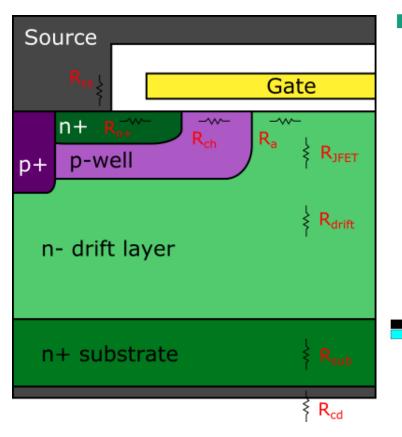

# SiC Power MOSFET resistance

Different components of on-state resistance

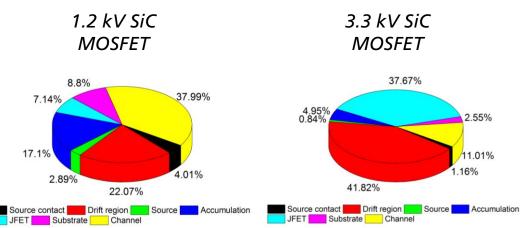

Contribution of different components to total R<sub>DS</sub>(on) depends on cell design and blocking voltage

Analytical simulation of resistance of SiC Power MOSFET with 3 μm JFET, 1 μm channel, 13 μm cell pitch

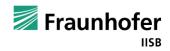

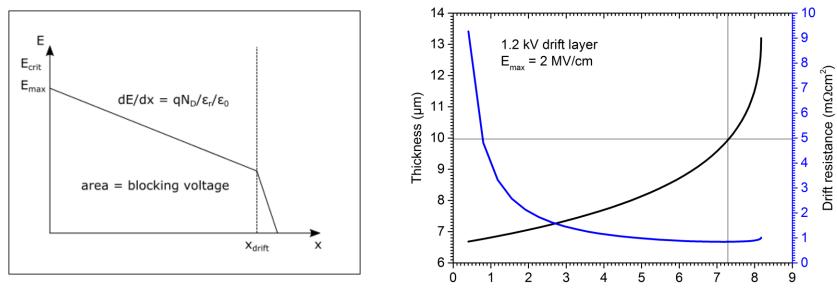

## **Resistance: drift layer**

| Voltage                              | 650 V | 1200 V | 1700 V | 3300 V |

|--------------------------------------|-------|--------|--------|--------|

| Contribution to R <sub>DS</sub> (on) | 10.8% | 22.1%  | 31.9%  | 41.8%  |

Optimization task: find drift layer doping and thickness at minimum resistance

Too high doping and / or too small thickness

#### → increase of electric field

→ increase of drain-source leakage current

Doping (10<sup>15</sup> cm<sup>-3</sup>)

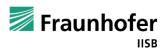

### **Resistance: channel**

| Voltage                              | 650 V | 1200 V | 1700 V | 3300 V |

|--------------------------------------|-------|--------|--------|--------|

| Contribution to R <sub>DS</sub> (on) | 45.9% | 38.0%  | 30.9%  | 11.0%  |

High density of states at SiO<sub>2</sub> / SiC interface  $\rightarrow$  low mobility  $\rightarrow$  high channel resistance

- Sophisticated gate oxides (NO annealing)

- $\rightarrow$  passivation of interface states and increase of electron mobility

→ shift of flatband (threshold) voltage

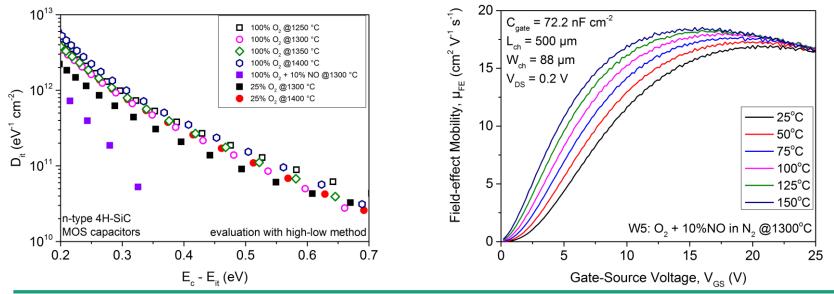

### **Resistance: JFET**

| Voltage                              | 650 V | 1200 V | 1700 V | 3300 V |

|--------------------------------------|-------|--------|--------|--------|

| Contribution to R <sub>DS</sub> (on) | 3.8%  | 7.1%   | 10.6%  | 37.7%  |

JFET implantation used to reduce extension of the space charge region in the JFET region

- $\rightarrow$  decrease of JFET resistance

- $\rightarrow$  possible increase of electric field in gate oxide

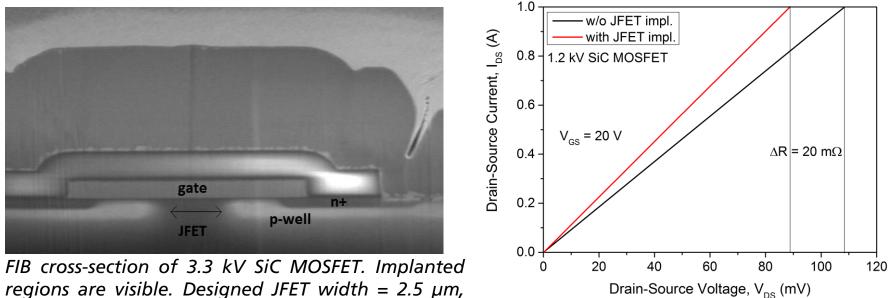

#### **Resistance:** substrate

| Voltage                              | 650 V | 1200 V | 1700 V | 3300 V |

|--------------------------------------|-------|--------|--------|--------|

| Contribution to R <sub>DS</sub> (on) | 10.6% | 8.8%   | 7.2%   | 2.6%   |

Forward characteristics of 6 A / 650 V SiC JBS diodes with and without substrate thinning

- $\rightarrow$  decrease of substrate resistance

- → more challenging handling and processing of thin wafers

## **Resistance: cell design**

|                                                                          | Cell design                                                                                  |                                                           |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Stripe                                                                   | Square                                                                                       | Hexagon                                                   |

| 1                                                                        | 1.36                                                                                         | 1.34                                                      |

| 1                                                                        | 1.73                                                                                         | 1.74                                                      |

| 1                                                                        | 0.46                                                                                         | 0.45                                                      |

| 45 - J SC                                                                |                                                                                              | $\Delta = 31 \text{ m}\Omega$                             |

| Drain-Source CL<br>Drain-Source CL<br>Drain-Source CL<br>Drain-Source CL | 1.7 kV SIC MOSEE                                                                             | 27%<br>Iower R <sub>DS</sub> (on)<br>for<br>square design |

| 0 <del>]</del><br>0 1                                                    | 2 3 4 5                                                                                      | 6 7 8                                                     |

| -                                                                        | 1<br>1<br>1<br>1<br>1<br>50<br>45<br>40<br>35<br>50<br>40<br>35<br>50<br>20<br>15<br>10<br>5 | Stripe Square   1 1.36   1 1.73   1 0.46                  |

### Summary

Low on-state resistance of SiC Power MOSFET achievable by design and / or process optimization

Dominant components of total on-state resistance dependent on the device blocking voltage

Very low on-state resistance usually paid with lower reliability

Group Devices & Reliability, 17.07.19 © Fraunhofer IISB

Part of this research was supported by GRDC Program through the National Research Foundation (NRF) funded by the MSIT of Korea (NRF-2017K1A4A3013716).