Fraunhofer Institut Mikroelektronische Schaltungen und Systeme

# Annual Report 2003

Annual Report of the Fraunhofer-Institut für Mikroelektronische Schaltungen und Systeme IMS Duisburg 2003

### Preface

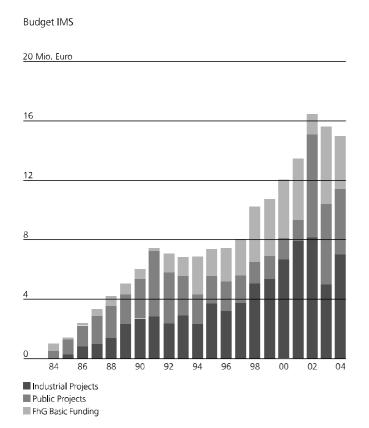

During 2003, the 19<sup>th</sup> year of existence of IMS, application industry still had been very cautious with investment in innovative developments. This showed some influence in the quantitative development of our institute this year.

We managed to reach an annual turnover of more than 15 million Euros, the industrial revenues reached about 32 %. The volume of CMOS production could be stabilized at nearly last year's level.

Consequently, we did not augment our staff in these days, but concentrated in training our collaborators the most efficient way by intensive practice.

The good cooperation with "Fraunhofer Institute of Photonic Microsystems (IPMS)" in Dresden in the fields of ASIC production, test and mask fabrication turned out to remain an important factor of our concept. The detailed knowledge of each other and confidence has grown over the last 12 years, so the relation is very close and trustworthy.

The planning of the fourth section of our institute building had been completed during this year, we hope that the construction work will start in spring 2004.

In 2003 the biggest annual investment in our history was placed in our CMOS line for state of the art equipment. It was quite a challenge for our team, besides the continuous production in the existing CMOS line, to install the new equipment and bring it into operation. During the first half of 2004 we will switch from 6" to 8" wafers and start implementing an additional process with 0.25 µm structural width. So, beginning in the second half of the year, our customers will profit from the more rational way of our production and the smaller structural size of our process. The bigger throughput will help customers with increasing midsize volume requirements to be served in shorter terms.

In June 2003 our Smart Home "InHaus" was completed by the ceremonial opening of our Smart Garden with automated maintenance functionality. In November 2003 the periodical "InHaus-Forum" took place with participation of leading international companies in that field, and local and regional public authorities. Main topic this year was the combined marketing of new products and services by the partners.

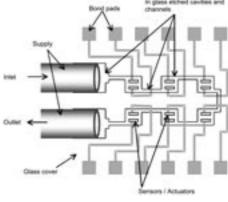

Taking chance of our close neighbourhood to Dutch partners, we succeeded starting a EUREGIO-Project concerning "micro reactors" in autumn 2003.

In these days, the continuous confidence of our customers, business partners and public authorities is even more important for us, than in other years in the past. So we thank them, and also all our employees for their contributions to our work. Our future success will depend on their further R&D work in the fields of Microelectronics, Sensors, Wireless Chips and Systems.

Time

Günter Zimmer (Director of IMS)

# Contents

| Development of the IMS                                                                               | 7  |

|------------------------------------------------------------------------------------------------------|----|

| Selected Projects of the Year 2003                                                                   | 11 |

| I CMOS Devices and Technology                                                                        |    |

| Production of Customer ICs at IMS<br>H. Vogt, U. Paschen                                             | 12 |

| Active Defect Reduction Program at IMS<br>S. Linnenberg, J. Peter-Weidemann, B. Heinicke, U. Paschen | 14 |

| II Silicon Sensors and Microsystems                                                                  |    |

| Turn-key Assembly of Integrated Pressure Sensors<br>O. Köster, H. K. Trieu                           | 16 |

| CMOS-Based Detectors for Optical Communications and Mass Storage<br>I. Hehemann, A. Kemna            | 19 |

| Dependable Sensor Systems<br>D. Weiler                                                               | 22 |

| III CMOS Image Sensors                                                                               |    |

| CMOS Line Image Sensors in the FhG-IMS<br>A. Kemna, W. Brockherde                                    | 26 |

| Automotive CMOS Camera<br>W. Brockherde, C. Nitta                                                    | 29 |

| IV CMOS Circuits                                                                                     |    |

| Embedded Microcontroller Applications<br>H. Kappert, R. Lerch, N. Kordas                             | 31 |

| Digital Sinc-Filter for High Order Sigma-Delta-Modulators<br>M. Gnade, A. Kemna                      | 34 |

# Contents

| Cascaded Sigma-Delta-Modulators of Higher Order<br>Without Stability Problems<br>D. Weiler     | 36 |

|------------------------------------------------------------------------------------------------|----|

| V Wireless Chips and Telecommunication Systems                                                 |    |

| Rapid Prototyping for Wireless System-on-Chip Solutions<br>M. Marx, HC. Müller, R. Kokozinski  | 39 |

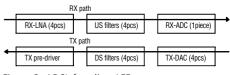

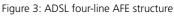

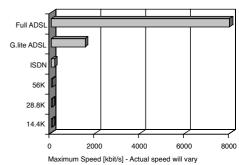

| Low power four channel Central Office ADSL Solution<br>M. Bresch, R. Kokozinski                | 42 |

| CMOS IP for Short Range Wireless Communication Systemes<br>N. Christoffers, R. Kokozinski      | 46 |

| VI Systems and Applications                                                                    |    |

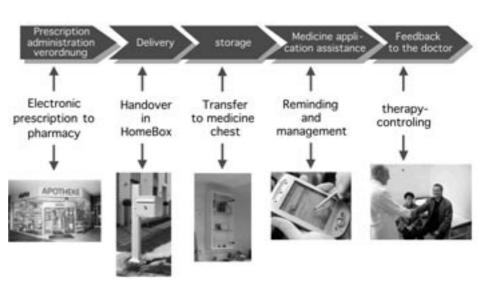

| Smart Label based Medicine Management<br>G. vom Bögel, M. Hedtke, K. Scherer                   | 50 |

| The use of Smart Labels in the Supply Chain for Clothing<br>G. vom Bögel, M. Hedtke, M. Németh | 52 |

| List of Projects IMS                                                                           | 55 |

| List of Publications and Scientific Theses 2003                                                | 61 |

| Board Memberships for Associations and Authorities 2003                                        | 71 |

| Chronicle                                                                                      | 75 |

| Press Review                                                                                   | 79 |

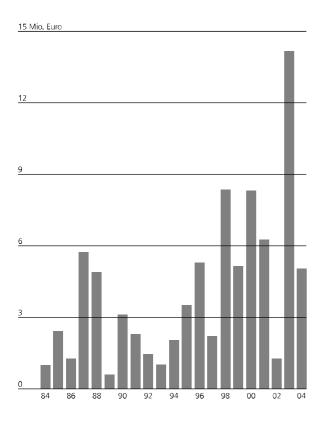

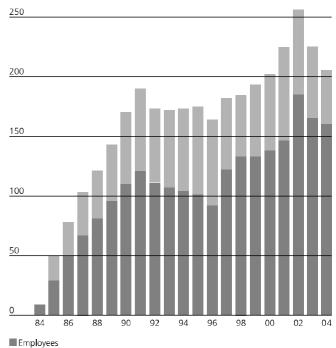

Development of the IMS

# Development of the IMS

#### Capital Investments IMS

#### Staff Members IMS

Scientific Assistants

Selected Projects of the Year 2003

# Production of Customer ICs at IMS

H. Vogt, U. Paschen

#### Introduction

IMS offers a broad spectrum of services in the field of microelectronics and micro electromechanical systems (MEMS). With several design departments the development of application specific integrated circuits (ASICs) can be realised according to the customer needs. In addition IMS also has the capability to fabricate these circuits with several advanced CMOS processes with volumes ranging from small numbers for prototypes up to medium volume production numbers.

#### Fabrication

IMS currently runs a fabrication line for wafers with a diameter of 150 mm. Recently, the cleanroom was expanded to about 1000 m<sup>2</sup> (see Figure 1), providing space for new equipment that increases the capacities both for production and technological R&D activities.

The basis of the IMS fabrication activities are CMOS processes, currently with a minimal structure size of 0,5 micron. Several process options and add-ons have been developed in order to increase the versatility of the IMS products. For example the processes offer options for special devices like high voltage transistors for interfacing with an electrical harsh environment. Also available are voltage independent capacitors and high resistance polysilicon enabling the realisation of analog and mixed signal circuits (that is the combination of analog and digital functionality on one chip), for example for highly demanding sensor signal processing. Another strong focus is the fabrication of optical sensors based on CMOS technology, e.g. high speed camera chips or camera chips with an extremely large sensitivity range. A further strength of IMS is an

integrated pressure sensor, which can be fabricated together with CMOS circuitry in one process. Thus, the sensor can directly be integrated on one chip together with versatile electronics. This offers the possibility to realize complete sensor systems with extremely small size, including signal conditioning and communication electronics.

Typical applications of chips designed and fabricated at IMS cover a very broad spectrum, ranging from consumer products to highly demanding industrial fields.

Product examples are optical sensor ICs, smart labels for several applications, smart power ICs that combine "intelligent" logic functions with high power capability and integrated pressure sensors for medical, industrial and automotive applications as well as circuits with very specialised functionalities for specific customer applications.

Production volumes range from very few chips (MPC service) for the realisation of first prototype systems to small and medium volume fabrication. This flexibility makes IMS especially attractive for small and medium enterprises.

IMS has also upgraded its packaging capabilities. In order to offer the full production chain from silicon to packaged IC or module an automated packaging line for ceramic substrates or PCBs has been installed.

#### Outlook

In 2004 the IMS production line will be upgraded for the fabrication with 200 mm wafers, which will be a significant increase in production and R&D capacity. The larger usable area per wafer alone accounts for an increase of about 80 %. Due to the new equipment several bottlenecks that limit wafer throughput today will be eliminated. Therefore, not only the wafersize increases but also the wafer fabrication capacity per year increases as well.

In addition to the upgrade to 200 mm wafers we will also install an industrial quarter micron CMOS process. This offers the possibility to realize very high density digital cores that together with analog functionality build the basis of intelligent analog systems and enables for example very small transponders or improved optical sensors. Also the application of advanced equipment with a minimum structure size of 250 nm offers new and exciting possibilities for new devices, for example very low resistance and highly robust power devices. Thus, this extension of IMS capabilities to smaller structure sizes together with increased production volume will secure and broaden the position of IMS as a developer and supplier of advanced products in the field of microelectronic circuits and systems.

Figure 1: Part of the cleanroom facilities at IMS

## Active Defect Reduction Program at IMS

S. Linnenberg, J. Peter-Weidemann, B. Heinicke, U. Paschen

#### Introduction

In order to solve yield problems due to defects and to continuously increase the circuit yield, it is necessary to know the exact nature and cause of the defects. For this reason a stringent monitoring of defect occurrence is indispensable for all the critical process steps. At IMS an active defect reduction program is carried out for continuous yield improvement. While small defect levels and the highest possible yield are an important issue in any IC fabrication, extremely low defect densities are a mandatory requirement for very large chips like for example optical image sensors with chip areas of the order of square centimetres and more (figure 1). Most of the optical image sensors at IMS are manufactured in a 0,5 µm CMOS technology with 3 metal layers. For the planarisation of the intermetal oxides a CMP process is used. The contacts and vias are realized by tungsten plugs (tungsten deposition and backetch). Because the small structure size and the large areas of image sensors put the highest demands on technology they are used here as an example, even though similar measures are carried out for other circuits and processes.

Figure 1: Example of a CMOS image sensor with 168 mm<sup>2</sup> chip area and 1025 by 1024 pixel

#### Active Defect Monitoring

In order to ensure a stable and high quality IC production in the IMS fabrication line, regular machine dependent particle generation tests are carried out. This keeps the overall defect level small. Beside these general machine dependent defects there is also a possibility of process dependent or even product dependent defects. In order to keep their level as low as possible a more exact investigation and active defect monitoring is employed. For the automatic defect identification a WF-720 wafer inspection system from Orbot Instruments is used. This system works with Perspective Darkfield Imaging (PDI™) combined with pixelby-pixel die-to-die comparison. The data obtained with this instrument are the basis for all further investigations and measures.

The defect coordinates are subsequently transferred to an inspection microscope INS 3000 from LEICA Microsystems whereby the defects can be analysed in detail. Thus, each defect can be classified and pictures of the defects can be stored for further reference. For a more detailed investigation the defects can also be analysed in a Scanning Electron Microscope S-7800 H from HITACHI.

This defect monitoring is performed on all critical levels of the front end and back end fabrication of the 0,5 µm CMOS process (active area, poly level, tungsten levels, metal levels). The defect inspection system is capable to automatically recognize already observed defects of deeper levels, thus, simplifying the evaluation of the data significantly.

Some defects, like scratches due to handling problems of a machine, are easily identified and easily attributed to the critical process step. In other cases only a very thorough investigation can reveal the nature and the origin of the defects.

As an example figure 2 shows a defect in the metal level, which could be a cause for circuit failure if located between two metal lines with minimum distance.

The acquired defect data can be evaluated statistically with the program <sup>®</sup>YIELD Manager from EGsoft, which allows for a versatile analysis, with respect to defect class, defect size and spatial distribution. The analysis of the data revealed that a small number of process steps is responsible for most of the defects. Most of these defects are of very small size (approximately  $1 \mu m^2$ ) but this is still large enough to make then a potential source of electrical failures in submicron technologies.

Since each defect is stored with defect position, observation-level, defect type and defect size, it is possible to compare the results of the electrical circuit test of the image sensors with the defect monitoring data. Thus, specific pixel, line or column failures can be directly attributed to individual defects. Additional methods like liquid crystal measurements can also be employed to localise the position where the malfunction occurs. This comparison of the electrical circuit test data with the defect monitoring data is an important step of the active defect monitoring.

Taking all these information into account the critical process steps can be identified and subsequently be optimised, thus ensuring a continuous improvement of yield and quality.

#### **Discussion and Conclusions**

With the help of specialised automated defect inspection tools and a continuous program to identify critical process steps and optimise them even very demanding circuits with submicron structure size and very large chip areas can be fabricated with high quality and yield.

Figure 2: Example of a defect in the metal level

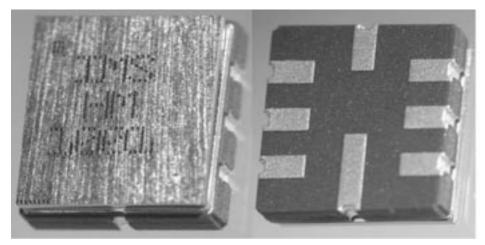

# Turn-key Assembly of Integrated Pressure Sensors

O. Köster, H. K. Trieu

#### 1. Introduction

The continuing demand for sensor products with higher performance, light weight and small dimensions is requiring levels of package performance of microelectromechanical devices that were not attainable by the molded plastic and ceramic packages of the past decade. Portable devices and cost effectiveness are strong drivers of packaging technologies for sensor products. Pressure sensor systems with minor temperature drift and small form factor, i. e. calibrated pressure sensors within miniaturized housings, will play a major role. For example altimeters and barometers are already incorporated in clocks and pocket knives [1; 2]. In order to provide its customers with a turn-key solution, FhG-IMS Duisburg has built a fabrication line for test,

calibration and assembly of integrated pressure sensors. The chosen housings are CLCC8 with the outer dimensions of  $5 \times 5 \times 1.7$  mm<sup>3</sup>.

# 2. Wafer level Calibration of integrated Pressure Sensors

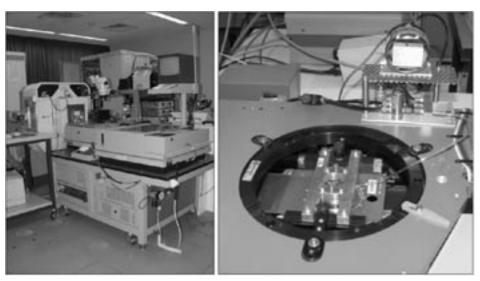

IMS has set up a method for wafer level calibration of integrated surface micromachined absolute pressure sensors in the low pressure range [3 - 6]. The necessary equipment for sensor calibration has been added to a standard test arrangement for microelectronic circuit testing consisting of an automatic waferprober EG2010 from Electroglass Corportion, USA, and a test system M3610 from SZ Testsysteme AG, Amerang, Germany (figure 1). The waferprober is connected to the serial interface of the workstation of the test system. Thus, the pressure sensor calibration is performed at the same time as the circuit test. In order to apply different pressures to the chips the conventional probe card has been modified to get a miniaturized pressure chamber (figure 2).

The wafer level pressure sensor calibration is performed at discrete temperatures and at three different applied pressures at each applied temperature. The chamber pressure is switched rapidly via valves. The chamber pressure is measured by means of a calibrated reference pressure gauge. All data from the test runs are stored in a data file. Finally the calibration coefficients are calculated and then directly stored within the integrated EEPROM of the pressure sensor. At the same time calibration coefficients for an integrated temperature sensor may also be calculated and stored. Then the bad dice will be marked with an ink dot and the wafer is subsequently forwarded to the assembly line.

Figure 1: Wafer level calibration system

#### 3. Chip Assembly

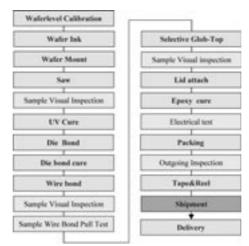

Figure 3 depicts the assembly process flow. The whole assembly line is set up for cassette-to-cassette operation. Each cassette contains 20 Auer-Boats, whereas each Auer-Boat takes up 42 pressure sensors. Die bonding and lid attach is performed at a fully automated standard Die Bonder ESEC 2007. Wire bonding is performed at a fully automated standard Ball-Wedge Wire Bonder ESEC 3088. In figure 4 an X-ray microphotograph of a bonded pressure sensor in a CLCC8 housing is shown. The final functional test and subsequently the packaging within "Tape&Reel" is performed by a custom specific machine from Fritsch GmbH. Figure 5 depicts the top and rear side view of a barometric sensor. The pressure conveyance is realized from the side walls. To our knowledge this integrated pressure sensor has got the smallest dimensions all over the world.

#### 4. Summary

The presented approach for an wafer level calibration of micromachined pressure sensors has already achieved high accuracy. In addition, the outlined test system may as well be used for wafer level quality control of pressure sensors and pre-selection prior to assembly. The assembly line is currently in the ramp-up phase. The equipment was chosen for a planned throughput of several million sensors per year.

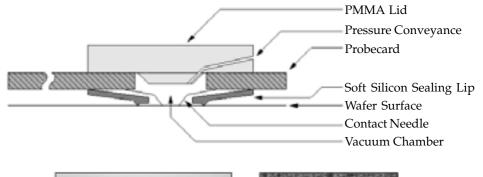

Figure 2: Sketch of modified probe card

Figure 3: Summarized assembly processflow

Figure 4: X-ray microphotograph of a bonded pressure sensor

Figure 5: Ultra small packaged integrated pressure sensor

#### 5. References

- [1] www.suuntousa.com/products.htm, side visited 03.02.03

- [2] Victorinox-Höhenmesser 1.3705.AT, www.victorinox.com/newsite/de/ produkte/index.htm, side visited 03.02.03.

- [3] O. Köster et al., "On-wafer calibration for pressure sensors", Annual Report of the Fraunhofer-Institute of Microelectronic Circuits and Systems 2001, 25

- [4] Method and Device for Testing or Calibrating a Pressure Sensor on a Wafer, Patent WO 02/101348 A1, published 19.12.02 (owner: FHG-IMS)

- [5] D. Brögger, Diploma Thesis; FH Düsseldorf, Germany 12/00

- [6] O. Köster et al., "Kalibrierung von integrierten Drucksensoren im Waferverbund", tm – Technisches Messen 05/2003, 265

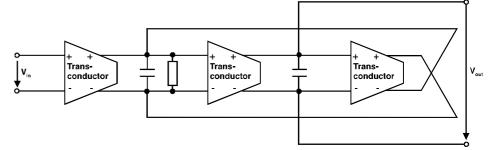

# CMOS-Based Detectors for Optical Communications and Mass Storage

I. Hehemann, A. Kemna

#### Introduction

Today the area of mass storage and optical communications represents a high volume market with increasing potential for the future. In 2002, for example, 31.5 Mio. DVD players were sold worldwide, and, considering the increasing storage needs and upcoming products, higher sales figures are predicted for the next years. Furthermore, although there is a trend towards systems on chip, a steady growth of the data transfer on board level and the short-haul can be observed. Due to the limited data rate of wire line transmission systems, caused by crosstalk phenomena, reflections, and the damping behaviour, this type of communication will be performed optically in the future. At latest with the use of optical communication systems within PC systems, an enormous increase of this market will occur.

Although the CMOS technology is the technology of choice for commercial products, the vast majority of photo detectors for both applications is based on BiCMOS-, III/V, or hybrid technologies. This is due to the fact that early systems were based on light of the infrared spectrum which is difficult to detect with CMOS based sensors. However, in the field of optical storage as well as in the short-haul optical communication the tendency goes towards shorter wavelengths of the visible spectrum. In the first case this trend is pushed by the inherent increase of the storage capacity, in the latter case by the availability of low cost light sources and the fact that for short distances the damping behaviour of fibres is negligible [1, 2]. Since light of the wavelength region from 400 nm to 800 nm can be detected with CMOSbased detectors, the use of that technology is desirable for the implementation of low cost components.

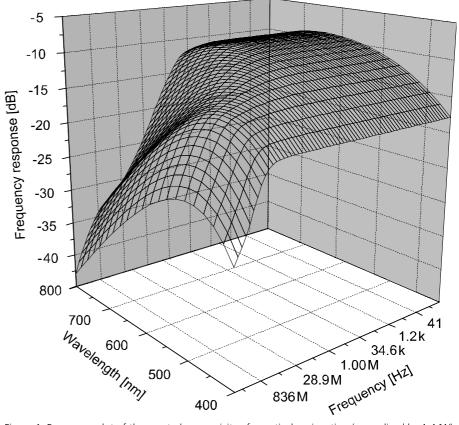

# Photodiodes for the visible light spectrum

Up to now, integrated optical detectors have mainly been used for applications where the input signal bandwidth is in the kilohertz range, e. g. imagers or x-ray detectors. Due to this, the frequency behaviour of CMOS photodiodes could generally be neglected. With the applications aimed at here, signal bandwidths of some hundred Megahertz have to be processed so that the photodiode bandwidth plays a significant role.

For the investigation of the behaviour of photodiodes device simulations as well as analytical calculations that allow

Figure 1: Frequency plot of the spectral responsivity of a vertical pn-junction (normalized by 1 A/W).

to evaluate the influence of different process parameters are used. Figure 1 shows the calculated frequency behaviour of the spectral responsivity in dependence of the stimulating wavelength of a vertical pn-junction. Due to the different penetration depth of the radiation into silicon at different wavelengths, the contribution of drifting and diffusing charges to the overall photocurrent varies. This causes a heavy dependence of the bandwidth on the wavelength yielding values from several Megahertz for the near infrared going up to almost one Gigahertz for the near ultraviolet.

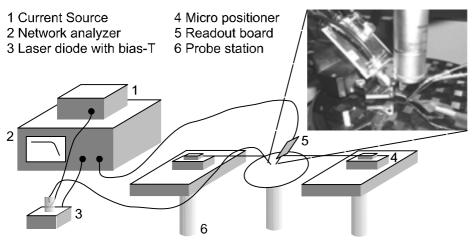

For the characterization of test structures a hybrid measurement method has been developed (see Figure 2). To process the photocurrent a discrete transimpedance amplifier with sufficient bandwidth is contacted to the wafer using microwave probes, the stimulation is done employing fibre coupled laser diodes with wavelengths relevant for optical storage systems, namely 785 nm (CD-ROM), 670 nm (DVD), 405 nm (Blu-ray). Measurements

Figure 2: Measurement setup for transient characterization of photodiodes.

have shown that for both applications mentioned above photodiodes with sufficient performance are realizable in the C0512 IMS CMOS technology.

#### **Readout Circuits**

The readout circuits for both sorts of detectors have to meet hard specifications concerning gain, bandwidth, and noise requirements. To implement circuits with sufficient performance, a detailed analysis of the transimpedance amplifier configuration was carried out and ways for its optimisation have been developed.

Different novel circuit topologies have been investigated. For the field of optical communication a transimpedance amplifier suitable for SONET STS-24 has been realized. Including the photodiode on-chip, the circuit exhibits a transimpedance gain of 64.2 dB $\Omega$ , a bandwidth of 680 MHz, and a sensitivity of -15.1 dBm at 405 nm wavelength.

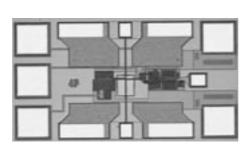

The feedforward concept has been employed to realize transimpedance amplifiers suitable for the use within detectors for optical storage systems. Using this approach, circuits with improved noise behaviour and power consumption could be implemented. A transimpedance gain of 96.0db $\Omega$ , a bandwidth of 83.7 MHz, and an equivalent input noise current of 8.49 nArms while dissipating a power of only 1.73 mW was achieved with a two stage architecture, for example. Furthermore, by using the bootstrapping concept, performance values above what is achievable with the standard transimpedance amplifier configuration have been obtained. In this way a circuit that reads out a photodiode with 4 pF additional capacitance with a gain of 95.86 dB $\Omega$  and a bandwidth of 75.4 MHz was realized (Figure 3).

# Advanced Detectors for optical storage systems

Detectors for optical storage systems usually are simple multi quadrant structures. They provide only spare information about the impinging light signal so that the performance of the signal processing algorithms is low. This results in the need for high quality optical components and cost intensive alignment steps during the fabrication of the systems.

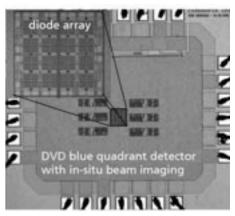

To improve the functionality of such detectors a novel structure has been developed that in-situ combines demodulating and integrating readout approaches (Figure 4) [3]. This allows to extend the information gained in the low frequency spectrum without disturbing the structure for demodulation needed to meet existing standards. The additional data can be used to improve the signal processing, finally leading to a cost reduction for the overall system.

#### References

- [1] F. Yokogawa et al., "The path from a Digital Versatile Disc (DVD) using a Red Laser to DVD using a Blue Laser", Japanese Journal of Applied Physics, Vol. 37, pp. 2176-2178, 1998

- [2] D. M. Kuchta et al., "Performance of fiber-optic data links using 670 nm cw VCSELs and a monolithic Si photodetector and CMOS preamplifier", IBM J. Res. Develop., Vol. 39, No. 1/2, pp. 63-72, 1995

- [3] I. Hehemann et al., "A New Single Chip Optical CMOS Detector for Next Generation Optical Storage Systems", Symposium on VLSI Circuits Digest of Technical Papers, pp. 165-168, 2003

#### Conclusions

The feasibility of fast and highly sensitive, fully integrated optoelectronic circuits in a CMOS technology has been shown. Furthermore, a novel detector architecture for optical storage systems has been implemented and successfully tested. Current work is dealing with investigations concerning the integration of this detector in a system and the perspective of CMOS technologies for spatial division multiplexed optical communications.

Figure 3: Chip micrograph of a bootstrapping transimpedance amplifier.

Figure 4: Chip micrograph of a detector with combined integrating and demodulating readout.

## Dependable Sensor Systems

Dr. D. Weiler

#### Introduction

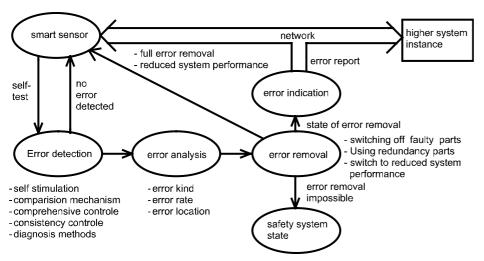

Smart sensors play a critical role in many applications. While in general sensor failure can cause machine damage or inferior product quality, many sensors are employed in safety-critical applications and their failure could cause injury or even death of humans [1]. A second argument for error detection of sensor elements are costs. After fabrication a functionality test follows. To test the full functionality often a complete assembly including the cost expensive packaging is necessary to enable the non-electrical stimulation for full sensor testing. There is a great potential of cost savings if the assembly of defective sensor systems could be avoided by using a test on wafer level. Hence, there is a great need for dependable sensor systems. The presented concept of detection of faulty sensor elements is the key part of a dependable smart sensor system (Figure 1) [2].

A dependable sensor system contains error detection, error analysis, error removal, and error indication functions.

Figure 1: State diagram of a dependable sensor system

The error detection must be developed under aspects of real-time capability and economical costs. If an error occurs the error analysis determines the error type, error rate, and error location for the following error removal. The aim of a dependable sensor system development is to obtain a sensor functionality even in the case of a fault. If a full error removal is not possible a mild or partial performance degradation can be the result if acceptable. If he error removal not possible the system has to reach its safety state. The state of the error removal must be reported to higher system instances.

#### **Error Detection Concept**

The error detection plays the key role in a dependable sensor systems because sensor elements are usually exposed to rough environments, no conventional self-testing strategy for non-electrical stimulation is available, and because possible sensor errors may appear "hidden" by the following signal processing. Conventional error detection methods are based on redundancy, evaluation of mathematical models of the observed process, or knowledge-based models. Use of redundancy incurs additional costs and fails when common mode failures occur. Mathematic models have problems with model uncertainties and robust detection and need complex algorithms which cannot be implemented economically in smart sensors.

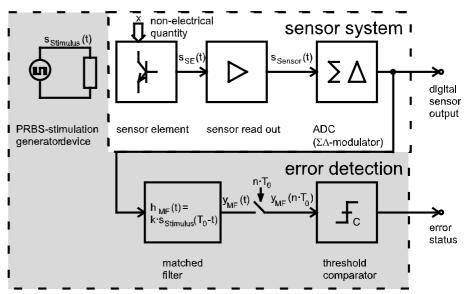

Our error detection is based on electrical self-stimulation of the sensor element combined with matched filtering for detection of the stimulation. Figure 2 shows the block diagram of the error detection method.

The non-electrical quantity x interacts with the sensor element and is conver-

ted into an electrical signal  $s_{se}(t)$ . This signal is read out and digitized using a  $\Sigma\Delta$ -modulator. This sensor system is complemented by the error detector containing a PRBS-generator, a stimulating device, a matched filter, and a threshold comparator.

A PRBS-generator creates an additional stimulus for the sensor element. Therefore the stimulation device interacts directly or indirectly by using crosssensitivity of the sensor element. Stimulation devices can be resistors for thermal stimulation, coils for magnetic stimulation, or plates for electrostatic stimulation.

In a defect-free sensor system the PRBS can be detected at the output signal of the system. Under the assumption that the stimulation frequency  $f_{stim}$  is lower than the corner frequency of the sensor system f<sub>sensor</sub>, the PRBS appears at the output of the sensor system only attentuated by a factor  $\varepsilon_{\text{stim}}$ . The output of the sensor system is fed into the matched filter, which is used to detect the PRBS. A matched filter reduces the amplitude of the stimulation to be detected. Only a small stimulation amplitude V<sub>o</sub> allows an on-line error detection with a minimum disturbance of the measurement of the nonelectrical quantity x. The output of the matched filter is sampled every  $n \cdot T_0$ times, when the correlation peak occurs. The last part of the error detection concept is a threshold comparator which compares the sampled matched filter output to a prescribed threshold C. According to the value of the sampled output the error status is determined. Zero values indicate a defect of the sensor element or of the  $\Sigma\Delta$ -modulator, while values between zero and the prescribed threshold C indicate a reduced sensitivity of the sensor element. In the case of values greater than the prescribed threshold C the sensor system is defect-free.

Using correlation technique the probability for a false alarm  $P_{e,\,min}$  depends only of the signal/noise ratio SNR, which is the quotient between the stimulation energy  $E_{stim}$  and the noise density  $N_{o}$  at the output of the matched filter.

#### System Realization

To prove the functionality of the error detection a temperature sensor as an example for a sensor system has been realized. The sensor system consists of a temperature sensor element and a first order  $\Sigma\Delta$ -modulator. The temperature sensor contains of lateral PNP bipolar transistors with different emitter areas [3]. A positive temperature coefficient derived from the difference of the base-emitter voltage of these transistors is converted by the  $\Sigma\Delta$ -modulators into a pulse density binary stream. The analog/digital converter based on the  $\Sigma\Delta$ -principle achieves a high signalto-noise ratio (SNR) by combining oversampling, interpolation, and noiseshaping while dispensing of the need

Figure 2: Block diagram of the error detection

of high precision analog components [4].  $\Sigma\Delta$ -modulators rely on the noise spectrum of coarsely guantized input signal being shaped and shifted out of the signal band to higher frequencies to achieve fine quantization. The ADC consists of the  $\Sigma\Delta$ -modulator followed by a decimator. This sensor system is complemented by the error detector containing a PRBS-generator, a heating source as the stimulator, a matchedfilter, and a threshold comparator. The pseudo random binary sequence is derived from irreducible codes (m-sequences) using feedback shift registers [5]. The characteristical polynomial used for the PRBS with a period of 7 is:

$$P(x) = X^3 + x + 1$$

To avoid a temperature dependence of the threshold of the sampled matched filter output a PRBS with same number of "0" and "1" is needed. Generators using m-sequences generate an oddnumber length of the PRBS, so we use for the first half of the PRBS the noninverting and for the second part the inverted m-sequence thus obtaining a sequence with the PRBS length of 14. Due to the low-pass character of the heat propagation in the silicon substrate we use a pulse length of  $T_{pulse} = 5s$ . Using a length of the PRBS of 14 every 70s is the error status updated. A resistor acts as the heating source modulated with the PRBS which converts the electrical power into a temperature variation  $\Delta T_{heat}$  of the sensor system. The matched filter has been realized as a correlator consisting of a multiplier and an integrator. Both inputs of the matched filter are digital so there is a simple realization of the correlator using an EXOR-gate for the multiplication of the two input signals  $s_{\Sigma_A}(t)$  and  $s_{PRBS}(t)$  and an up/downcounter for the integration. If both input signals are equal the counter counts up and if they are not equal the

counter counts down. At the end of the PRBS the counter is read out and its value is compared to the threshold C.

The sensor system has being fabricated in a standard 1.2 µm n-well silicon-gate CMOS technology (Figure 3). The die area of the chip is ca. 5.7 mm<sup>2</sup>. Comparing to the same temperature sensor without any error detecting the area has increased by 0.52 mm<sup>2</sup> due the PRBS generator, the matched filter, and the threshold decision circuitry. The polysilicon heating resistor has been placed near the bipolar PNP transistors without an additional area consumption.

#### Measurement results

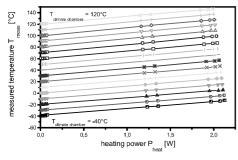

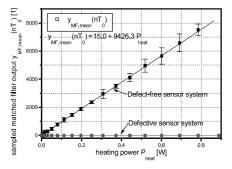

The output of the integrated temperature sensor system is a binary pulse density stream generated by the  $\Sigma\Delta$ modulator. The pulse density exhibits a linear dependence on the temperature with a relatively low slope of 0.3 %/°C due to special requirements of the application for the temperature sensor. When stimulated the heating resistor converts the electrical power Pheat into a temperature change  $\Delta T_{heat}$  of the temperature sensor. The temperature change for a constant heating power for different ambient temperatures in the range between -40 °C and 120 °C is shown in Figure 4: The measured temperature T<sub>meas</sub> rises linearly with the constant heating power

$P_{heat}$ . The measured conversion factor is  $R_{th} = 9$  °C/W. This means that for a temperature rise of ΔTheat = 1.0 °C an electrical power of  $P_{heat} \approx 0.11$  W is needed. By optimizing the design of the heating resistor we aim to reduce the electrical power needed to stimulate.

For the error detection the temperature sensor is stimulated by applying the PRBS to the heating resistor. The samp-

Temperature ΣΔ-modulator Digital part: sensor - PRBS-generator - matched-filter - threshold comparator

Figure 3: Chip photo of the temperature sensor including error detection

Figure 4: Temperature change caused by a constant heating power

led matched filter output shows Figure 5 for different heating power values.

In the case of an faulty sensor the sampled output is around zero, i. e.  $y_{ME}(nT_0) = 0$ , which is independent of the temperature. In the case of an operating temperature sensor cases the pseudo random stimulation causes a sampled output of the matched filter to be much greater than zero. By using a heating power of 0.1 W the difference between operating an faulty temperature sensor is ca. 900. This threshold is easy to detect and yields a negligable false alarm rate. The stimulation using a heating power of  $P_{heat} = 0.1$  W results in a temperature raise of ca.  $\Delta T_{heat} = 1 \text{ °C}$ which is small enough not to disturb the temperature measurement. The described error detection method is so powerful that a change of 0.3 % of the pulse density of the  $\Sigma\Delta$ -modulator can be surely detected.

#### Conclusion

We have presented an error detection concept based on pseudo random stimulation of the sensor element and detection of the stimulation using a matched filter. The concept has been realized using a temperature sensor as an example of the sensor element. The functionality of the error detection method has been proven. With this method it is also possible to determine the sensitivity of the sensor element. The output signal of the system yields a digitized sensor signal. When using electrical or magnetic fields for stimulation a wide variety of sensor elements can be stimulated and in this way a dependable sensor system with error detection can be implemented. Our next goal is to use this error detection method with a capacitive pressure sensor and apply an electrostatic stimulation.

#### References

- D. Hammerschmidt, "Sensor Systems – Interface between Environment and Application", Proceedings ESSCIRC '99, Duisburg, 1999

- [2] D. Weiler et Al, "Detection of Defective Sensor Elements Using Correlation Technique Combined with SD-Modulation", Proceedings Sensor-Kongress 2003, part 2, pp. 413-418, Nürnberg, 2003

- [3] E. Montane et Al, "A compact temperature sensor of a 1.0 μm CMOS technology using lateral PNP transistors", Proceedings THERMINIC Workshop, Budapest, 1996

- [4] J. C. Candy, G. C. Temes, "Oversampling Delta-Sigma Data Converters", Theory, Design and Simulation", IEEE Press, 1991

- [5] R. J. McEliece, "Correlation properties of sets of sequences derived from irreducible cyclic codes", Information and Control 45, 1980

Figure 5: Sampled matched-filter output

# CMOS Line Image Sensors in the FhG-IMS

A. Kemna, W. Brockherde

#### 1. Introduction

Linear image sensors are used in numerous commercial and industrial applications, e.g., bar code readers, line cameras, scanners, copiers, facsimile machines, and optical range sensors.

The classical approach to the realization of such arrays is based on using onedimensional CCD arrays. This technique has matured during the last 25 years and CCD users got accustomed to their limitations in resolution, dynamic range, temperature behaviour, and the complex interfacing. Though the first silicon image sensor was fabricated in a MOS process this approach has been neglected by image sensor developers. But today's submicron CMOS processes can compete with CCDs in performance and offer a lot of additional features: wide temperature range, random pixel access, and, above all, the possibility of cointegration of complex electronic circuitry in a standard CMOS process.

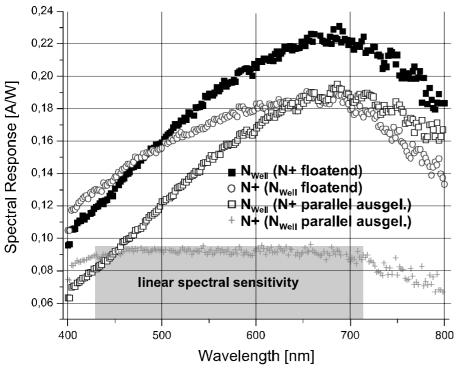

#### 2. Photdetector Devices

In CMOS area imagers mainly standard photodiodes are used as light sensing elements. Photodiodes can be formed by any combination of P- an N-type layers. Due to the wide varieties of pn-junction and layout variations available in a standard CMOS process the photodiodes can be particularly optimised for many parameters e.g. spectral sensitivity, dark current, detector capacitance, low noise, and high speed [1, 2]. As an example the layout linearization of the photodiode spectral sensitivity is shown in Figure 1.

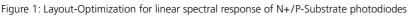

Another photo sensing element which is very attractive for line sensor application too: the photo MOSFET device which is formed by a standard PMOS transistor located in a floating n-well (Figure 2). Even though the phototransistor can not be particularly optimised for such a wide variety of parameters, the element exhibits extremely high photosensitivity and dynamic range. It can be operate up to several 1000 A/W at low irradiation levels due to intrinsic transistor amplification. The device exhibits a wide temperature range (min. -40 °C to +125 °C) and the minimum detectable illumination is below 1 mlx.

Both photodetector devices enable arbitrary pixel geometry and the realization of smart photodetector arrays by CMOS integration of functional blocks, like random pixel access, noise reduction and signal processing blocks as well as on chip analog-to-digital conversion.

#### 3. IMS CMOS Line Sensors

To demonstrate the performance and the enormous potential of this sensor

type we developed and fabricated various CMOS line sensor ICs.

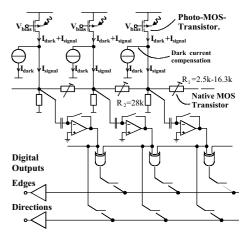

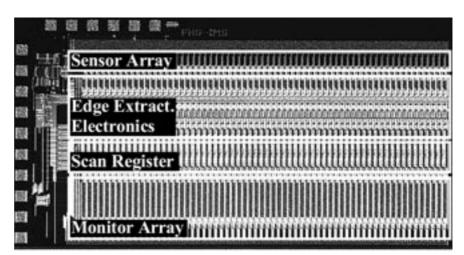

#### 3.1 Fast edge extraction sensor

In Figure 3 a circuit schematic of a CMOS linear photosensor array with fast on-chip edge extraction is shown. It features a 1-D array connected to a distributed resistive lattice network that approximates a spatial Gaussian lowpass filter. Resistors R<sub>1</sub> and R<sub>2</sub> determine the spatial corner frequency and signal gain. Since highly sensitive photo-MOS transistors are used instead of photodiodes, the resistor values can be low and their size is small. For the lateral resistors we have employed tunable resistors based on N-type native MOS transistors operating in the linear region. This enables programmable sequential lowpass filtering of the acquired image at two different spatial frequencies during two subsequent clock phases [3]. An auto-zeroed comparator creates the digital difference signal: the entire operation corresponds to on-chip spatial bandpass filtering followed by a binarization operation and serves to extract edges in images. In addition to the information about edge location, the gradient direction of the edge is also available as a binary signal at the output. A monitoring photosensor array thas uses time-integrated current readout has been laid out in parallel to the edge extraction array in order to enable monitoring of the acquired images without filtering. The 64 pixel edge extraction sensor with a 52 µm pixel pitch has been realized in 1.5 µm double metal n-well CMOS technology and occupies a silicon area of 7.7 mm<sup>2</sup> including the 64 pixel monitor line (Figure 4). The chip needs a single 5 Volt supply and at a readout clock frequency of 16 MHz, a complete edge extraction takes 8 µs. The fixed-pattern noise (FPN) was measured to be about 0.6 %.

The inclusion of median filters and non linear filter functions are promising further improvements in edge detection performance in the future.

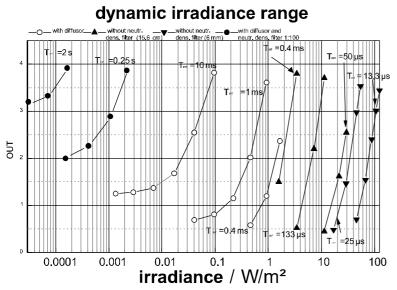

#### 3.2 2048 pixel line sensor

The chip photomicrograph of a second example is shown in Figure 5. The device is a 2048 pixel line sensor with 15 µm pixel pitch employing the photo MOSFET as sensing element. Since the 2048 pixel sensor with a pixel pitch of 15 µm exceed the standard size of a reticle used for lithography during wafer processing, 9 submasks, one for each corner, one for each side and a centre mask are stitched together forming a line sensor 31.4 mm x 3.7 mm of size. Stitching technology is well established in the FhG-IMS. No yield reduction could be observed in addition to the normal chip area determined yield figures.

The device features random block access for fast readout of "regions of interest", dark current compensation, and internal temperature compensation. High photosensitivity, low FPN, and a temperature range of -40 to +125 °C are also important properties. With

Figure 2: Cross section of photosensitive PMOS Transistor

Figure 3: Schematic of edge detection circuit

Figure 4: Chip photomicrograph of the CMOS linear photosensor array with edge extraction

Figure 5: Chip micrograph of 2048 pixel line sensor

variation of the integration time between a few microseconds and several seconds, the chip covers a dynamic illumination range of 177 dB (Figure 6, [4]). Interfacing the sensor is quite simple since it uses a single 5 V supply and a single external clock (up to 10 MHz) for readout. The sensor can be used for various applications like optical measurement, spectroscopy, or scanner applications.

#### 4. Summary

In addition to the presented devices we have prototyped several other CMOS line sensors. These include a velocity sensor for contactless speed measurement, a high speed triangulation line sensor for accurate distance measurement, and a sensor with an analog EEPROM in each pixel to perform automatic FPN correction and on-line subtraction of shading and background patterns. To summarize, the integration of optical line sensors in standard CMOS technology offers an enormous potential for improvement of sensor performance and addition of on-chip signal processing which will lead to new applications and products in the near future.

#### References

- [1] Ingo Hehemann et. al., ESSDERC, September 2002, Florence, Italy.

- [2] A. Kemna et. al., "Low noise, large area CMOS X-Ray image sensor for C.T. applications", IEEE Sensors 2003, Toronto, Canada.

- [3] M. Schanz et. al., "Smart CMOS Image Line Sensors", IEE Transaction on Electron Devices, Vol. 44, Number 10, October 1997.

- [4] W. Brockherde et. al., "Smart 2048-Pixel Linear CMOS Imager", ESSCIRC 1998, The Hague, Netherlands.

Figure 6: Dynamic input range of 2048 phototransistor pixel line sensor

## Automotive CMOS Camera

W. Brockherde, C. Nitta

#### Introduction

Today, the exploding market of digital cameras fuels the development of CMOS image sensors. Though most of the CMOS imager suppliers focus on low cost "single chip cameras" (i. e. combining image sensor and camera electronics on a single CMOS chip) for consumer applications there is a lot of demand for CMOS image sensors for "non-consumer" applications. Besides the possibility of cointegration of sensors and electronics CMOS has some heavy potential advantages: high dynamic range, high temperature range, no blooming, smearing, or time lag, random access, and versatile electronic shutter control. The approach of Fraunhofer IMS is to use these new features to create improved solutions for existing and new imaging and optical sensory applications.

One of the most important and promising fields of advanced CMOS imager applications is that of automotive engineering. This includes on the one hand vision-based applications such as driver assistance systems, collision avoidance, driver monitoring, and rear view and blind spot vision. On the other hand imaging enables a wide variety of optical detection, sensing, and measurements, e.g. for obstacle detection, ranging, and occupancy and precrash sensing.

CMOS-based imaging and optical sensing technologies offer significant advantages. These include low fabrication costs owing to the fact that CMOS is the standard IC technology widely available, wide operating temperature range (>100 °C), and single-chip integration capability.

The CMOS imaging technology, however, offers even more features that elude any comparison with older tech-

nologies previously used. Thus CMOS imagers can be employed as "dual"- or "multiple"-use devices as they can be easily programmed, reconfigured, or multiplexed. E.g., the same CMOS imager can be used for seat occupancy monitoring when the vehicle is in motion or for intrusion detection while it is stationary and burglary alarm is activated. The requirements for both applications greatly differ: this applies not only to image acquisition and signal processing but also to power dissipation. Thus in the latter case the "intrusion detector" runs on battery as the car engine is shut down. Hence low power operation is mandatory in this case.

However, most challenging automotive imaging applications are based on cameras looking outside the vehicle. Let us consider those imposed on cameras for autonomous cruise control (ACC). Such cameras are operated in conjunction with a distance radar: their purpose is to extract the highway lane markings so that the ACC computer can determine whether a vehicle detected by the radar occupies the same lane as the vehicle carrying the ACC. Nevertheless, road illumination conditions can vastly vary not only between the scenes but also within a single scene due to inhomogenous illumination. ACC cameras have thus to exhibit extremely high "optical" dynamic range in order to be able to capture all scene details at night and also with bright sunlight.

#### Highly sensitive CMOS sensor

The Fraunhofer Institute of Microelectronic Circuits and Systems in Duisburg now has developed an automotive camera that satisfies the requirements mentioned above. This 2<sup>nd</sup> generation High-Dynamic-Range Camera is based on a novel CMOS imager that was also

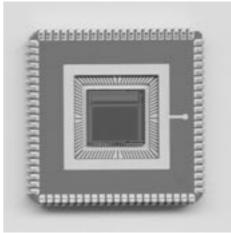

Figure 1: Chip photomicrograph of the 768 x 576 pixel imager array for automotive camera

Figure 2: Raw image (single integration time) taken with the new sensor

Figure 3: Demonstrator camera with Firewire interface

Figure 4: subframes taken with different integration times; total acquisition time: 18 ms

designed by the group and fabricated in 0.5 µm standard CMOS technology available at the institute (see Figure 1). Unlike competing high dynamic range CMOS imagers that employ logarithmic dependence on light irradiance, this imager uses linear dependence and thus does not suffer from poor contrast and high noise typical for "logarithmic" CMOS imagers. The high dynamic range of the CMOS "linear" imager used in the camera developed in Duisburg has been achieved using a sophisticated multiexposure algorithm that yields a 120 dB input dynamic range with excellent image quality unrivaled by other "linear" imagers. The chip exhibits a resolution of 768 x 576 pixels (i. e. "picture elements") while delivering 50 frames/ second in progressive scan (rolling shutter) operation. A first raw image taken with the new sensor (using single integration) is depicted in Figure 2.

#### Demonstrator camera

To demonsrate the performance of the sensor a camera platform has been developed and realized as demonstrator camera for sensor characterization and evaluation (see Figure 3). The camera exhibits an easy to use Firewire interface and transfers 120 dB sub-images of 512 x 256 pixels with the full frame rate, i. e. 50 fps.

The camera and the CMOS sensor will be soon available for evaluation purposes. The preliminary data of both, camera and sensor are listed in Table I. Figure 4 shows four subimages of a scene taken with four different integration times. The subsequent calculation to one high dynamic image will be done in the camera.

The sensor and camera development was financed by the German automobile company BMW, Munich.

| CMOS image sensor                                |                                   |

|--------------------------------------------------|-----------------------------------|

| Acquisition                                      | Progressive scan, rolling shutter |

| Sensitive area                                   | 768 x 576 pixels                  |

| Total # of pixels                                | 796 x 604                         |

| Pixel size                                       | 10 μm x 10 μm                     |

| filling factor                                   | 50 %                              |

| Total chip area                                  | 90 mm² (0,5 μm CMOS)              |

| Power supply                                     | 3.3 V                             |

| Power consumption                                | typ. 120 mW                       |

|                                                  |                                   |

| Full frame-rate (20 ms integration time)         | 50/s                              |

| Maximum frame rate (full frame)                  | 66/s                              |

| Pixel clock                                      | 16 MHz                            |

| on chip gain                                     | 6                                 |

| Demonstrator camera                              |                                   |

| Interface                                        | IEEE 1394                         |

| Full frame (20 ms, 60 dB)                        | 37/s                              |

| Subframe<br>(four integrations 512 x 256; 60 dB) | 50/s                              |

Table I: Data of CMOS sensor and demonstrator camera

# Embedded Microcontroller Applications

H. Kappert, R. Lerch, N. Kordas

#### Introduction

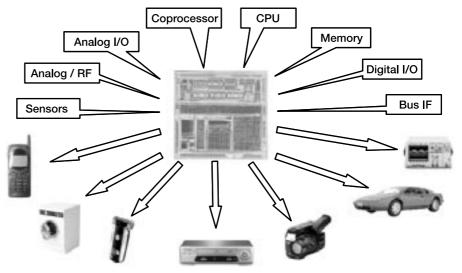

The use of microcontrollers has proliferated over the past two decades. Todays large scale integration technologies allow the integration of "embedded controllers" together with additional analog and digital electronics on a single microchip. Custom ICs based on microcontrollers are now seen even in the most mundane applications.

However, many of the design approaches use fixed microcontroller cores with invariant standard peripherals, resulting in sub-optimal designs for dedicated applications.

Fraunhofer IMS has realized a new design strategy for microcontroller applications. In the past years, a design environment consisting of a portfolio of microcontroller cores, hardware emulation platforms and a comfortable test and debug concept was established.

IMS has successfully integrated its microcontrollers into various applications, e.g. in data acquisition systems, medical applications, controllers for household appliances or industrial ICs. The actual applications are based mainly on two different controllers: the IMS2205 and the IMS3311 which are opcode compatible to well known industrial microcontrollers from Motorola (MC6805 and MC6811). The continuous success of the IMS strategy is based on a few elements which are highlighted below.

system size is growing from this starting point. Customers having a first contact with our cores usually wonder: why is it only a core? At the first glance, the IMS controller IP is seems to be just a microprocessor core which includes absolutely no peripherals or memories. Indeed, our controller IP also includes a set of standard peripheral IP as independent modules. They can be combined with the processor IP and technology-dependent memory modules into a complete application specific microcontroller system. This allows for a full custom system without any ballast from standard peripherals which are not necessary or oversized for the target application. We call this the lean core approach.

#### Flexibility

The lean core approach gives the customer high flexibility in his application. Besides the core IP, standard peripherals are available. Several projects have shown that standard peripherals are nice to have but that the main benefit comes from full custom blocks which make an application as powerful as required. With the lean core approach,

Figure 1: Embedded Microcontroller

#### Lean core approach

The typical IPs in the microcontroller business are macros which contain peripherals in a more or less static configuration. All developments start from this macro and typically, the a controller system can be integrated around the microprocessor core, which is fully optimized for the application.

#### **Full Custom Peripherals**

For the IMS controller cores a growing set of standard peripherals like generalpurpose IOs, Serial Communication Interface (SCI, ASIO), Serial Peripheral Interface (SPI), I<sup>2</sup>C, CAN, Timer, Watchdog are available. All controllers and digital peripherals are based on hardware description languages and can thus be used in any technology. Besides these pure digital blocks, analog blocks for signal conditioning or mixed analog digital blocks like A/D and D/A converters are also part of the portfolio.

As mentioned above, several projects have shown that the main benefit lies in the full custom design of peripherals. A large number of these peripherals have been developed. Some blocks have been designed for data and memory management, e.g. a Memory Management Unit. Especially in the field of data acquisition, often a large amount of data must be handled. This guickly exceeds the address space of the 8-Bit microcontroller cores. With a Memory Management Unit, memory sizes much larger than the controllers address space can be handled easily. Two other blocks were designed for automatic data management, verification and protection in form of checksum, respectively. For the verification of larger data blocks or the protection of communication frames, a Cyclic Redundancy Check circuit has been developed. For data management a Direct Memory Access module has been designed. Direct Memory Access can be used in many applications, where higher volumes of data have to be moved between memory and peripherals without the need of the controller. This can be used e.g. in measurement systems or communication systems. While data is automatically transferred between memory and peripherals, the controller can perform some calculations or formatting tasks. Alternately, the controller may enter a power-saving idle mode during periods of inactivity, with the DMA module still running.

Another kind of blocks have been integrated which make use of Direct Digital frequency Synthesis. These blocks have been developed for different industrial applications to control freely adjustable frequencies. With the additional capability of pulse width modulation we have used this technique to control single or multiphase bridge configurations for steppers or motors.

Current research activities are in the field of coprocessors which are optimized for data stream processing as needed for data encoding, compression or encryption.

Besides these digital blocks full custom analog peripherals exist like dedicated amplifiers, oscillators or filters.

#### Emulation

A key aspect of IMS embedded controller development is emulation. It enables the customer to start software development and application debugging in parallel to ASIC development. For several years now, IMS has provided the ASIC emulator, which has been superseded by the SoC-Emulator recently. If higher volumes of emulator prototypes are needed, a dedicated emulator can be developed without the overhead of the general purpose SoC-Emulator.

With the emulator the IMS or the customer are able to rapidly prototype

the new application. The central element is based on one or more FPGAs which allow the full emulation of the digital part. Analog parts are emulated with a functionally compatible replacement based on standard components. Tools have been developed to support FPGA and ASIC synthesis with regard to specific modifications driven by constraints from the FPGAs and the ASIC flow, respectively.

A powerful graphical user interface allows hardware and software debugging on the emulator and ultimately on the ASIC as well. The emulation of the whole digital part leads to a high confidence level for the later ASIC integration and the final application.

#### Test and Debug

All controller applications based on the IMS microcontroller cores are equipped with a test and debug interface based on the IEEE1149.1 (JTAG) standard, with powerful extensions for internal scan. The number of necessary additional pins can be significantly reduced, down to one or even no additional pin, by multiplexing functional pins in test mode. This technique has already been sucessfully proven in several applications. The JTAG interface and a full scan approach is today's standard to achieve a test coverage of more than 98 % as required by industry. The main advantage of the interface implemented with the IMS cores is its support for hardware and software debugging on the final ASIC, without additional overhead.

#### Outlook

The IMS controller integration team intends to extend the portfolio by a

RISC-based scaleable architecture in the field of up to 16 bit controllers. Special research activities center on low power applications and coprocessors.

#### Summary

This article has highlighted the IMS activities on microcontrollers and has outlined the many advantages of our methodology. It's key idea is to leverage a lean core strategy to provide the flexibility necessary to optimize the system according to the application requirements. This results in optimized full custom devices with a minimum of overhead. With the complete design flow starting with rapid prototyping via the system integration up to the final test and debug, IMS provides a powerful way to integrate full custom microcontroller systems. Especially the early prototyping leads to a high confidence level for the final ASIC and the success of the application.

Figure 2: SoC Emulator Prototype

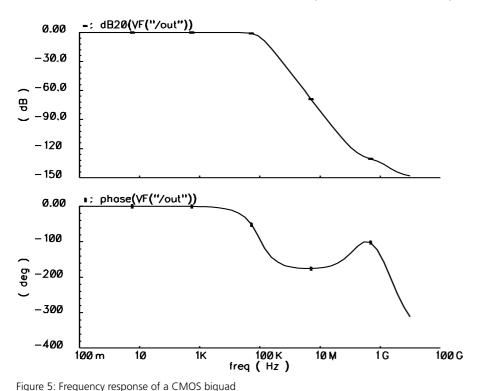

# Digital Sinc-Filter for High Order Sigma-Delta-Modulators

M. Gnade, A. Kemna

#### Introduction

In numerous sensor applications an immediate analog to digital conversion of the acquired sensor signal is desired. For an integration of the sensing element and the readout circuitry on a single chip one particular ADC architecture has proven to be very suitable. Sigma delta modulators of higher order are capable of achieving very high resolution for a limited signal band without making high demands on technology parameters. The output of such a sigma delta modulator, a pulse density modulated signal at a very high clock frequency, has to be decimated in order to obtain a digital PCM signal out of it. The combination of the sigma delta modulator and the decimation filter forms the complete ADC. Since the signals are in a digital format right at the output of the modulator there is no need to implement the decimation filter on the same chip as the sensing element and the readout circuit. Thus the decimation filter can be realized using different technologies like an FPGA or an ASIC based on a pure digital CMOS technology exhibiting a minimum feature sizes of 130 nm.

#### Filter description

Digital sinc filters are commonly used to implement decimation by large factors without using complex digital circuitry. To obtain an optimum the filter order should exceed the order of the sigma delta modulator by one [1]. The corresponding transfer function in the z-domain is

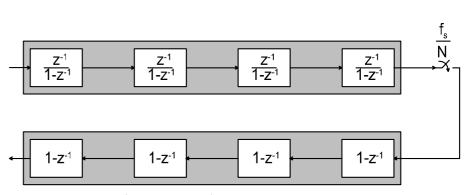

$$H(z) = \left(\frac{1 \cdot 1 - z^{-N}}{N \cdot 1 - z^{-1}}\right)^{\kappa}$$

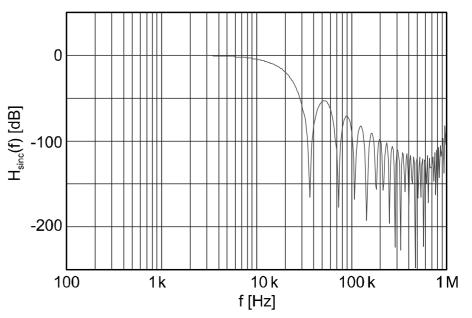

where N is the decimation ratio and k the order of the sinc filter.

The transfer function of a sinc filter of 4<sup>th</sup> order designed to decimate the output signal of a 3<sup>rd</sup> order sigma delta modulator is plotted against the freguency in Figure 1. Since the transition from the passband to the stopband is not very steep the sinc filter is only suitable for the first stage of a multistage decimation filter. The minimum output clock frequency should be 4 times the Nyquist frequency in order not to loose too much signal power by filtering. The sinc filter is built up of three subassemblies, an IIR part consisting of digital accumulators, an FIR part, comprising digital differentiators, and a subsampler. Figure 2 shows a block diagram of a sinc filter of 4<sup>th</sup> order.

The above mentioned sigma delta modulator which the sinc filter is designed for is of 3<sup>rd</sup> order, it has a signal bandwith of 3.6 kHz and an oversampling ratio of 150. With an ideal low pass filter this modulator is able to reach a signal-to-noise ratio of 98.52 dB which corresponds to a resolution of 16.36 bits. Thus the described sinc filter has to be of 4<sup>th</sup> order and it implements decimation by a factor of 30. Consequently the oversampling ratio behind the sinc filter is 5. With these boundary conditions the whole system consisting of sigma delta modulator and sinc filter is able to reach a signal-to-noise ratio of 68.92 dB and, therefore, a resolution of 11.45 bits. This loss in resolution of nearly 5 bits can be outweighed by using a second filter stage performing an additional decimation by a factor of 5.

The minimum word length w of the registers of that the accumulators and differentiators in Figure 2 are built of is calculated by

$$w = k \cdot \log_2(N) + b$$

where k is the order of the sinc filter, N is the decimation ratio, and b is word-

length of the pulse density modulated signal to be decimated [2]. For the realized filter this equation yields a word length of 21 bits. With this condition the accumulators are allowed to overflow without having an influence on the signal integrity. Both, a realization in an FPGA and the integration as an ASIC of this decimation filter is possible.

#### References

- Norsworthy, Schreier, Temes, "Delta-Sigma Data Converters, Theory, Design and Simulation", IEEE Press, 1997

- [2] Dijkstra, Nys, Piguet, Degrauwe, "On the Use of Modulo Arithmetic Comb Filters in Sigma Delta Modulators", IEEE Proc. on the Int. Conference on Acoustics, Speech and Signal Processing '88, April 1988

Figure 1: Frequency response of the sinc filter

Figure 2: Block diagram of the 4th order sinc filter

### Cascaded Sigma-Delta-Modulators of Higher Order Without Stability Problems

Dr. D. Weiler

#### Introduction

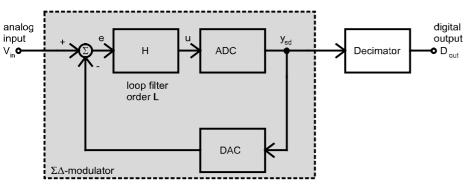

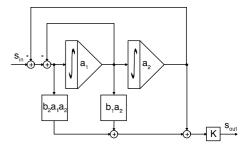

Analog/Digital converter (ADC) based on the sigma-delta  $(\Sigma \Delta)$ -principle achieve a high signal to noise ratio (SNR) by combining oversampling, interpolation, and noise shaping while dispensing with the need of high precision analog components [1]. A  $\Sigma\Delta$ -ADC consists of a  $\Sigma\Delta$ -modulator followed by a decimator (Figure 1). The SNR of the ADC is mainly determined by the  $\Sigma\Delta$ -modulator. The parameters of the  $\Sigma\Delta$ -modulator are oversampling ratio OSR, order of the modulator L, resolution of the internal ADC B, and the architecture. An increase of the OSR, order L, or the resolution B will increase the SNR of the ADC. The choice of using a high OSR has the disadvantage of high power consumption and the maximum sampling frequency is limited by the technology. Therefore, a moderate OSR is a better choice. The consequence is that a high order loop filter or multi-bit quantization is necessary. Both approaches can be realized using different architectures: single-loop or cascaded  $\Sigma\Delta$ -modulator. A 3<sup>rd</sup> order single-loop  $\Sigma\Delta$ -modulator has been well implemented at the IMS in the last years. Further increasing of the order will result in serious stability problems. The high sensitivity to DAC non-linearity using multi-bit guantization requires

Figure 1:  $\Sigma\Delta$ -ADC with single-loop  $\Sigma\Delta$ -modulator

correction mechanism and therefore increase the complexity. To overcome stability problems and DAC non-linearity cascading of  $\Sigma\Delta$ -modulators can be a solution.

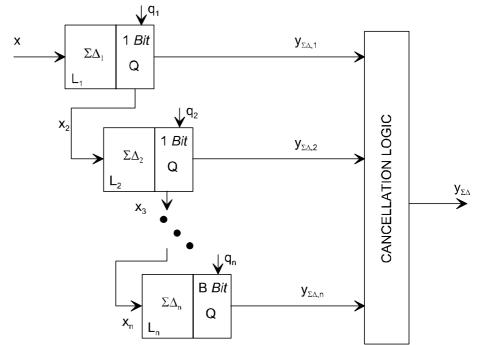

#### Cascades $\Sigma\Delta$ -modulators

Cascaded  $\Sigma\Delta$ -modulators consist of stable 1<sup>st</sup> or 2<sup>nd</sup> order  $\Sigma\Delta$ -modulators. Since the cascaded  $\Sigma\Delta$ -modulator contain only feedforward paths and there is no feedback between the single-loop modulators they have inherently no stability problems for higher orders [2]. By using only multi-bit quantization at the last cascade the sensitivity to DAC non-linearity can be drastically reduced [3]. The disadvantage of cascaded  $\Sigma\Delta$ modulators is their higher sensitivity to other circuit imperfections like capacitor mismatching.

The general architecture of a cascaded  $\Sigma\Delta$ -modulator shows Figure 2. The cascaded  $\Sigma\Delta$ -modulator consists of several low order single-loop  $\Sigma\Delta$ -modulators, each with its own quantizer. Each  $\Sigma\Delta$ -modulator in the cascade converts the quantization error E of the previous modulator. The quantization error of all modulators with the exception of the last stage will be eliminated digitally by the cancellation logic. The total order of the cascaded  $\Sigma\Delta$ -modulator is the sum of the used single-loop modulators:

$$L = L_1 + L_2 + K + L_n$$

The output signal of the  $\Sigma\Delta$ -modulator after the cancellation logic

$$Y (z) = z^{-1} \cdot X (z) + d \cdot (1 - z^{-1})^{L} \cdot Q_n (z) - d \cdot (1 - z^{-1})^{L - L_n} \cdot E_n (z)$$

consists of the input signal X(z), the  $L^{\rm th}$  order noise shaping of the last-stage

quantization error, and the  $(L-L_n)^{th}$  order shaping of the DAC error in the last stage [4]. The attenuation of the DAC error is only valid in the described architecture with single-bit quantizer in all but the last stage and multi-bit quantization only in the last stage.

Since the 1<sup>st</sup> order  $\Sigma\Delta$ -modulator has a poor idle-tone performance it is better to use a 2<sup>nd</sup> order  $\Sigma\Delta$ -modulator as the first stage of the cascaded  $\Sigma\Delta$ -modulator. Imperfect cancellation because of mismatch could degrade the overall idle-tone performance to be determined by the first stage.

#### Simulation results

Since  $\Sigma\Delta$ -modulators represent heavily non-linear systems, an exact mathematical analysis is extremely difficult [2]. To predict the SNR of cascaded  $\Sigma\Delta$ -modulators simulations are the only accurate method. All simulation results in this communication obtained using behavior simulations based on SIMULINK models. Several circuit non-idealities affecting the SNR, and, therefore the resolution are considered in the models. Relevant non-idealities in switched capacitor realizations are: capacitor mismatch, sampling jitter, kT/C-noise, and the OTA-non-idealities including finite DC gain  $A_{v0}$ , gain-bandwidth GBW, slew-rate SR, and OTA-noise.

The simulation results compare different architectures with an order of 3. The first used architecture is a 1-1-1  $\Sigma\Delta$ -modulator, which consists of three 1<sup>st</sup> order single-loop  $\Sigma\Delta$ -modulators. The second architecture is a 2-1  $\Sigma\Delta$ -modulator with a 2<sup>nd</sup> order  $\Sigma\Delta$ -modulator to a the first stage and a 1<sup>st</sup> order a the second stage. Both cascaded  $\Sigma\Delta$ -modulators are compared to a single-loop 3<sup>rd</sup> order  $\Sigma\Delta$ -Modulator. Figure 3 shows a FFT of the output  $y_{\Sigma\Delta}$  of a 1-1-1  $\Sigma\Delta$ -modulator with an input frequency of  $f_{in} = 1$  kHz and a sampling frequency of  $f_s = 128$  kHz. This plot shows the characteristic rise of the shaped quantization noise with 60 dB/dec for a 3<sup>rd</sup> order  $\Sigma\Delta$ -modulator. Due to nearly ideal cancellation no idle-tones occur.

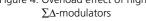

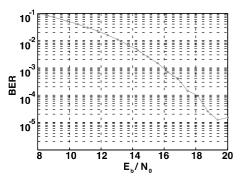

Figure 4 shows the sweep of the input amplitude versus the SNR for all three modulator architectures. A  $\Sigma\Delta$ -modulator containing only 1<sup>st</sup> order modulators shows no overloading effect. A 2<sup>nd</sup> order  $\Sigma\Delta$ -modulator becomes unstable for input amplitudes above 80 % of the reference voltage of the feedback DAC and for a 3<sup>rd</sup> order  $\Sigma\Delta$ -modulator the overload limit is at ca.70 %. This figure shows one advantage of cascaded  $\Sigma\Delta$ modulators compared to high-order single-loop modulators concerning the dynamic input range.

The serious problem of cascaded  $\sum \Delta$ -modulator is their mismatch dependence

Figure 3: FFT of the output of a 1-1-1 cascaded  $\Sigma\Delta$ -modulator

Figure 2: General architecture of a cascaded  $\Sigma\Delta$ -modulator

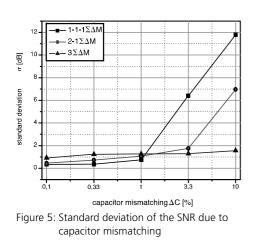

because of imperfect noise cancellation in the analog part. Figure 5 shows the standard deviation of the SNR for different capacitor mismatch values [5]. This simulation result has been archived by repeating 1000 simulations with randomized gain factors, which represent the mismatch. The single-loop  $\Sigma\Delta$ -modulators shows no SNR-dependence on mismatch. A variation of the gain factors results only in a very small modification of the noise-shaping and therefor in the SNR. A different dependence show the cascaded modulators. The standard deviation of the SNR raises for increased mismatch. Mismatch above 1 % results in a poor noise cancellation and, therefore, in a reduced SNR. The effect becomes more pronounced if the number of single-loop stages increases. This limits the order of cascades  $\Sigma\Delta$ modulators to L = 6.

The effect of sampling jitter is independent of the modulator architecture because it affects only the sampling stage. Sampling jitter has a heavy effect on the SNR and, therefore, the sampling state needs a careful design.

Other non-idealities of the OTA affect the SNR in both architectures in similar manner.

#### Conclusion

A comparison of single-loop and cascaded  $\Sigma\Delta$ -modulators have been derived using SIMULINK behavior simulation. To overcome stability problems of high order single-loop  $\Sigma\Delta$ -modulators cascaded modulators are an alternative. The effect of capacitor mismatch can be tolerated for technologies with a matching of better 1 % for modulator order smaller than L = 6. The consisting disadvantage of cascaded  $\Sigma\Delta$ -modulators is their area-overhead due to the quantizers located at each single stage.

#### References

- J. C. Candy, G. C. Temes, "Oversampling Delta-Sigma Data Converters", Theory, Design and Simulation, IEEE Press, 1991

- [2] M. Rebeschini, "Capter 6: The Design of Cascaded ΣΔ ADCs", in "Delta-Sigma Data Converter", IEEE Press, 1996

- [3] F. Mediiro et Al., "Using Cascade SD Modulators for xDSL MODEMs in Digital Technologies: Architecture Selection and Systematic Design", Mixed-Signal Design Cluster Workshop on Embedded Data Converters, Stockholm, Sweden, September 2002

- [4] A. Rodríguez-Vázquez et Al., "High-Speed, High Resolution ∑∆ Modulators: An Overview with Emphasis on Cascade Architecture", Mixed-Signal Design Cluster Workshop on Embedded Data Converters, Stockholm, Sweden, September 2002

- [5] A. Hellebrand, "Analyse und Bewertung von kaskadierten Sigma-Delta-ADCs im Vergleich zur 'Single-Loop'-Topologie", Diploma thesis, University Duisburg-Essen, November 2003

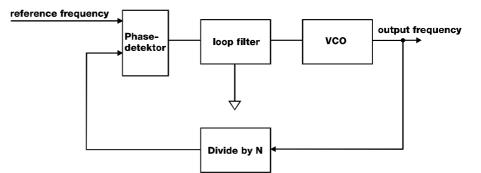

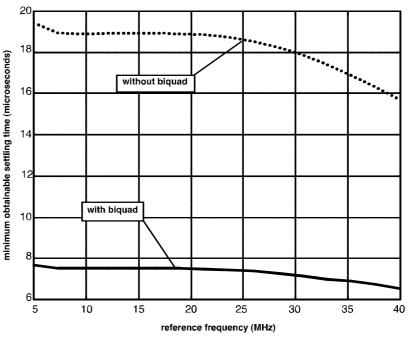

## Rapid Prototyping for Wireless System-on-Chip Solutions

M. Marx, H.-C. Müller, R. Kokozinski

#### Introduction

The improvements in the area of microelectronics lead to shorter design cycles and rapidly rising complexity of electronic designs. Therefore, developers are forced to refine the system development process to avoid a productivity gap. *Rapid prototyping* (RP) is a technique to support the system development. The term rapid prototyping is defined as a type of prototyping in which emphasis is placed on developing prototypes early in the development process to permit early feedback and analysis.

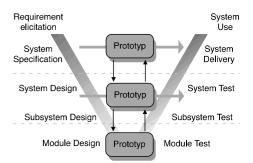

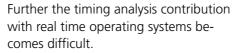

The IMS design-flow for wireless System-on-Chip is based on the traditional development process which can be represented in the V-model. The V-model enhanced by different levels of rapid prototyping is called VP-model [2] (Figure 1). The idea of rapid prototyping is to skip time intensive steps of the development process, and reduce the time to get a first functional prototype of the entire system or a part of the system. This prototype allows the validation of functionality and early performance tests. The comparison between different design alternatives can be simplified and therefore the conceptual validation rises.

Also in future, wireless systems (WS) will be implemented by a mixed analogue and digital signal processing but the ratio of *digital* functions in the value-added chain is increasing rapidly. This contribution focuses on RP to speed up the design flow for *digital* WS.

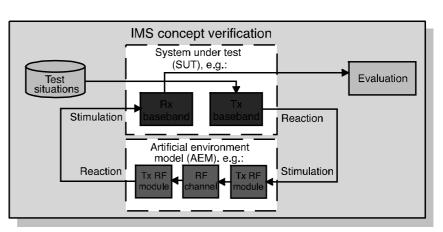

#### Prototyping versus Simulation

A first rough behaviour modelling of the system under test (SUT) is achievable in a system simulation tool like Matlab/ Simulink. Normally, every system under test interacts with a real environment. For simulation, these interactions must be emulated, too. Thus, in most applications a second rough emulation – an artificial environment model (AEM) – of the real environment is necessary, where the SUT is embedded in.