IIS

BMBF-Verbundprojekt: SiPoB-3D Förderkennzeichen: 16ES0384

Projektlaufzeit: 01.03.2016 bis 28.02.2019

Abschlussbericht

Co-Design für System-in-Package-on

**Board:**

Management von Komplexität und Entwurfsland-schaft zur Erarbeitung

kompakter

3D Systemlösungen"

Akronym: SiPoB-3D

Teilvorhaben: Designmethoden und Designflows für das System-in-Package-

on-Board Co-Design

Version: 1.0

Erstelldatum: 31.01.2020

Autoren: Andy Heinig (Fraunhofer IIS/EAS)

Zuwendungsempfänger: Fraunhofer-Gesellschaft zur Förderung der angewandten

Forschung e.V.

Ansprechpartner: Teilprojektleiter

Fraunhofer IIS/EAS (EAS)

Andy Heinig Zeunerstraße 38 01069 Dresden

Tel: +49 351 4640 783 Fax: +49 351 4640 703

andy.heinig@eas.iis.fraunhofer.de

## Inhalt

| I. Ziele                                                                             |                                 | 4             |

|--------------------------------------------------------------------------------------|---------------------------------|---------------|

| I.1 Problemstellung und allgemeine Ziele des V                                       | orhabens/                       | 4             |

| I.1.1 Motivation                                                                     |                                 | 4             |

| I.1.2 Das Gesamtziel des Vorhabens                                                   |                                 | 5             |

| I.2 Wissenschaftliche und/oder technische Ziele                                      | e des Vorhabens                 | 5             |

| I.3 Ausgangssituation und Voraussetzungen, wurde                                     | unter denen das Vorhaben durch  | hgeführt<br>8 |

| I.3.1 Der Stand von Wissenschaft und Technik                                         |                                 | 8             |

| I.3.1.1 Aktuelle globale Situation (fehlende                                         | Fähigkeiten)                    | 8             |

| I.3.2 Neuheit und Attraktivität des Lösungsansa                                      | atzes                           | 10            |

| I.4 Abgrenzung und Zusammenarbeit mit ander                                          | ren Projekten                   | 10            |

| II. Technische Ergebnisse                                                            |                                 | 11            |

| II.1 Arbeitspaket 0: Spezifikationen, Anforde<br>Abgleich mit internationalen Trends | rungen, regelmäßige Statusanaly | se und<br>11  |

| II.2 Arbeitspaket 1: Simulation und Modellierun                                      | g                               | 11            |

| II.3 Arbeitspaket 2: Flow-Integrations und Design                                    | gn Methoden                     | 14            |

| II.4 Arbeitspaket 3: Design Flow Infrastruktur                                       |                                 | 18            |

| II.5 Arbeitspaket 4: Validierung durch Test-Beis                                     | spiele und Prototypen           | 19            |

| III. Verwertung und voraussichtlicher Nutz                                           | en en                           | 21            |

| III.1 Ausgangslage                                                                   |                                 | 21            |

| Nutzen und Verwertbarkeit                                                            | Fehler! Textmarke nicht de      | efiniert.     |

| IV. Veröffentlichungen                                                               |                                 | 23            |

## Zusammenfassung

Im Projekt SiPoB-3D wurde Methoden und Verfahren für den effizienten Entwurf von kompakten 3D-Systemen entwickelt. Dies ziele vor allem auf das Co-Design von System-in-Package und gleichzeitig dem Board, um eine übergreifende Optimierung zu ermöglichen und gleichzeitig Designsicherheit zu erreichen. Das Teilvorhaben Designmethoden und Designflows für das System-in-Package-on-Board Co-Design ist notwendig, um zwischen den eingesetzten Werkzeugen und Methoden geeignete Schnittstellen zu definieren, diese bzgl. Validierung und Optimierung zu bewerten und schließlich einen entsprechenden Design-Ablauf zu definieren. Dies wurde notwendig, um im globalen Wettbewerb bei der steigenden Komplexität marktfähige Lösungen entwickeln zu können.

Das Fraunhofer IIS/EAS arbeitete dabei an den folgenden Themenkomplexe im Projekt mit. Im essentiellen Bereich der Simulation und Modellierung sind dies Modelle für die Heterogene Chip/Package Integration, um thermische Analysen der Systeme zu ermöglichen. Bei der Flow-Integration wurde Methoden für frühzeitige Design Abschätzungen entwickelt und eine Ansatz für die Wiederverwendung von Hochfrequenz Komponenten in Package-Substraten untersucht. Die aufgesetzten Methoden und Design-Flows wurde evaluiert und im Entwurf von entsprechenden Prototypen eingesetzt.

| Version 1.00 | 07.02.2020 |

|--------------|------------|

|--------------|------------|

Abschlussbericht SiPoB-3D Seite: 4

#### I. Ziele

## I.1 Problemstellung und allgemeine Ziele des Vorhabens

#### I.1.1 Motivation

Die Integration von immer mehr Funktionalität in kleinste Volumina sowie die Erhöhung von Leistungsfähigkeit und Energieeffizienz wird in allen für Deutschland wichtigen Märkten bedeutsamer. Dies gilt besonders für die Bereiche Mobilität (insbesondere Auto, Bahn, Flugzeug, allgemein für Elektromobilität), Energietechnik, Industrie4.0, Internet of Things, Medizintechnik, oder Beleuchtungstechnik.

Neue Technologien, wie z.B. "More than Moore (MtM)", hochintegrierte 3D-Technologien (3D-IC) oder "System in Package (SiP)-Technologien", werden immer wichtiger für kompakte Elektroniksysteme. SiP beinhaltet in diesem Projekt insbesondere auch verschiedene Chip-Embedding Technologien. Wir haben immer mehr eine Mischung aus vielen Technologien und vielen verschiedenen Materialien.

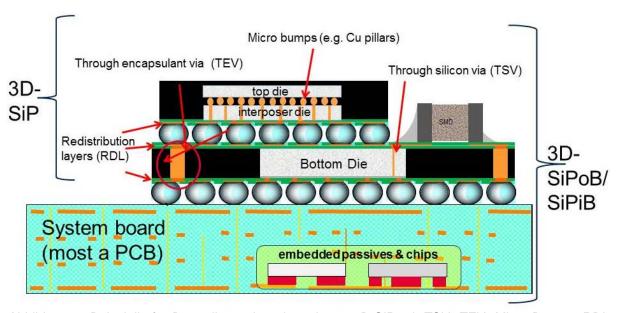

Abbildung 1 zeigt beispielhaft den schematischen Querschnitt eines komplexen 3D-SiP-Aufbaus, der zusammen mit einem Board ein kompaktes System bildet, wie es in CoSiPoB erforscht werden soll. Das 3D-SiP enthält verschiedene neuartige Technologien wie Through-Silicon-Vias (TSV), Through-Encapsulant-Vias (TEV), Redistribution Layers (RDL) und Micro-Bumps beinhaltet. Auch im Board sind zusätzliche Bauelelemente integriert.

Für solche komplexen SiPs können teure Prototypen nicht ohne eine entsprechend geeinte Design- und Simulationsumgebung für umfangreiche Vorfertigungs-Simulationen (z.B. für Design-Rules Überprüfung, thermische, elektrische Simulation) hergestellt werden Die Gefahr zu scheitern ist zu hoch. Daher besteht zunehmend der Zwang, eine zusammenhängende Chip-Package-Board-Co-Design-Umgebung zu schaffen, die Halbleiterchips, passive Bauelemente, das Gehäuse sowie das Board (Platine) umfasst. Nur dadurch sind optimale Kompromisse für ein Gesamtsystem aus verschiedenen Halbleiterchips, Gehäuse und Board möglich.

Abbildung 1: Beispielhafte Darstellung eines komplexen 3D-SiP mit TSV; TEV, Micro-Bumps, RDL, diskreten passive Bauelementen und drei Chips.

| Version 1.00 | 07.02.2020 |  |

|--------------|------------|--|

|              |            |  |

#### I.1.2 Das Gesamtziel des Vorhabens

Das SiPoB-3-Projekt zielt in drei Richtungen:

- i) Verbesserung der Chip-Package-Board Co-Design Landschaft durch Beschleunigung von Erforschung, Entwurf, und Markteinführung künftiger kompakter Systeme unter Berücksichtigung einer optimalen Lösung bestehend aus Chip, Gehäuse und Board.

- ii) Verbessertes Simulieren und Modellieren, Aufbau einer Toolbox von SiP-Komponenten und dadurch Stärkung der Einsatzmöglichkeiten neuer, innovativer Technologien, wie z.B. "More than Moore (MtM)" Technologien, 3D Integrationstechnologien (3D IC) Technologien, und "System in Package (SiP)" Technologien, sowie innovative Substrattechnologie (z.B. Chip-Embedding).

- iii) Durch zusammenhängende Betrachtung von Chip, Gehäuse und Board schnelle Erforschung und Erarbeitung neuer Integrationstechnologien für leistungsfähige Systeme hinsichtlich Getriebesteuerung und mm-Wellen-System.

Die Forschungsarbeiten werden von den Dresdner Fraunhofer Instituten IIS/EAS und dem IZM-ASSID, sowie dem Lehrstuhl für Technische Elektronik der Universität Erlangen wissenschaftlich unterstützt.

#### Vom SiPoB-3D Projekt werden

- i) die deutschen Halbleiter- und Systemhersteller (Infineon und Conti, sowie Symeo und Hitex) durch Erforschung und Erarbeitung einer zusammenhängenden Co-design Umgebung mit notwendiger Simulations- und Modellierungslandschaft profitieren;

- ii) die deutschen Halbleiter- und Systemkomponentenhersteller durch kürzere Entwicklungszeiten und somit schnellere Markteinführung und damit bessere Wettbewerbsfähigkeit profitieren,

- iii) der Toolhersteller CST durch Erarbeitung neuer Einsatzmöglichkeiten für seine Produkte profitieren,

- iv) die Boardhersteller durch Erarbeitung von Speziallösungen für Produkte der internationale Halbleiter- und Gehäuseindustrie (Aufbau- und Verbindungstechnik)

profitieren.

#### I.2 Wissenschaftliche und/oder technische Ziele des Vorhabens

Kompakte Systemintegration bedeutet die Integration von mehr Funktionalität in ein immer kleineres Volumen. Diese kompakte Integration von Chips in ein 3D-SiP und die Integration dieser gehäusten Chips auf oder in einer Platine (PCB), führt zu neuen Herausforderungen. Zukunftig dürfen nicht nur die technologischen Herausforderungen betrachtet werden, es muss auch die zu diesem Zweck erforderliche Entwurfsumgebung und Methodik erforscht und entwickelt werden, die das Design eines optimalen Gesamtsystems, bestehend aus einem Kompromiss zwischen Technologie und Kosten, in begrenzter Zeit erlaubt. Eine zusammenhängende Chip-Package-Board-Co-Design-Umgebung muss entwickelt werden,

| Version 1.00 | 07.02.2020 |

|--------------|------------|

|--------------|------------|

welche die drei unterschiedlichen Domänen <u>Chips und passive Bauelemente</u>, <u>Gehäuse</u> und <u>Board (Platine)</u> umfasst.

Tabelle 1, linke Spalte, zeigt die sieben wichtigsten Herausforderungen für SiPoB-3D. Das Ziel ist dabei die Bereitstellung von Lösungen (in der rechten Spalte), um das optimale System/Subsystem als Ganzes zu erreichen.

Tabelle 1: Hauptherausforderungen von Fraunhofer in SiPoB-3D und die wichtigsten Innovationsziele

| Herausforderung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SiPoB-3D Ziele für die folgenden Aspekte                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Herausforderung 1:  Einheitliche Entwicklungsumgebung Bedarf einer einheitlichen Entwicklungsumgebung, die die verschiedenen Domänen Chip, Package und die Board (Platine) für die Optimierung des Systems als Ganzes abdeckt, um es sowohl schneller, besser und mehr ökonomisch zu gestalten.  Herausforderung 2: Überbrückung der Lücke zwischen 3D-SiP und dem Board Heute erfordern typische Designs bzw. Anforderungsanfragen eine klare Abstimmung zur Gewährleistung der gefragten Funktionalität. Deshalb wird und ist es immer öfter zwingend wichtige beitragenden Unternehmen in der Kette in die Konzeptionierung mit einzubeziehen. So muss die Lücke zwischen Chip-Technologie, Packaging und Montage geschlossen werden. Unternehmen wie Infineon und ST Microelectronics sowie Continental müssen mit anderen Bereichen wie der Substrattechnologie im besonderen der Leiterplatte zusammenarbeiten. | Entwicklungsumgebung für das elektronische Design unter Anwendung zuverlässiger Baugruppen; dies beinhaltet den Datenaustausch zwischen den drei Domänen, genauso wie die Datenkomplexität (z.B. für DRC)  Ziel 2: Überbrückung der Lücke zwischen 3D-SiP und dem Board Aufbau einer Umgebung für einen optimalen Daten-Austausch und einer Designschnittstelle zwischen 3D-SiP und der Platinen-Welt (Board) um das optimale System im Package auf der Platine (SiPoB-3D) als ein Ganzes zu erreichen. |  |

| Herausforderung 3: Problematik verschiede-ner Tool-Umgebungen Unterschiedliche Partner haben unterschiedliche Tool-Landschaften; Die Partner müssen zusammenarbeiten, da ein einzelnes Unternehmen nicht im Stande ist ein komplettes SiPoB-3D-System alleine erfolgreich zu entwickeln.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ziel 3: Erarbeitung eines flexiblen Ansatzes, der Zusammenarbeit verschiedener Tool-Umgebungen ermöglicht Installierung eines flexiblen Ansatzes, der die Zusammenarbeit zwischen den Unternehmen erlaubt, auch bei Nutzung unterschiedlicher Tools ("different tool eco-systems"); über einen Backbone auf offenen (Semi-) Standards, bevorzugter Weise auf XML, welches die Flexibilität bietet und unterschiedliche Datenformate/-schemas unterstützt (siehe CoSiP-Projekt)                          |  |

| Herausforderung 4: Vielfalt von Techologien                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Ziel 4: Erarbeitung der Möglichkeit, verschiedenste Technologien zu nutzen                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Version 1.00 | 07.02.2020 |

|--------------|------------|

|              |            |

Große Vielfalt an Technologien erfordert Tools, die eine optimale Auswahl an Technologien, Baugruppen, Montage- und Packaging-Technologien erlauben. Somit muss eine große Diversifikation vorgehalten und unterstützt werden.

Einsetzen von Entwicklungsblöcken, welche die neuesten Technologien beschreiben, wie TSV, TEV, Mikropumpen, etc., um 3D-SiP unter der Benutzung der aktuellsten Package Technologien (z.B. Chip Embedding) aufzubauen; die Partner werden in Abhängigkeit von ihrem Anwendungsportfolio verschiedene Baugruppen entwickeln.

#### Herausforderung 5:

#### Vermeidung teurer Hardware-Prototypen

Bedarf an Modellen für Technologiebaugruppen für die gesamte Chip-Packaging-PCB Simulation und Design-Regeln Überprüfung.

#### Ziel 5: Vermeidung teurer Hardwareprototypen durch korrekte Modelle

Mit korrekten Modellen können die Entwicklung und Fertigung von teuren Hardware-Prototypen vermieden werden; Simulationen mit Modellen auf optimaler Abstraktionsebene sind effizient und unterstützen die Detailmodelle in den jeweiligen Entwicklungsumgebungen und tragen damit wesentlich zur verbesserten Güte der Simulation bei. Resultierende dadurch Design-Regeln spiegeln Produzierbarkeit wieder.

#### Herausforderung 6:

#### Wärmemanagement

Wärme-Management angewendet auf Baugruppen

## Ziel 6: Erarbeitung einer Designumgebung für Wärmemanagement

Installieren einer Design-Umgebung für thermisches Design angewendet an den Baugruppen (e.g. TSV, TEV, Mikropumpen) in allen drei Domänen von SiPoB-3D

#### Herausforderung 7:

#### Materialauswahl

Richtige Materialauswahl und Integration deren Eigenschaften in Entwicklungsumgebung (Vielfalt von Materialien verursacht extreme Komplexität; es ist in der ITRS-Roadmap festgehalten, dass sich während der letzten Package-Materialien Jahren alle verändert haben und in den nächsten 10 Jahren wieder verändern werden).

## Ziel 7: Verbesserung des Know-Hows zu Materialdaten

Berücksichtigung der Physik von Materialien in der Entwicklungsumgebung. Materialien sind eng verknüpft mit der Zuverlässigkeit im Design. Wir müssen die Materialdaten besser kennen, insbesondere für hohe Frequenzen. Designregeln müssen die Zuverlässigkeit wiederspiegeln.

Ein wesentlicher Vorteil des geplanten Projekt besteht darin, dass die Arbeiten an der Design-Umgebung durch Hardware-Tests unter Einsatz von Spitzentechnologien, wie z.B. Chip-Embedding Technologien validiert werden. Dies beinhaltet beispielsweise die Verwendung von Micro-Bumps, TSV, oder das Chip-Embedding in Moldcompound (eWLB-Typ) oder in Laminate (Blade<sup>TM</sup>-Typ). Es wird erwartet, dass alle Projektpartner, deren Erfahrungen und Know-How sich ergänzen, hervorragende Ergebnisse erzielen werden, indem sie über drei Disziplinen zusammenarbeiten.

| Version 1.00 | 07.02.2020 |

|--------------|------------|

|--------------|------------|

| Abschlussbericht | SiPoB-3D    | Seite: 8 |

|------------------|-------------|----------|

|                  | 1.311.00-30 |          |

Die speziellen Ziele der beteiligten Institute der Fraunhofer Gesellschaft sind:

#### Tabelle 2: Übersicht der Ziele von Fraunhofer

In Hinblick auf die Institute und Forschungszentren <u>FhG IIS/EAS & IZM-ASSID</u> zielt SiPoB-3D auf folgendes ab

- Tiefgreifendes Verständnis der drei Domänen Chip, Gehäuse und Platine, was eine bessere Unterstützung der Entwickler ermöglicht

- Unterstützung des Projekts mit Design und Herstellung von Teststrukturen

- Aufbau einer weltweit führenden Infrastruktur und Know-How um die europäische Halbleiter-, Platinen- und Design-Tool-Industrie zu unterstützen und um Spitzenprodukte zu entwickeln

- Stärkung und Verbesserung von Ausbildung und Unterstützung für SiPoB-3D Entwicklung in der akademischen Gemeinschaft Europas

# I.3 Ausgangssituation und Voraussetzungen, unter denen das Vorhaben durchgeführt wurde

### I.3.1 Der Stand von Wissenschaft und Technik

Die wesentlichen Treiber für System-in-Package (SiP) Technologien sind anhaltende Miniaturisierung bei gleichzeitiger Integration von immer mehr Funktionalität und damit immer größerer Integrationsdichte. Die wachsende Komplexität der Mikrosysteme in Bezug auf neue Materialkombinationen und die Einführung neuer Aufbau- und Verbindungstechnologien führt zu großen Herausforderungen, sodass begleitendes Chip-Package-Co-Design immer wichtiger wird.

#### I.3.1.1 Aktuelle globale Situation (fehlende Fähigkeiten)

- Fehlende kohärente Chip/Package/Board-Co-Designumgebung für die 3D-Integration und System-in-Package, welche auch das Board beinhaltet. Das Projekt befasst sich mit Herausforderungen, die in der ITRS-Roadmap und in vielen der wichtigsten Konferenzen wie z.B. der DAC oder der DATE hervorgehoben werden.

- Fehlende Umgebung für eine kohärentes Package/Board Co-Design sowie ein Co-Design über die Unternehmensgrenzen hinaus.

- Der Design-Rule-Check für Packaging und Platinenaufbautechnik ist auf eine geringe Anzahl von Regeln limitiert. Diese Situation betrifft alle großen Firmen inklusive der "Packaging Foundries" in Asien und USA.

- Charakterisierung von Packaging-Materialien bei hohen Frequenzen (Milimeterwellen) ist eine große Herausforderung. Aktuell sind HF-Anwendungen auf einen kleinen Spezialmarkt, der sehr spezifisches Material und kostspielige Packaging-Lösungen verwendet, begrenzt. Wir müssen uns auf die Charakterisierung von Materialien vorbereiten und die Materialdaten im Hochfrequenzbereich in die Design-Umgebung integrieren.

- "Low power" Lösungen sind bisher auf Die- bis Systemebenen begrenzt; sie müssen erweitert werden, damit wichtige innovative Komponenten wie z.B. aktive Interposer, Multichip-Module und 3D-Stapel ("3D-Stacks") berücksichtigt werden. Dies wird die

| Version 1.00 |  | 07.02.2020 |

|--------------|--|------------|

|--------------|--|------------|

bisher durch thermische Verluste limitierte Integration ermöglichen und eine energieeffiziente Entwurfsmethodik für 3D Strukturen fördern.

- Untersuchung von multi-physikalischen Effekten, wie thermo-mechanisch and thermoelektrisch (thermischer IR-drop) ist notwendig

- Unvollständige SiP Design-Toolbox (z.B. Flip-Chip f2f Brick) um immer komplexere Systeme mit Chip, Package und Board zu entwerfen und aufzubauen.

- Optimierung der Geschwindigkeit für "Rapid-Prototyping" um den "Time-to-Market" zu verbessern.

- Innovative Design-Rule-Check-Strategie um eine Automatisierung von existierenden Regeln zu ermöglichen und um neue Regeln für komplexe Flip-Chip und 3D Aufbau Regeln einzuführen und zu programmieren. (Heutige Lösungen decken nur 40% der zwingend erforderlichen Regeln ab). Durch die Nutzung eines vollen Co-Design-Flows bekommen Firmen wie ST und Infineon, die den Chip und das Package in Eigenfertigung herstellen, einen Vorteil.

- Automatisiertes Tool für einen finalen Design-Rule-Check verbessert den "Time-to-Market" für komplexe Systeme.

- HF-Materialcharakterisierung ermöglicht eine genaue Modellierung für neue Anwendungen (Radar, kabellose HDMI-Verbindung, Motorsteuergeräte, usw.)

| Firma                                                                                   | Aktuelle Marktsituation und was heute fehlt                                                                                                                                                                                                                                                                                                                                                            |  |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fraunhofer<br>IIS/EAS and IZM-<br>ASSID                                                 | Erste Tools und Simulationsmethoden für die thermische, elektrisch sowie die gekoppelte elektro-thermische Simulation von Chip/ Package Lösungen sind etabliert sowie in industriellen Designflows installiert. Aktuell fehlt die Einbeziehung des Boards in diesen Betrachtungen. Dort liegt die Herausforderung vor allem in den divergenten Tools und                                               |  |

| IIS/EAS ist ein führendes Institut im Bereich Entwurfsmethoden und Design               | Methoden der beiden Domänen. So verwenden die Board-Designer zum Beispiel häufig Tools auf Basis des Betriebssystems Windows, während die Tools aus dem Bereich Chip/Package fast ausschließlich auf dem Betriebssystem Unix/Linux basieren. Auch die Arbeitsweisen sind unterschiedlich, so wird im Board Bereich fast ausschließlich mit graphischer Eingabe gearbeitet und kaum eine automatisierte |  |

| IZM-ASSID ist ein<br>führendes Institut im<br>Bereich 3D                                | Unterstützung angeboten während im Chip-Bereich häufig semi- oder vollautomatische Lösungen dominieren. Die Vereinigung dieser beiden Welten stellt eine große Herausforderung dar.                                                                                                                                                                                                                    |  |

| SystemIntegration inkl , Micro-Bumping, Redistribution Layer, TSV, Assemby und Stacking | Im Bereich des Face-to-Face Die Stackings sind Technologien existent, diese müssen aber immer an die konkreten Gegebenheiten der Chip-Technologie sowie der Verbindungselemente (Bumps) sowie der Assembly und Gehaüse Technologie angepasst werden.                                                                                                                                                   |  |

|                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                        |  |

#### I.3.2 Neuheit und Attraktivität des Lösungsansatzes

Das Teilvorhaben von Fraunhofer zielt in folgende Hauptrichtungen:

- Unterstützung des Designs von innovativen extrem miniaturisierten, hochintegrierten Produkten basierend auf 3D-IC und 3D-SiP mit Bezug zum Substrate durch effeizeinte Auswahl der richtigen Implementierung durch Toolunterstützung

- Verbesserung der Schnittstelle zwischen Chip, Package und Platine für ein kohärentes energieeffizientes Produktdesign durch eine einheitliche Beschreibungssprache

- Anpassung und Bewertung der Interconnectstrukturen (Bump) inkl Design-Rule Ableitung

- Stärkung von Kompetenz und Know-How durch Forschungszentren in Europa (Region Grenoble in Frankreich, Regionen Erlangen/Nürnberg/Regensburg und Dresden in Deutschland)

- Kohärenter Design-Workflow, der nicht nur den Chip und das Package, sondern auch das Board beinhaltet.

## I.4 Abgrenzung und Zusammenarbeit mit anderen Projekten

Das Projekt wird mit den französischen Partnern des CATRENE Projekts SiPoB-3D verbunden. Dabei wurden die Deliverables und Meilensteine direkt aufeinander abgestimmt, sodass möglichst viele Synergien erzeugt werden. Im französichen Konsortium sind neben STMicro-electronics in Crolles and Grenoble, DOCEA Power und Atrenta vertreten. Dazu kommen die zwei Forschungsinstitute CEA-LETI und die Universität Savoyen in Frankreich. Durch die Zusammenarbeit mit Firmen und Forschungseinrichtungen aus Frankreich erwarten wir star-ke Synergien, um das Chip-Package-Board Thema auf breiter aufzustellen. Das Gesamtpro-jekt SiPoB-3D wird auch auf europäischer Ebene von Infineon geleitet.

STMicroelectronics in Frankreich hat in den vergangenen Jahren eine exzellente, weltweit anerkannte, Kompetenz im Bereich SiP-Integration aufgebaut und war Partner mit Infineon in den abgeschlossenen Projekten CoSiP und 3DIM3. DOCEA Power bringt Kompetenz zu thermischen Verhalten von SiP, Atrenta bringt zusätzlich Systemkompetenz in SiPoB-3D mit ein. Auch der Austausch zwischen den französischen Forschungsinstituten und den deutschen Instituten bringt europäische Forschungs-Kompetenz auf höchstem Niveau zusammen, z.B. hinsichtlich mm-Wellen Design, Simulation und Modelling FAU LTE und die Universität Savoyen.

| Version 1.00 |  | 07.02.2020 |

|--------------|--|------------|

|--------------|--|------------|

| Abschlussbericht | SiPoB-3D | Seite: 11 |  |

|------------------|----------|-----------|--|

|                  |          |           |  |

## **II. Technische Ergebnisse**

In Anlehnung an das übergreifende CATRENE-Projekt SiPoB-3D ist der deutsche Projektteil in 5 Arbeitspakete (AP0-AP4) aufgeteilt, wobei die Nummerierung der Teil-APs kongruent übernommen wurde. Einzelne Teil-APs die in SiPoB-3D ausschließlich von französischen Partnern bearbeitet werden, wie z.B. AP4.1, sind benannt, aber nicht im Detail beschrieben. Die fünf Hauptarbeitspakete AP0 bis AP4 entsprechen der typischen Vorgehensweise bei einem solchen Co-Design Projekt.

Tabelle 3: Arbeitspakete

| Arbeits-<br>paket<br>Nr. | Titel des Arbeitspakets (AP)                                                                            | Arbeits-<br>paketleiter | Start-<br>monat | End-<br>monat |

|--------------------------|---------------------------------------------------------------------------------------------------------|-------------------------|-----------------|---------------|

| 0                        | Spezifikationen, Anforderungen, regelmäßige<br>Statusanalyse und Abgleich mit<br>internationalen Trends | Infineon                | 1               | 30            |

| 1                        | Simulation und Modellierung                                                                             | FAU LTE                 | 1               | 36            |

| 2                        | Flow-Integrations und Design Methoden                                                                   | IIS/EAS                 | 1               | 36            |

| 3                        | Design Flow Infrastruktur                                                                               | Infineon                | 1               | 36            |

| 4                        | Validierung durch Test-Beispiele und Prototypen                                                         | Continental             | 7               | 36            |

# II.1 Arbeitspaket 0: Spezifikationen, Anforderungen, regelmäßige Statusanalyse und Abgleich mit internationalen Trends

In Zusammenarbeit mit den anderen Projektpartnern wurde die Erarbeitung und Einigung auf die globalen Projektanforderungen abgeschlossen, um ein möglichst vollständiges Bild bzgl. der notwendigen Fortschritte in Methodik, Werkzeugen und Entwurfsumgebungen zu erfassen.

Am IIS/EAS fanden eine ausführliche Literaturrecherche und Absprachen mit den Toolherstellern statt, um die existierenden Schnittstellen zu evaluieren und die notwendigen Erweiterungen zu definieren.

## II.2 Arbeitspaket 1: Simulation und Modellierung

AP1.1: ERARBEITUNG UND ANALYSE DER TOOLLANDSCHAFT ZUR SIMULATION UND MODELLIERUNG

IIS/EAS hat die Untersuchung verschiedener Simulationswerkzeuge mit einem Fokus auf thermische und elektrische Simulation fortgeführt (z.B. ANSYS, COMSOL). Die Dokumentation der für SiPoB3D relevanten Toollandschaft ist fertiggestellt. Im Projektverlauf wird jetzt häufig auf die Tools der Firma CST zurückgegriffen.

AP1.2: ENTWICKLUNG VON MODELLEN FÜR DIE HETEROGENE CHIP/PACKAGE INTEGRATION

Der folgende Bericht beschreibt Modellierungs- und Simulationsmethoden und Überlegungen, die auf einem mikroelektronischen Hochleistungssystem für thermische Anwendungen mit bis zu 200 W anliegender Leistung implementiert werden können. Der Demonstrator besteht aus

| Version 1.00 |  | 07.02.2020 |

|--------------|--|------------|

|--------------|--|------------|

28 CP-Leistungswiderständen und 42 NTC-Thermistoren. Um eine sehr gute Wärmeableitung und Wärmeabfuhr für das System zu erreichen, werden ein Aluminiumkühlkörper, ein dünnes Wärmeleitmaterial (TIM) mit hervorragenden thermischen Eigenschaften und ein bürstenloser Gleichstromlüfter hinzugefügt. Auf diese Weise können wir sicherstellen, dass das thermische Gesamtprofil des Systems Temperaturwerte aufweist, die nicht erhöht sind und daher für die Robustheit, Haltbarkeit, Stabilität und Leistung des Systems nicht kritisch sind.

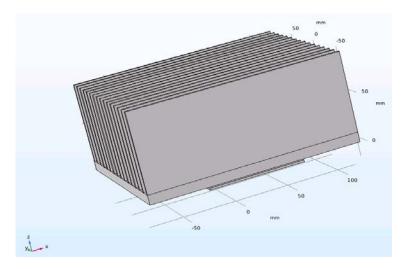

Die Abbildung zeigt die modellierte Version des thermischen Demonstrators, der bei FEM-Simulationen mit COMSOL Multiphsysics verwendet wird.

Der erste Schritt zur Modellierung solcher Systeme besteht darin, alle enthaltenen Komponenten mit einfachen Geometrien wie Blöcken, Zylindern usw. zu entwerfen. In unserem Fall wurden Blöcke für jede Struktur des Systems verwendet: die CP-Leistungswiderstände, NTC-Thermistoren und Leiterplatten (Kupferbahnen und Isolierkörper FR-4) und das TIM zwischen den Widerständen und dem Kühlkörper. Für die Modellierung von Kühlkörpern haben wir zusätzlich einen Block für die Basis und dann vertikale Blöcke für die Lamellen verwendet. Ein sehr wichtiger Schritt während der Modellierung ist das Anwenden der genauen Abmessungen für die Komponenten wie in den Datenblättern angegeben. Darüber hinaus können die PCB-Design-Software-Tools nützliche Informationen über die genaue Position der Systemelemente und die implementierten Abstände in Bezug auf ihre Position im Vergleich zu den benachbarten Komponenten liefern.

Anschließend müssen die Materialeigenschaften während der Simulation definiert werden. Die von den Komponentenherstellern bereitgestellten Datenblätter enthalten zusätzliche Informationen zu den verwendeten Materialien. Die Materialeigenschaften häufig verwendeter Materialien wie Kupfer, Silizium oder Aluminium werden von der Materialbibliothek von COMSOL Multiphysics bereitgestellt. Materialeigenschaften anderer Materialien, wie z. B. das TIM-Wärmeleitpad, müssen manuell angegeben werden.

In thermischen Simulationen sind wichtige Materialeigenschaften, die das Verhalten des Systems bestimmen, die Wärmeleitfähigkeit k, die Wärmekapazität Cp, die Materialdichte  $\rho$  und der konvektive Wärmeübertragungskoeffizient hc. Außerdem müssen der Umgebungstemperatur-Text und die Wärmeübertragungsrate Q angegeben werden. Letzteres wird von COMSOL Multiphysics automatisch anhand der Gleichung Q = hc \* (Text-T) berechnet.

Der nächste Schritt ist zu entscheiden, welche Art von Simulationen in Bezug auf die angewandten physikalischen Phänomene durchgeführt werden müssen. In unserem Fall

| Version 1.00 07.02.2020 |  |

|-------------------------|--|

|-------------------------|--|

Abschlussbericht SiPoB-3D Seite: 13

wollten wir das Verhalten der Wärme simulieren, die durch die Systemkomponenten fließt und wie der erzeugte Luftstrom das System kühlt. Fortan wurden die "Wärmeübertragung in Feststoffen" und "Wärmeübertragung in Flüssigkeiten" von COMSOL verwendet. Die thermischen Phänomene, die solche Verhaltensweisen und Wirkungen definieren, sind die natürlichen Wärmeübertragungsmechanismen.

Anschließend müssen die Randbedingungen des thermischen Systems definiert werden. In unserem Fall wurden die CP-Leistungswiderstände als Wärmequellen des simulierten Testsystems für eine angelegte Leistung von bis zu 200 W angegeben. Zusätzlich müssen Parameter wie der konvektive Wärmeübergangskoeffizient hc, die Umgebungstemperatur, die Startwerte und der Gesamtwärmestrom des Systems definiert werden.

Schließlich muss das Netz des Systems und des Lösers angegeben werden. Abhängig von der Maschengröße können wir verschiedene Maschen anwenden, von sehr groben bis zu sehr feinen. In jedem Fall werden die Größen der minimalen und maximalen Elemente automatisch vom Simulationsprogramm berechnet. In Bezug auf den verwendeten Löser gibt es eine große Auswahl: von statischen zu zeitabhängigen.

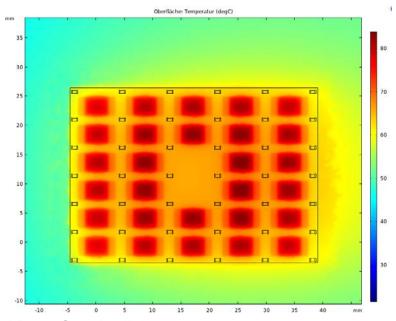

Die folgende Abbildung zeigt das Temperaturprofil des aktiven Bereichs des thermischen Testsystems unter 200 W angelegter Leistung. Die Abbildung wurde aus COMSOL Multiphysics extrahiert. Wir stellen fest, dass die Temperaturkarte der Widerstände ein einheitliches Profil aufweist und dass die maximale Temperatur des Systems etwa 83 ° C beträgt, wie durch die Farbe in der Temperaturskala auf der rechten Seite angezeigt wird. Durch den Einsatz effektiver Kühllösungen auf dem thermischen Demonstrator haben wir eine optimale Wärmeabfuhr und gleichmäßige Temperaturreduzierung für Hochleistungsanwendungen erreicht.

AP1.4: Standardisierung

IIS/EAS nimmt an Standardisierungsaktivitäten des Si2 teil. Zur Diskussion finden alle zwei Wochen Telefonkonferenzen statt.

| Version 1.00 |  | 07.02.2020 |

|--------------|--|------------|

|--------------|--|------------|

## II.3 Arbeitspaket 2: Flow-Integrations und Design Methoden

Neuartige 3D-Integrationstechnolgien werden die Anzahl potentiell verfügbarer Aufbauvarianten für SiPoB-3D-Designs vervielfachen. Damit einher geht ein größerer Aufwand bei der Auswahl der für eine konkrete Anwendung geeignetsten Variante. Dieser Schritt ist auch bekannt als Early Design Planning bzw. Early Design Exploration. Das Hauptziel dabei ist ein 3D die & Package Co-Design, um das vollständige SiPob3D-Gesamtsystem zu optimieren. Dazu ist es nötig, existierende EDA Entwurfsmethoden zu erweitern bzw. neu zu entwickeln um alle notwendigen Entwurfsdomänen (von Chip über Package zum Board) abdecken zu können.

AP2.1-2.5: Frühzeitige Design Abschätzungen, Systemdesign unter Berücksichtigung thermischer Effekte, Flow zur physikalischen Verifikation

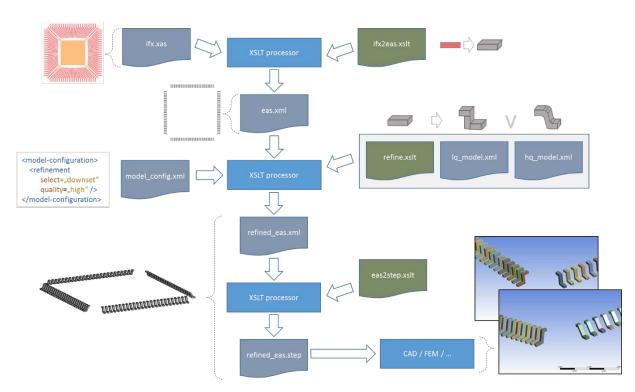

Basierend auf einem flexiblen XML-Beschreibungsformat, wurde ein Konzept zur frühen 3D-Entwurfsraumerkundung entwickelt. In Zusammenarbeit mit den anderen Partnern fand anhand unterschiedlicher Designbeispiele eine Evaluierung des neuartigen Ansatzes statt. Die Beispiele wurden dazu in der erwähnten XML-Beschreibungssprache beschrieben und weiter verarbeitet.

XSLT-Transformationen überführen die XML-basierte Designdaten Schritt für Schritt in ein vollständiges Simulationsmodel, welches sich direkt die entsprechenden in Simulationswerkzeuge (z.B. ANSYS) importieren lässt. Während des Ablaufs kann sich der Designer für den Detaillierungsgrad der Simulation entscheiden. Die dazu notwendigen Komponentenmodelle (zur Verfügung gestellt unterschiedlichen Genauigkeiten) werden mit der 3D-Beschreibung des Systems verknüpft.

| Version 1.00 |  | 07.02.2020 |

|--------------|--|------------|

|--------------|--|------------|

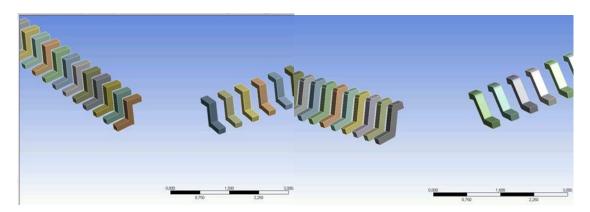

Unterschiedliche XML-Modelle der Lead-Komponente führen zu unterschiedlichen Simulationsmodellen (hier in ANSYS). Einfachere rektilineare Formen (links) und genauere S-Formen (rechts).

Die entwickelten XML-Modelle können leicht in komplexeren Packagevarianten eingesetzt werden, etwa in Chipstapeln. In diesem Fall ein Wirebond-Modell mittlerer Genauigkeit kam zum Einsatz, um zwei Nacktchip-Komponenten in einem Package zu verbinden (das Design entspricht dem Testaufbau, welches für die unter AP 1.2 beschriebenen thermischen Untersuchungen verwendet wurde).

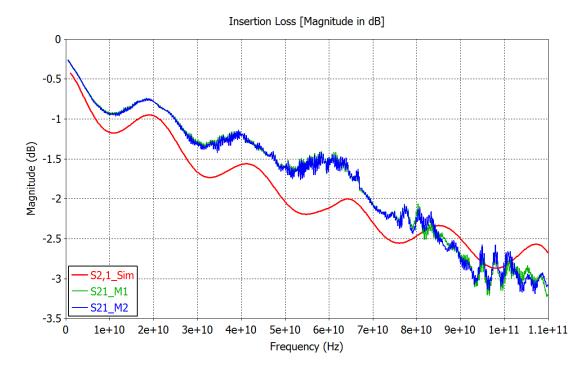

Im Projektzeitraum wurde weiterhin eine Methode zum Chip-Package CoDesign für Hochfrequenzsysteme entwickelt. Diese Ermöglicht es den Designer, direkt die Packagekomponenten sowie auch die Chipkomponenten gemeinsam zu betrachten und zu optimieren.

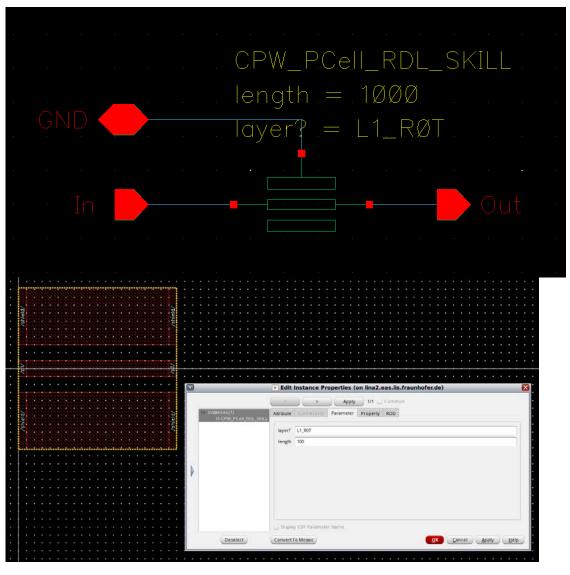

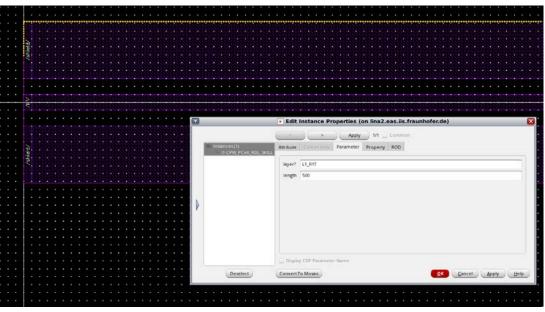

Als Beispiel wird hier eine Hochfrequenzleitungsstruktur angeführt. Für diese und andere Strukturen wurden sogenannte P-Cells entwickelt mit denen man den Entwurf auch im Package und an den Übergängen zum Chip und zum PCB vereinfachen kann.

Für die CPW wurden in der P-Cell eine Schematic, eine Layoutvorschrift, sowie präzise elektrische Modelle abgelegt. Siehe dazu die folgenden Bilder.

| Version 1.00 |  | 07.02.2020 |

|--------------|--|------------|

|--------------|--|------------|

Version 1.00 07.02.2020

Für diese Modelle werden Simulationsergebnisse und Messungen in Einklang gebracht und dieser Komponenten stehen den als charakterisierte Hochfrequenz-Elemente zur Verfügung.

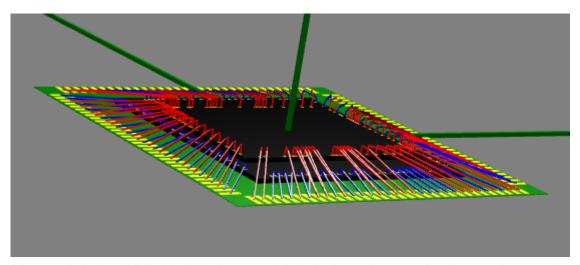

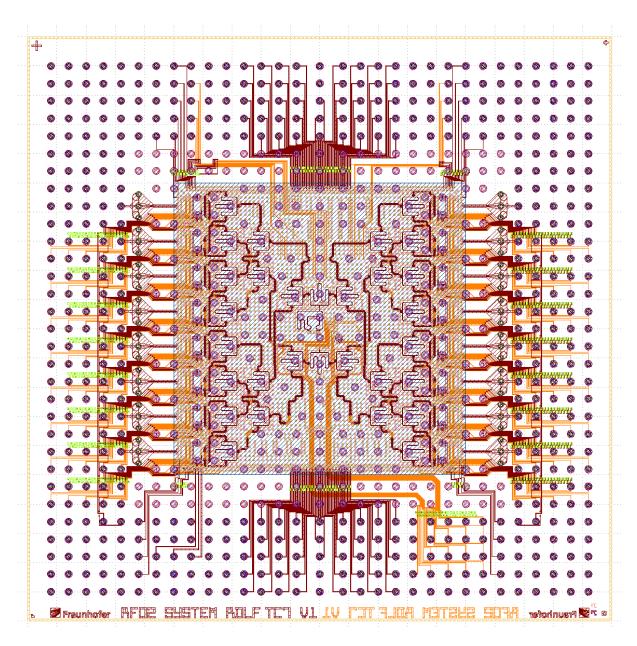

Damit wird der Entwurf sehr komplexer Chip-Package Systeme ermöglicht. Siehe dazu die nächste Abbildung. Aufgrund der Komplexität und der Anforderungen, die zum Beispiel für ein System für 60GHz 5G WiFi erforderlich sind, ist es unabdingbar, auf vorqualifizierte Komponenten zugreifen zu können.

| Version 1.00 |  | 07.02.2020 |

|--------------|--|------------|

|--------------|--|------------|

In diesem System werden gleichzeitig Hochfrequenz-Combiner/Splitter sowie die Zuleitungen zu den Antennen als auch die Spannungsversorgung und auch die Leitungen für den Digitalteil der Schaltung verlegt. Dieses ist nur durch die entwickelten Designmethoden möglich, da z.B. das Übersprechen zwischen verschiedenen Domainen verhindert werden muss.

## II.4 Arbeitspaket 3: Design Flow Infrastruktur

Im Projekt ist an diesem Arbeitspaket keine Beteiligung des IIS/EAS vorgesehen. Es wurden auch keine beratenden Tätigkeiten notwendig.

| Version 1.00 | 07.02.2020 |

|--------------|------------|

|              |            |

## II.5 Arbeitspaket 4: Validierung durch Test-Beispiele und Prototypen

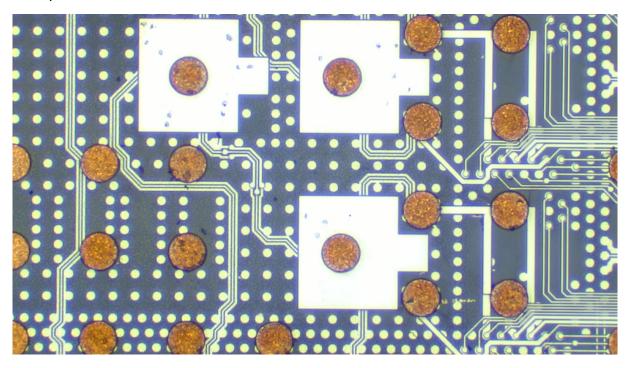

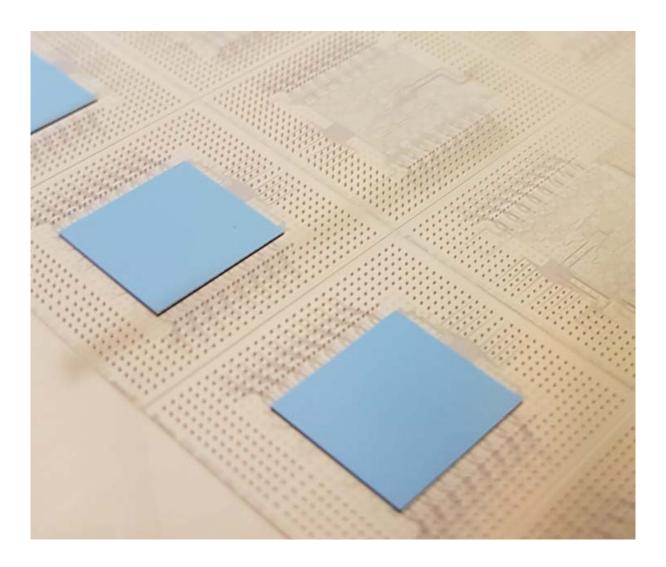

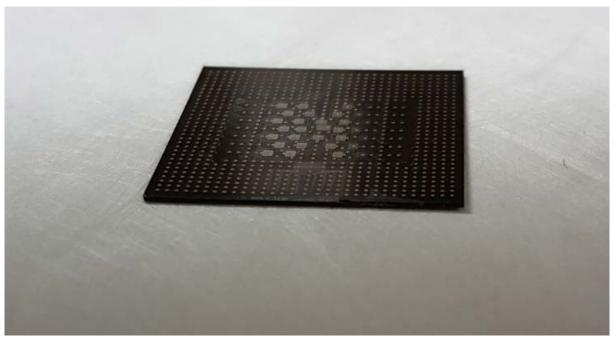

Testaufbauten wurden festgelegt und wurden entsprechend der Designdaten aus AP2 implementiert. Siehe dazu auch die nachfolgende Abbildung. Diese zeigt ein Hochfrequenzsystems bestehend aus einem aktiven IC und und einer Package-Realisierung, die die Integration von RF Komponten direkt auf dem Package-Substrat beinhaltet. Bild1 zeigt einen Ausschnitt aus den implementierten RF-Power-Splitter-Combiner auf dem Package-Substrat und Bild2 zeigt dabei das Substrat nach der Assemblierung des RF-ICs. Bild3 stellt das finale RF-System mit geringer Aufbauhöhe dar, das zur weiteren Einsatz auf eine Leiterplatte montiert wird.

| Version 1.00 | 07.02.2020 |

|--------------|------------|

|              |            |

| Abschlussbericht | SiPoB-3D  | Seite: 21 |

|------------------|-----------|-----------|

| 71.550776155     | L31P0B-3D | 00.00     |

## III. Verwertung und voraussichtlicher Nutzen

#### III.1 Ausgangslage

Ein wesentlicher Nutzen des Projekts ist der, dass die Partner die drei Domänen Chip, Gehäuse und Board abdecken. Die Partner können so voneinander lernen, optimale Systeme bestehend aus 3D-SiP und Board als Ganzes zu entwerfen. Die Halbleiter- und Systemhersteller (Infineon und Conti) werden die Methodologie und Entwurfskapazität in ihre interne Toolumgebung implementieren. Dies wird schnelleren, besseren und wirtschaftlicheren Entwurf von optimalen SiPs gemeinsam mit Kunden ermöglichen. Die Toolhersteller können durch CoSi-PoB ihre Toollandschaft an die Herausforderungen in Komplexität und Diversifikation bei 3D Integration vorbereiten. Die Boardhersteller können die Schnittstelle zwischen Chip/Package und Board erforschen und für ihre Kunden weiter optimieren. Dadurch werden optimierte Kompromisse für den Entwurf einen Systems/Subsystems bestehend aus Chips, Gehäuse und Board ermöglicht. Die Anwender Conti und Symeo bekommen die Fähigkeit zum verbesserten Entwurf elektronisches Systeme/Subsysteme durch besserer Verständnis der Komplexitäts- und Diversifikationsherausforderungen von 3D Systemen.

Zusammen mit den Industriepartnern werden die Ergebnisse in die Entwurfs- und Design Umgebung unter Berücksichtigung der technologischen Umsetzung für die einzelnen zukünftigen Produkte integriert, um die Entwicklungszeit und die Zeit bis zum Markteintritt ("Time to Market"), sowie die Skalierbarkeit der Produkte zu verbessern. Besserer Ablauf beim Co-Design einschließlich physikalischer Platzierungsregeln; schnellerer Markteintritt für Hochfrequenzprodukte dank besserer Simulation, verbesserte Abstimmung des Package Umrisses mit den Kunden Boards. Die Definition und Überprüfung des Package-Board co-Entwicklungsablaufs wird mit Leitkunden mit realen Fällen durchgeführt, um die Produktkosten mit minimaler Substratfläche und -lagen der Package und Systeme zu verifizieren. So-wohl die Designumgebung wie auch die 3D-SIP Technologie mit den zugehörigen Produkten wird vom SiPoB-3D profitieren.

Darüber hinaus ergeben sich für die Fraunhofer Gesellschaft (Fraunhofer Institute (IIS/EAS, IZM-ASSID) nachfolgend aufgeführte zusätzliche Gesichtspunkte.

Der gemeinnützige Auftrag der Fraunhofer Gesellschaft besteht darin, anwendungsorientierte Forschungsleistungen zu erbringen, welche einer unmittelbaren industriellen und applikativen Nutzung zugeführt werden können. 3D Systemlösungen sind als die Schlüsseltechnologie für die Realisierung von innovativen Systemlösungen und Produkten anzusehen.

Die beiden Fraunhofer Institute unterstützen im Rahmen des Projektes Firmen bei der Einführung der neuen Technologien im industriellen Anwendungsfeld. Das kann unter anderem durch den Cluster "Silicon Saxony" bzw den neuen Kompetenz-Center erfolgen. Aber auch über die sächsischen Grenzen hinaus werden vor allem auch mittelständische Firmen bei der Einführung dieser neuen Technologien beraten und unterstützt, da ansonsten die Risiken und Kosten für die Firmen teilweise nicht mehr tragbar sind.

Die am IZM-ASSID vorhandene Wafer-Level-Prozesslinie gestattet eine Verwertung der Ergebnisse bei der technischen Realisierung von SiP auf höchsten technologischem Niveau Dieses Element einer Integrationsplattform steht der Industrie und vor allem auch dem Mittelstand zur Verfügung, um innovative Produktideen zu erproben und umzusetzen.

Darüber hinaus werden die erwarteten Ergebnisse bei Fraunhofer im angewandten wissenschaftlichen Bereich genutzt, um die führende Stellung der beiden beteiligten Institute – im Bereich Design sowie Technologie - auszubauen.

Die Institute werden wichtiges Wissen ("Know How") aufbauen, das eine weltweit führende Ausbildung von Nachwuchs in Deutschland ermöglicht, was der Gesellschaft insgesamt nutzt.

| Version 1.00 |  | 07.02.2020 |

|--------------|--|------------|

|--------------|--|------------|

| Abschlussbericht | SiPoB-3D | Seite: 22 |

|------------------|----------|-----------|

|                  |          |           |

Die erzielten Ergebnisse können über bestehende Kooperationen zu Universitäten direkt in aktuelle und zukünftige Lehrveranstaltungen einfließen.

Damit ist sichergestellt, dass zukünftige Ingenieure schon heute mit den modernsten Technologien vertraut werden. Weiterhin können Diplom-, Bachelor- sowie Masterarbeiten zusammen mit den Universitäten durchgeführt werden. Bei Praktikas die durch die beiden Institute durchgeführt werden, können Studenten einen vertiefenden Einblick in diese zukunftsorientierten Technologien bekommen.

| Version 1.00 |  | 07.02.2020 |

|--------------|--|------------|

|--------------|--|------------|

## IV. Veröffentlichungen

- (1) Hopsch, Fabian, and Andy Heinig. "Processing and Memory Partitioning Enabled by Low Cost Flip-Chip Stacking." 2019 International Wafer Level Packaging Conference (IWLPC). IEEE, 2019

- (2) Heinig, Andy and Papaioannou, Dimitrios. "Simulation, verification, validation and testing of the thermal behavior of a high-power microelectronic test-system". 2019 ITherm. The Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems

- (3) Hopsch, Fabian, and Andy Heinig. "Antenna Integration Technologies for 5G Car-Application." 2018 International Wafer Level Packaging Conference (IWLPC). IEEE, 2018

- (4) Heinig, Andy and Papaioannou, Dimitrios. "Simulation, testing and implementation of temperature-reduction solutions on a high-power thermal demonstrator". 2018 ITherm. The Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems

- (5) Dittrich, Michael, Andy Heinig, and Fabian Hopsch. "Electrical characterization of a high speed HBM interface for a low cost interposer." 2018 IEEE 68th Electronic Components and Technology Conference (ECTC). IEEE, 2018.

- (6) Heinig, Andy and Papaioannou, Dimitrios. "Comparison between thermal simulations and experimental measurements on an advanced microelectronics test-system". 2017 ITherm. The Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems

- (7) Dittrich, Michael, et al. "Heterogeneous interposer based integration of chips with copper pillars and C4 balls to achieve high speed interfaces for ADC application." 2017 IEEE 67th Electronic Components and Technology Conference (ECTC). IEEE, 2017

| Version 1.00 |  | 07.02.2020 |

|--------------|--|------------|

|--------------|--|------------|