# HIGH THROUGHPUT LOW ENERGY INDUSTRIAL EMITTER DIFFUSION AND OXIDATION

M. Meßmer<sup>1</sup>, S. Lohmüller<sup>1</sup>, J. Weber<sup>1</sup>, A. Piechulla<sup>2</sup>, S. Nold<sup>1</sup>, J. Horzel<sup>1</sup>, A. Wolf<sup>1</sup>

<sup>1</sup>Fraunhofer Institute for Solar Energy System (ISE), Heidenhofstr. 2, 79110 Freiburg, Germany Phone: +49 761 4588-2287; e-mail: marius.messmer@ise.fraunhofer.de

<sup>2</sup>centrotherm international AG, Württembergerstr. 31, 89143 Blaubeuren, Germany

ABSTRACT: In this work, we investigate an approach of shortened low pressure (LP) POCl<sub>3</sub> diffusion and a high throughput thermal oxidation with stacked wafers to form the emitter for passivated emitter and rear cells (PERC). As the high temperature processes such as LP-POCl<sub>3</sub> diffusion and thermal oxidation account for a significant share of the manufacturing costs of PERC solar cells, our high throughput approach is very promising in terms of reducing both, production costs and energy consumption. Compared to state-of-the-art POCl<sub>3</sub> diffusion and low temperature oxidation, a 40% reduction of the specific costs and a 50% reduction of the energy consumption of the high temperature processes is feasible. We examine this approach by using four different adapted LP-POCl<sub>3</sub> diffusion processes using only the deposition phase (omitting further drive-in and in-situ oxidation) in combination with a "stack oxidation" process. Detailed characterization of the properties of the emitter and oxide layers after diffusion and after oxidation confirm a high quality emitter formation resulting in emitter dark saturation current density  $j_{0e} \approx 32 \text{ fA/cm}^2$  at  $R_{sh} \approx 183 \Omega/\text{sq}$ . Although the wafers are oxidized in a stack of horizontally oriented wafers touching each neighboring wafer, a very homogeneous oxide grows resulting in high passivation quality. Further, we find that this adapted emitter diffusion process allows for effective laser doping, which is promising for selective emitter formation.

Keywords: High throughput, wafer stacks, LP-POCl<sub>3</sub> diffusion, thermal oxidation, laser doping, silicon oxide

## 1 INTRODUCTION

The passivated emitter and rear cells (PERC) structure [1] gained a significant world market share in the last decade and will remain the mainstream technology in industry in the next years [2]. The process sequence for PERC solar cells usually contains two high temperature processes: A tube furnace diffusion using phosphorus oxychloride (POCl<sub>3</sub>) as liquid dopant source is the most common technology to form the emitter [2] and a thermal oxidation or anneal (also in a tube furnace) mostly serves as emitter passivation [3]. A cost of ownership (COO) analysis [4] shows, that these two processes account for a share of 11% of the PERC cell production costs. Energy conversion efficiencies  $\eta$  close to 22.5% are currently achieved for PERC solar cells with homogeneous emitters [5-7] using Czochalskigrown silicon (Cz-Si) wafers. In order to further increase  $\eta$ , the selective emitter has come back into focus in recent years [7-12] and its market share will increase significantly [2]. The selective emitter can be formed by, e.g., local laser doping from the phosphosilicate glass layer [13]. In order to further reduce the production costs of solar cells, a huge increase of the production tool throughput is predicted from 8000 wafers per hour in 2020 to 12000 wafers per hour in 2030 [2]. One option to realize a higher throughput is to increase the density of wafers per process by stacking the wafers during diffusion [14] or oxidation [15].

This work investigates an approach to reduce the specific costs and the energy consumption of the high temperature processes by decreasing the process time of the low pressure (LP) POCl<sub>3</sub> diffusion and by increasing the throughput during thermal oxidation. Hence, this study investigates the combination of shortened LP-POCl<sub>3</sub> diffusion processes applying only the deposition phase (omitting the drive-in phase) and a high throughput oxidation by stacking the wafers. We study the achievable charge carrier concentration profiles, the emitter recombination properties, the oxide growth, and

the combination with laser doping in comparison to a reference state-of-the-art high temperature process route.

## 2 STATE-OF-THE-ART EMITTER FORMATION

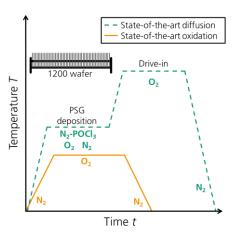

The state-of-the-art emitter formation technique for PERC cells is the tube furnace diffusion using  $POCl_3$  as liquid dopant source. This  $POCl_3$  diffusion often includes a deposition phase and a subsequent drive-in phase usually at elevated temperatures, as depicted in Figure 1. The deposition phase takes place on a first temperature plateau with nitrogen  $(N_2)$  flow through the  $POCl_3$  bubbler. Further, oxygen  $(O_2)$  gas flow is also active. The ratio between  $N_2$ - $POCl_3$  and  $O_2$  is moderate at this step, where the phosphosilicate glass / silicon dioxide  $(PSG/SiO_2)$  layer [16, 17] grows on the surface of the wafer (during this step, a moderate in-diffusion of phosphorus in the wafer takes also place), acting as a

**Figure 1:** Schematic illustration of the state-of-the-art tube furnace diffusion and oxidation processes as a function of the temperature *T* over time *t*. Throughput of both processes: 1200 wafer.

dopant source in the subsequent drive-in phase. There, a high  $O_2$  gas flow is often introduced to the process tube [8, 18, 19]. For this so-called in-situ oxidation the furnace is usually ramped up to temperatures above  $850^{\circ}$ C [20–22]. The goal of the in-situ oxidation is to decouple the phosphorus source from the silicon (Si) surface and thus to control or reduce phosphorus (P) in-diffusion from this source. Due to the increased throughput, the POCl<sub>3</sub> diffusion at low pressure (LP) [23] dominates in production. The LP-POCl<sub>3</sub> diffusion is typically performed in a horizontal quartz boat with vertical wafer arrangement and a typical wafer pitch of 2.38 mm with a throughput of 1200 wafers per run.

For boosting the efficiency of PERC solar cells, a selective emitter can be implemented on the front side of the PERC solar cell [7–12]. The approach often used for the realization of the selective emitter formation is laser doping from the  $PSG/SiO_2$  layer.

Emitter passivation for PERC cells mostly involves a thermal oxidation or annealing process [3]. Figure 1 depicts the course of a state-of-the-art thermal oxidation process. It features moderate temperatures [3, 6, 7] well below those of the diffusion process and it is also performed in a tube furnace similar to the diffusion process. During this process, gaseous  $N_2$  and  $O_2$  are used [24–26]. During oxidation in the  $O_2$  atmosphere a layer of silicon dioxide grows into the silicon surface. This layer serves as a surface passivation – in particular in combination with hydrogen rich capping layers. Such low temperature thermal oxidation processes do hardly affect the doping profile [6].

#### 3 APPROACH

The approach investigated in this paper applies an adapted LP-POCl<sub>3</sub> diffusion in combination with a high throughput oxidation by stacking wafers.

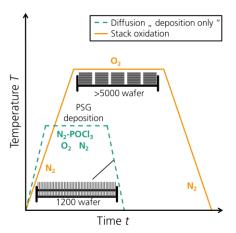

We adapt the LP-POCl $_3$  diffusion process by reducing the process to its PSG/SiO $_2$  layer deposition step, as depicted in Figure 2. In this step, only the PSG/SiO $_2$  deposition and a moderate in-diffusion of phosphorus take place. No drive-in or in-situ oxidation at elevated temperature is performed since the thermal treatment required for the further in-diffusion of phosphorus is transferred to the subsequent thermal

**Figure 2:** Schematic illustration of the approach in this work: Adapted tube furnace LP-POCl<sub>3</sub> diffusion and the high throughput thermal oxidation using wafer stacks (>5000 wafer).

oxidation process. This significantly reduces the process time for the LP-POCl $_3$  diffusion step compared to the state-of-the art diffusion, keeping the typical load of 1200 wafers per process.

During the thermal oxidation process in this work, the wafers are stacked horizontally on top of each other with their surfaces touching each other. Thus, the throughput may be significantly increased to more than 5000 wafers per run, as depicted in Figure 2. However, this high throughput oxidation process features a higher temperature and longer process time compared to the state-of-the-art process. Stack diffusion [14] and stack oxidation [15] processes have been proposed and industrially applied earlier. The high throughput thermal oxidation process with stacked wafers is simply referred to as "stack oxidation" below.

The PERC solar cell fabrication sequence for our approach with selective emitter would be analogous to the state-of-the-art sequence, only the diffusion and thermal oxidation processes are adapted.

## 4 COST CALCULATION

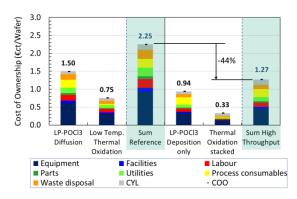

We calculate the cost of ownership (COO) for our state-of-the-art process route for PERC solar cells with LP-POCl<sub>3</sub> diffusion and low temperature thermal oxidation, as well as for the novel approach proposed in this paper. The calculations were conducted with the "SCost" COO model [4], which is aligned to the SEMI standards E35 [27] and E10 [28]. The model input data is based on industrial equipment and process parameters. The results are depicted in cost split charts in Figure 3. For this calculation the wafer throughputs mentioned in section 3 are assumed. By shortening the LP-POCl<sub>3</sub> process, the COO for this process reduces from 1.50 €ct/Wafer to 0.94 €ct/Wafer (same amount of 1200 wafer per process). Comparing the thermal oxidation processes, the state-of-the-art low temperature thermal oxidation features a shorter process time and a lower thermal budget than the high throughput thermal oxidation, but the latter has a much higher load with 5000 wafers per process assumed here. This results in a 3.2 times higher throughput for the stack oxidation. Also taken into account is the increased investment cost for the

**Figure 3:** Cost of ownership (COO) calculation for the state-of-the-art process route with LP-POCl<sub>3</sub> diffusion (1<sup>st</sup> bar) and low temperature thermal oxidation (2<sup>nd</sup> bar), as well as for the approach presented in this paper with LP-POCl<sub>3</sub> only deposition diffusion (4<sup>th</sup> bar) and thermal oxidation using stacked wafers (5<sup>th</sup> bar). The sum of the COO for the state-of-the-art process route is stated in the 3<sup>rd</sup> bar and for the new approach in the 6<sup>th</sup> bar.

equipment which is assumed to be 30% higher for the high throughput thermal oxidation tool due to adapted automation and increased mechanical strength of the paddle which is necessary for the higher load. Nevertheless, the COO reduces from 0.75 \( \)\text{Ct/Wafer} for the low temperature oxidation to 0.33 \( \)\text{Ct/Wafer} for the stack oxidation. In total, the COO for both thermal processes reduces from 2.25 \( \)\text{Ct/Wafer} with the presented approach. This is a reduction of the COO by 44%. For the specific power consumption, taking into account the heat capacity of the Si wafers, a reduction of approximately 50% is expected due to reduced heat losses.

#### 5 EXPERIMENT

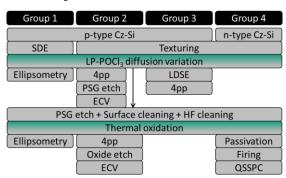

In this investigation, four groups of test samples are manufactured, depicted in Figure 4, for the characterization of the  $PSG/SiO_2$  and thermal oxide growth (group 1), of the sheet resistance  $R_{\rm sh}$  and charge carrier concentration profiles before and after oxidation (group 2), of laser doping (group 3) and of the passivation quality (group 4). Therefore, M2 p-type and n-type Cz-Si wafers serve as starting material for group 1 to 3 and group 4, respectively. Either a saw damage etch (SDE) or alkaline texturing is performed for group 1 or for groups 2 to 4, respectively, before four different LP-POCl<sub>3</sub> diffusion processes only with deposition step (see section 5.1) form the emitter and the stack layer system of  $PSG/SiO_2$ .

**Figure 4:** Experiment plan for the test samples investigated in this work.

For group 1, we perform ellipsometry measurements using a laser ellipsometer after the LP-POCl<sub>3</sub> diffusion to measure the layer thickness of the PSG/SiO<sub>2</sub> layer stack that forms during the POCl<sub>3</sub> deposition. The ellipsometry measurement consists of 25 measurement points distributed over the wafer surface, assuming a refractive index of 1.5 as proposed in Ref. [17].

Some test samples of group 2 are characterized by means of the four-point-probe (4pp) technique to determine the sheet resistance  $R_{\rm sh}$ . For the determination of the charge carrier concentration profiles, the electrochemical capacitance-voltage (ECV) measurement [29] is used after PSG etching to yield the charge carrier concentration as a function of the depth. The surface area factor is adjusted such that the  $R_{\rm sh}$  calculated from charge carrier concentration profile matches the  $R_{\rm sh}$  measured with 4pp close to the ECV measurement spot [30, 31].

The test samples of group 3 are partly laser-doped

(full area test fields, 1x1 cm²) using a green ns laser (532 nm wavelength) and three different laser parameter sets "P1" to "P3" with increasing laser pulse energy  $E_p = \{47 \ \mu\text{J}; 52 \ \mu\text{J}; 62 \ \mu\text{J}\}$ . Some areas on the wafer remain untreated by the laser and serve as reference. The test samples are also characterized by 4pp to determine  $R_{\text{sh}}$  after laser doping.

The following  $PSG/SiO_2$  etch in hydrofluoric acid (HF) removes the dopant source for groups 1, 3 and 4, and the remaining wafers in group 2. Then, for all groups, a wet chemical cleaning step oxidizes a very shallow part of the highly doped emitter surface. The grown oxide is then removed again in diluted hydrofluoric acid (HF) prior to the thermal oxidation process where the wafers are stacked on top of each other (see section 5.2).

For group 1, ellipsometry measurements are repeated after thermal oxidation to determine the  $SiO_2$  layer thickness using the same procedure as described above. For group 2, 4pp measurements determine  $R_{\rm sh}$  after thermal oxidation. Subsequently, the grown  $SiO_2$  is etched before the charge carrier concentration profiles are determined using ECV.

Group 4 is further processed by depositing a silicon nitride  $SiN_x$  on both sides using plasma enhanced chemical vapour deposition (PECVD). Subsequent to the following fast firing step for the activation of the hydrogen passivation, these symmetrical test samples are characterized using a quasi-steady-state photo conductance (QSSPC) measurement to determine the effective lifetime at five different spots per sample. Then, the emitter dark saturation current density  $j_{0e}$  is obtained by the procedure described in Ref. [32].

# 5.1 LP-POCl<sub>3</sub> diffusion

Table 1 shows process parameters of the PSG/SiO<sub>2</sub> deposition step for the reference process "Ref" and for the processes "Dep. T1" to "Dep. T4" investigated in this work. Our diffusion processes are developed in a LP-POCl<sub>3</sub> tube furnace from centrotherm international AG. The reference process "Ref" features a deposition temperature of  $T_{\text{dep}} = 800^{\circ}\text{C}$  (deposition temperatures are set temperatures in the tube furnace) while the gas flow ratio between N<sub>2</sub>-POCl<sub>3</sub> and O<sub>2</sub> is 0.26. This reference process benefits from a subsequent in-situ oxidation at elevated temperature and a second deposition phase at deposition temperature  $T_{\rm dep,2} > T_{\rm dep}$  to increase the amount of phosphorus within the PSG layer [16, 17]. The target of the variation in the novel LP-POCl<sub>3</sub> diffusion processes "Dep. T1" to "Dep. T4" is to have a sufficient high reservoir of phosphorus atoms incorporated in the silicon wafer as well as in the PSG layer immediately after the deposition step. This is beneficial for the further in-diffusion of the phosphorus atoms during the following laser doping process as well as for their redistribution during the subsequent thermal oxidation process. Therefore, we increased the N2-POCl3/O2 ratio

| Process | Temperature $T / {}^{\circ}C$ | N <sub>2</sub> -POCl <sub>3</sub> /O <sub>2</sub> ratio |

|---------|-------------------------------|---------------------------------------------------------|

| Ref     | 800                           | 0.26                                                    |

| Dep. T1 | 805                           | 0.80                                                    |

| Dep. T2 | 800                           | 0.80                                                    |

| Dep. T3 | 798                           | 0.80                                                    |

| Dep. T4 | 795                           | 0.80                                                    |

**Table 1:** Process parameters during PSG/SiO<sub>2</sub> deposition step of the LP-POCl<sub>3</sub> diffusion processes (see also Figure 2 for the process flow).

compared to the reference process to 0.8. We varied the deposition temperature of the PSG/SiO<sub>2</sub> deposition processes, decreasing from  $T_{\rm dep}=805\,^{\circ}{\rm C}$  for "Dep. T1" to  $T_{\rm dep}=795\,^{\circ}{\rm C}$  for "Dep. T4".

#### 5.2 Thermal oxidation

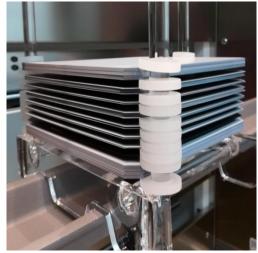

In combination with the reference diffusion process "Ref", described in section 5.1, a reference thermal oxidation featuring moderate temperature is used. In this low temperature thermal oxidation the wafers are vertically orientated in a conventional quartz boat. The adapted diffusion processes "Dep. T1" to "Dep. T4" are combined with a high throughput thermal oxidation process that is conducted within an industrial tube furnace also from centrotherm international AG. A special quartz boat is used as depicted in Figure 5. Here, the wafers are stacked horizontally on top of each other. This quartz boat uses the common paddle for automated loading and unloading of the process chamber. The wafers are loaded manually to the quartz boat, but automatization of this wafer loading process is conceivable. With quartz rings, it is possible to separate groups of wafers in this quartz boat. Free standing horizontal samples separated using these quartz rings serve as reference samples.

**Figure 5:** Experimental set-up for the stack oxidation process using a horizontal industrial tube furnace. Different groups of horizontally stacked wafers in this quartz boat are separated by quartz rings.

The process flow of the oxidation is as follows (see also Figure 2): The process atmosphere inside the tube is exchanged right after loading by evacuating and subsequent filling with nitrogen  $(N_2)$ . The temperature is ramped up in  $N_2$  to the plateau temperature. When reaching the plateau temperature, the atmosphere switches to pure oxygen  $(O_2)$  by using the vacuum pump. Before cool-down, the atmosphere is again changed to  $N_2$ .

#### 6 RESULTS

## 6.1 LP-POCl<sub>3</sub> diffusion processes

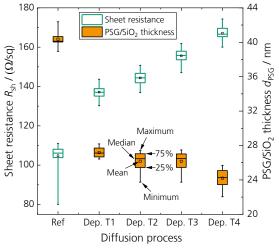

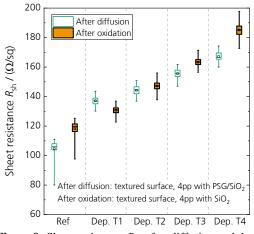

Figure 7 shows the sheet resistance  $R_{\rm sh}$  and the PSG/SiO<sub>2</sub> layer thickness  $d_{\rm PSG}$  for the diffusion processes characterized as described in chapter 5. The sheet resistance  $R_{\rm sh}$  of the reference process "Ref" is found to be  $R_{\rm sh} = (105 \pm 6)~\Omega/{\rm sq}$ . For diffusion process "Dep. T1"

(highest  $T_{\text{dep}} = 805^{\circ}\text{C}$ ), the sheet resistance is  $R_{\rm sh} = (137 \pm 3) \Omega/{\rm sq}$ and increases  $R_{\rm sh} = (167 \pm 3) \,\Omega/\text{sq}$  with decreasing  $T_{\rm dep} = 795 \,^{\circ}\text{C}$  for "Dep. T4". Further, the reference process features a thick PSG/SiO<sub>2</sub> with  $d_{PSG} = (40 \pm 1)$  nm. In contrast, increasing  $T_{\rm dep}$  and omitting the subsequent heat-up and the in-situ oxidation after the deposition step for the processes "Dep. T1" to "Dep. T4" reduces  $d_{PSG}$  significantly to  $(24 \pm 1)$  nm  $< d_{PSG} < (27 \pm 1)$  nm. The reduction of  $T_{dep}$ from process "Dep. T1" to process "Dep. T4" affects the PSG/SiO<sub>2</sub> thickness only slightly.

**Figure 7:** Sheet resistance  $R_{\rm sh}$  (4pp with PSG/SiO<sub>2</sub> layer on textured surfaces, 100 measurement points) and PSG/SiO<sub>2</sub> thickness  $d_{\rm PSG}$  (ellipsometry on SDE surfaces, 25 measurement points) for the different diffusion processes.

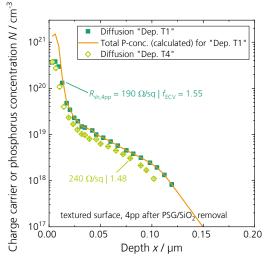

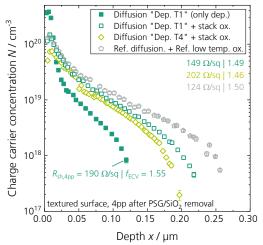

Figure 6 shows a selection of the ECV measurements. For reasons of clarity, only the charge carrier concentration profiles of diffusion "Dep. T1" and "Dep. T4" are shown. The  $R_{\rm sh}$  values given in the graph are higher than the ones obtained in Figure 7 as  $R_{\rm sh}$  is measured in the wafer center after PSG etching in Figure 6 while in Figure 7, it is measured over the whole wafer surface before PSG etching. The charge carrier concentration profiles show a surface concentration  $N_{\rm s}$  of

**Figure 6:** Charge carrier concentration profiles obtained by ECV technique after  $PSG/SiO_2$  etch on textured surface in the wafer center, scaled to locally measured  $R_{sh}$ . Further, the total phosphorus concentration calculated from the ECV profile according to Ref.[33].

$N_{\rm s} \approx 4.10^{20} \, {\rm cm}^{-3}$  for both processes. The profile depth  $x_{\rm d}$ extracted at a concentration  $N = 1 \cdot 10^{17}$  cm<sup>-3</sup> is found to be  $x_{\rm d} \approx 150$  nm for process "Dep. T1" and slightly less for "Dep. T4". According to Ref. [33], we calculate the expected total amount of phosphorus from the electrically active phosphorus concentration determined with ECV (also shown in Figure 6). The difference between the predicted total phosphorus concentration profile and the measured charge carrier concentration profile gives the share of electrically inactive phosphorus. At the surface and in the surface near region, this difference in the concentration is quite high. The expected total phosphorus surface concentration  $N_{s,total}$  increases significantly by about  $N_{\text{s,total}} = 1.5 \cdot 10^{21} \text{ cm}^{-3}$  comp a factor three compared to the concentration from ECV. The high amount of electrically inactive phosphorus will be activated in the following thermal oxidation step, which will be discussed in section 6.3.

#### 6.2 Laser doping processes

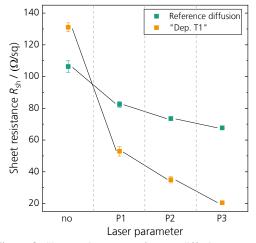

In this section, we investigate the performance of diffusion process "Dep. T1" in comparison to the reference process "Ref" regarding the change in sheet resistance  $R_{\rm sh}$  by laser doping. Figure 8 shows the  $R_{\rm sh}$ measured for the laser-doped test fields (applying the laser parameter set "P1"-"P3") and for the test fields without laser doping ("no"). For the reference diffusion "Ref",  $R_{\rm sh}$  decreases from  $R_{\rm sh} \approx 107~\Omega/{\rm sq}$  without laser processing down to  $R_{\rm sh} \approx 70 \ \Omega/{\rm sq}$  when applying laser parameter set "P3" with the highest pulse energy. In contrast, the PSG/SiO<sub>2</sub> deposition process "Dep. T1" starts at  $R_{\rm sh} \approx 130 \ \Omega/{\rm sq}$  without laser processing and  $R_{\rm sh}$ reduces down to  $R_{\rm sh} \approx 21~\Omega/{\rm sq}$  when laser parameter set "P3" is applied. The combination of low power laser parameter set "P1" with the PSG/SiO2 deposition process "Dep. T1" results in  $R_{\rm sh} \approx 53~\Omega/{\rm sq}$ , which is still lower than  $R_{\rm sh} \approx 67~\Omega/{\rm sq}$  reached by the reference diffusion "Ref" applying a higher laser power "P3". Starting with a higher  $R_{\rm sh}$  (without laser doping) for diffusion "Dep. T1" compared to the reference process, a lower  $R_{\rm sh}$  is reached with the same laser parameter set in comparison to the reference process. A reason for this could be the thinner PSG/SiO<sub>2</sub> layer for "Dep. T1" compared to"Ref" (see Figure 7). Lohmüller et. al. [16] showed that a diffusion process with only performing a deposition step features a

**Figure 8:** Sheet resistance  $R_{\rm sh}$  for two diffusion processes ("Reference" and diffusion process "Dep. T1") after laser doping with parameters "P1" – "P3" and without laser doping "no". The solid lines serve as a guide to the eye.

thin intermediate  $SiO_2$  layer. Their work showed that thinner intermediate oxide layers correlate with enhanced  $R_{\rm sh}$  reduction by laser doping [34]. Further, the activation of already incorporated electrically inactive phosphorus [35], see again Figure 6, could be a reason for the more effective doping observed in this work.

## 6.3 Thermal oxidation processes

This section discusses the results characterization of the thermal oxidation process. Figure 9 depicts the sheet resistances  $R_{\rm sh}$  after the thermal oxidation processes. Here, the reference diffusion "Ref" with  $R_{\rm sh} = (105 \pm 6) \,\Omega/\text{sq}$  is combined with the reference low temperature thermal oxidation which slightly increases  $R_{\rm sh}$  to  $R_{\rm sh} = (118 \pm 5) \,\Omega/\text{sq}$ . For the PSG/SiO<sub>2</sub> deposition processes "Dep. T1" to "Dep. T4" in combination with the stack oxidation, the  $R_{\rm sh}$  increases constantly with decreasing diffusion temperature, as expected. Interestingly, the stack oxidation decreases  $R_{\rm sh}$ for diffusion "Dep. T1" (highest  $T_{\rm dep}$ ) by  $\Delta R_{\rm sh} \approx 7~\Omega/{\rm sq}$  to  $R_{\rm sh} = (130 \pm 2) \,\Omega/\text{sq}$ . In contrast to that, the stack oxidation process clearly increases  $R_{\rm sh}$  for the deposition processes with lower  $T_{\text{dep}}$ , especially "Dep. T4". Here, an increase of  $\Delta R_{\rm sh} \approx 18 \, \Omega/{\rm sq}$  to  $R_{\rm sh} = (185 \pm 4) \, \Omega/{\rm sq}$  is observable after the stack oxidation process.

**Figure 9:** Sheet resistance  $R_{\rm sh}$  after diffusion and thermal oxidation process, measured with 4pp (100 measurement points over the wafer).

Figure 10 shows selected charge carrier concentration profiles for the different diffusion processes after the thermal oxidation processes. For diffusion "Dep. T1", the profile after diffusion from Figure 6 is also included. The reference sequence with diffusion "Ref" and low temperature oxidation results in a surface concentration  $N_{\rm s} \approx 1.5 \cdot 10^{20} \, {\rm cm}^{-3}$  and a depth of  $x_{\rm d} \approx 250 \, {\rm nm}$ . For "Dep. T1", the surface concentration decreases from  $N_{\rm s} \approx 4 \cdot 10^{20} \, {\rm cm}^{-3}$  after diffusion to  $N_{\rm s} \approx 1.5 \cdot 10^{20} \, {\rm cm}^{-3}$  after the stack oxidation, while the depth increases to  $x_{\rm d} \approx 200$  nm. The profile for the combination of the adapted LP-POCl<sub>3</sub> diffusion "Dep. T1" only with deposition step and the stack oxidation is very similar to the one of the reference process. From "Dep. T1" to "Dep. T4" after stack oxidation, the surface concentration decreases slightly, as well as the depth of the charge carrier concentration profiles. Calculating the total amount of phosphorus for "Dep. T1" after the stack oxidation according to Ref. [33], shows that the oxidation significantly reduces the expected total phosphorus

**Figure 10:** Charge carrier concentration profile obtained by ECV technique after  $SiO_2$  etch on textured surface. Filled green squares represent the doping profile already depicted in Figure 6. The empty symbols show the doping profiles after the stack oxidation.

concentration at the surface to  $N_{\rm s,total} \approx 2 \cdot 10^{20} \, {\rm cm}^{-3}$  (not shown here), which is only slightly higher than the active charge carrier concentration (compare Figure 10).

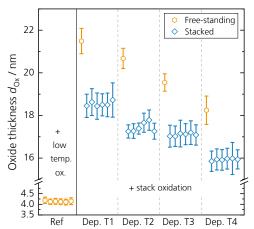

The respective oxide layer thicknesses  $d_{Ox}$  grown on the silicon surfaces during the thermal oxidation processes are measured using ellipsometry and depicted in Figure 11. The reference diffusion with the low temperature thermal oxidation yields an oxide thickness of  $d_{\text{Ox}} \approx 4$  nm with excellent homogeneity over the wafer and over the process boat. In contrast, the stacked oxidation yields much thicker layers, partly due to the higher oxidation temperature. Additionally to the wafers oxidized as a stack, single free-standing wafers in horizontal position are investigated. The oxide thickness of the free-standing samples decreases constantly from "Dep. T1"  $d_{Ox} = (21.5 \pm 0.6) \text{ nm}$ for  $d_{\rm Ox} = (18.2 \pm 0.7)$  nm for "Dep. T4". The oxide growth depends on the phosphorus concentration at the surface  $N_s$  [36, 37]: The higher the concentration, the higher the oxide growth rate. "Dep. T1" shows the highest surface concentration (compare Figure 10), which leads to the thickest oxide (see Figure 11). The surface concentration decreases with decreasing deposition temperature from

**Figure 11:** Silicon oxide layer thicknesses on SDE surface measured with ellipsometry (25 measurement points over the wafer) after diffusion and thermal oxidation.

"Dep. T1" to "Dep. T4" (see Figure 10) and so does the oxide thickness (see Figure 11). Furthermore,  $d_{\rm Ox}$  decreases as well for the stacked samples from  $d_{\rm Ox}\approx 18$  nm for "Dep. T1", over  $d_{\rm Ox}\approx 17$  nm for "Dep. T2" and "Dep. T3" to  $d_{\rm Ox}\approx 16$  nm for "Dep. T4". The oxide thickness is only about 2 to 3 nm lower for wafers oxidized as stack compared to the free standing ones. Thus, the availability of  $O_2$  within the gap between the stacked wafers is sufficient to grow a uniform oxide layer. The homogeneity over the wafer is excellent with standard deviations below 1 nm as well as the homogeneity over the stack with a standard deviation of about 0.5 nm.

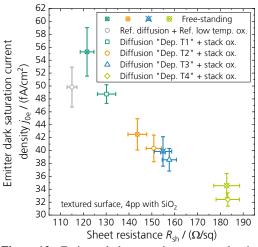

#### 6.4 Emitter recombination

Figure 12 shows the emitter dark saturation current density  $j_{0e}$  as a function of the sheet resistance  $R_{sh}$  for the reference process with state-of-the-art diffusion and low temperature thermal oxidation as well as for free-standing and stacked samples with adapted diffusion and stack oxidation. It has to be mentioned that all samples were coated with a SiN<sub>x</sub> layer of similar thickness, although the underlying oxide layer is of different thickness (compare Figure 11). The reference process results in  $j_{0e} = (50 \pm 3) \text{ fA/cm}^2 \text{ at } R_{sh} = (115 \pm 2) \Omega/\text{sq.}$  The  $j_{0e}$  for the high throughput approach decreases with increasing  $R_{\rm sh}$  and decreasing  $N_{\rm s}$ . For free-standing samples  $j_{0\rm e}$ decreases continuously from  $j_{0e} = (55 \pm 4) \text{ fA/cm}^2$  $R_{\rm sh} = (122 \pm 3) \,\Omega/\text{sq}$  for diffusion "Dep. T1"  $j_{0e} = (35 \pm 2) \text{ fA/cm}^2$  at  $R_{sh} = (183 \pm 6) \Omega/\text{sq}$  for diffusion "Dep. T4". A similar behavior is visible for the stacked samples, where  $j_{0e}$  decreases from  $j_{0e} = (49 \pm 1)$  fA/cm<sup>2</sup> at  $R_{\rm sh} = (130 \pm 4) \,\Omega/\text{sq}$  for diffusion "Dep. T1"  $j_{0e} = (32 \pm 1) \text{ fA/cm}^2 \text{ at } R_{sh} = (183 \pm 5) \Omega/\text{sq for diffusion}$ "Dep. T4". Comparing stacked and free standing samples,  $j_{0e}$  is higher for the free standing samples, but  $R_{\rm sh}$  is lower at the same time, thus no specific impact of the stacking on  $j_{0e}$  is observed. The low  $j_{0e}$  values achieved for the high throughput approach with adapted LP-POCl<sub>3</sub> diffusion (featuring only the deposition step) and stack oxidation suggests that the amount of highly recombinative electrically inactive phosphorus after the PSG/SiO<sub>2</sub> deposition process seems to be effectively reduced during the thermal oxidation process, as predicted using the model from Ref. [33] (see above).

To conclude, with the approach investigated in this work similar emitter properties can be achieved as for the

**Figure 12:** Emitter dark saturation current density for free-standing and stacked test samples.

state-of-the-art approach. However, the contacting of these emitters using screen-printed silver pastes and the integration into the PERC cell process needs to be proven additionally.

#### 7 SUMMARY AND CONCLUSION

Shortening the process time of the LP-POCl $_3$  diffusion by omitting any drive-in step as well as increasing the throughput during thermal oxidation from 1200 to more than 5000 wafers per process by stacking the wafers, results in a reduction of the specific costs by 44%. Furthermore, the specific power consumption is reduced by approximately 50%.

The charge carrier concentration profile of our high throughput approach is very similar to the one of a state-of-the-art LP-POCl<sub>3</sub> diffusion with low temperature oxidation, which features a surface concentration of about  $10^{20}\,\rm cm^{-3}$  and a profile depth in the range of 200 nm to 250 nm. The electrically inactive phosphorus available after the deposition step of the adapted LP-POCl<sub>3</sub> diffusion is reduced significantly due to the subsequent stack oxidation process. This is confirmed by yielding high-quality phosphorus emitters with emitter dark saturation current density  $j_{0e}$  values on textured surface between  $j_{0e}\approx 50~\rm fA/cm^2~(SiO_2/SiN_x~passivated$  and fired) at emitter sheet resistance  $R_{\rm sh}\approx 130~\Omega/\rm sq$  and  $j_{0e}\approx 35~\rm fA/cm^2$  at  $R_{\rm sh}\approx 180~\Omega/\rm sq$  for the high throughput approach. The results also show that stacking of wafers during thermal oxidation yields similar values for  $j_{0e}$  compared to free standing wafers.

The low  $j_{0\rm e}$  values achieved for the high throughput approach also suggest that a thermal oxide with high passivation quality is grown on the wafer surfaces within the stack. The thickness of this oxide is found to be  $16~{\rm nm} < d_{\rm Ox} \le 19~{\rm nm}$  with an excellent homogeneity (standard deviation of 1 nm).

Implementing a laser doping process between diffusion and oxidation for realizing selective emitters shows that a more effective doping is possible for the adapted LP-POCl<sub>3</sub> diffusion process that features only the deposition step, than for the reference LP-POCl<sub>3</sub> diffusion process.

In summary, this high throughput approach with short LP-POCl<sub>3</sub> diffusion and stack oxidation is very promising for passivated emitter and rear cells processing featuring homogeneous as well as selective emitters.

## ACKNOWLEDGEMENTS

The authors would like to thank all colleagues at the Fraunhofer ISE PV-TEC; especially I. Aidam and M. Frettlöh for ECV measurements. This work was funded by the German Federal Ministry for Economic Affairs and Energy within the research project "POLDI" under contract number 0324079D.

# REFERENCES

[1] A. W. Blakers, et al., "22.8% efficient silicon solar cell," *Appl. Phys. Lett.*, vol. 55, no. 13, pp. 1363–1365, 1989.

- ITRPV consortium, "International Technology Roadmap for Photovoltaic (ITRPV): Results 2019, 11th edition," 11th Edition, Apr. 2020.

- [3] R. Preu, et al., "Passivated Emitter and Rear Cell-Devices, Technology and Modelling," *Applied Physics Reviews, accepted for publication*, 2020.

- [4] S. Nold, Techno-ökonomische Bewertung neuer Produktionstechnologien entlang der Photovoltaik-Wertschöpfungskette: Modell zur Analyse der Total Cost of Ownership von Photovoltaik-Technologien. Stuttgart: Fraunhofer Verlag, 2019.

- [5] F. Stenzel, et al., "Exceeding 23 % and Mass Production of p-Cz Q.ANTUM Bifacial Solar Cells," in 36th EU PVSEC 2019.

- [6] E. Lohmüller, et al., "Front side optimization on boron- and gallium-doped Cz-Si PERC solar cells exceeding 22% conversion efficiency," in 37th EU PVSEC 2020, this conference.

- [7] Y. Lv, et al., "Towards high-efficiency industrial p-type mono-like Si PERC solar cells," *Solar Energy Materials and Solar Cells*, vol. 204, p. 110202, 2020.

- [8] T. Dullweber, et al., "Emitter Saturation Currents of 22 fA/cm2 Applied to Industrial PERC Cells Approaching 22% Conversion Efficiency," 32nd EU PVSEC, 2016.

- [9] S. Werner, et al., "Key Aspects for Fabrication of p-Type Cz-Si PERC Solar Cells Exceeding 22% Conversion Efficiency," 33rd EU PVSEC, 2017.

- [10] M. Müller, et al., "Loss analysis of 22% efficient industrial PERC solar cells," *Energy Procedia*, vol. 124, pp. 131–137, 2017.

- [11] P. Palinginis, et al., "Pioneering the industrialization of PERC technology: A review of the development of mono- and bifacial PERC solar cells at SolarWorld," *Photovoltaics International*, vol. 42, pp. 51–72, https://store.pv-tech.org/store/pioneering-the-industrialization-of-perc-technology-a-review-of-the-development-of-mono-and-bifacial-perc-solar-cells-at-solarworld/, 2019

- [12] I. Höger, et al., "Boosting module power by advanced interconnection and p-type Cz silicon solar cell efficiencies exceeding 22% in mass production," in *Silicon PV 2018*, p. 110003.

- [13] L. Ventura, et al., "Realization of selective emitters by rapid thermal and laser assisted techniques," in *13th EU PVSEC*, Nice, 1995, pp. 1578–1581.

- [14] J. Horzel, et al., "Verfahren zur Ausbildung eines Dotierstoffprofils," WO 2010/066626 A2, Jun 17, 2010

- [15] K. Breuer, et al., "Verfahren zur flächigen Gasphasenbehandlung von Halbleiterbauelementen," DE 10 2011 000 973 A1, Aug 30, 2012.

- [16] S. Lohmüller nee Werner, et al., "Analysis of Phosphosilicate Glass Structures Formed by Atmospheric Pressure and High Throughput Low Pressure POCL3 Diffusion," in 2018 IEEE 7th World Conference, pp. 1530–1535.

- [17] S. Werner, et al., "Structure and composition of phosphosilicate glass systems formed by POCl3 diffusion," *Energy Procedia*, vol. 124, pp. 455– 463, 2017.

- [18] A. Cuevas, "A good recipe to make silicon solar cells," in *The Conference Record of the Twenty-Second IEEE Photovoltaic Specialists Conference* -

- 1991, Las Vegas, NV, USA, Oct. 1991, pp. 466–470.

- [19] P. A. Basore, et al., "Simplified high-efficiency silicon cell processing," *Solar Energy Materials* and *Solar Cells*, vol. 34, no. 1-4, pp. 91–100, 1994.

- [20] S. Werner, et al., "Process Optimization for the Front Side of p-Type Silicon Solar Cells," in 29th EU PVSEC, Amsterdam, 2014.

- [21] Y. Komatsu, et al., "Innovative diffusion processes for improved efficiency on industrial solar cells by doping profile manipulation," in 24th EU PVSEC, Hamburg, Germany, 2009, pp. 1–5.

- [22] Y. Komatsu, et al., "Sophistication of Doping Profile Manipulation - Emitter Performance Improvement without Additional Process Step," in 25th EU PVSEC, Valencia, 2010.

- [23] M. Mühlbauer, et al., "Industrial Low-Pressure Phosphorus Diffusion for High Performance and Excellent Uniformity," in 26th EU PVSEC, Hamburg, 2011.

- [24] S. Mack, et al., "Impact of Solar Cell Manufacturing Processes on Thermal Oxide-Passivated Silicon Surfaces," in 24th EU PVSEC, Hamburg, Germany, 2009.

- [25] S. Mack, et al., "Control and optimization of thermal oxidation processes for industrial solar cell fabrication," in 2009 34th IEEE Photovoltaic Specialists Conference (PVSC), Philadelphia, PA, USA, Jun. 2009 - Jun. 2009, pp. 1024–1028.

- [26] S. Mack, et al., "Silicon Surface Passivation by Thin Thermal Oxide/PECVD Layer Stack Systems," *IEEE Journal of Photovoltaiks*, no. Vol. 1, No. 2, pp. 135–145, 2011.

- [27] Guide to Calculate Cost of Ownership (COO) Metrics for Semiconductor Manufacturing Equipment, SEMI E35-0618.

- [28] Specification for Definition and Measurement of Equipment Reliability, Availability, and Maintainability (RAM) and Utilization, SEMI E10-0814E.

- [29] E. Peiner, "Doping Profile Analysis in Si by Electrochemical Capacitance-Voltage Measurements," J. Electrochem. Soc., vol. 142, no. 2, p. 576, 1995.

- [30] R. Bock, et al., "Accurate Extraction of Doping Profiles from Electrochemical Capacitance Voltage Measurements," in 23rd EU PVSEC, Valencia, 2008

- [31] J. Weber, et al., "A Scanning Spreading Resistance Microscopy Study on a Laser-Doped Selective Phosphorous Emitter," *IEEE J. Photovoltaics*, vol. 10, no. 5, pp. 1313–1318, 2020.

- [32] A. Kimmerle, et al., "Carrier-diffusion corrected J0-analysis of charge carrier lifetime measurements for increased consistency," *Solar Energy Materials* and *Solar Cells*, vol. 142, pp. 116–122, 2015.

- [33] R. B. Fair, et al., "A Quantitative Model for the Diffusion of Phosphorus in Silicon and the Emitter Dip Effect," *J. Electrochem. Soc.*, vol. 124, no. 7, p. 1107, 1977.

- [34] S. Werner, et al., "Suitability of POCL3 Diffusion Processes with In-Situ Oxidation for Forming Laser-Doped Selective Emitters with Low Carrier Recombination," in 33rd EU PVSEC, Amsterdam, 2017.

- [35] J. R. Köhler, et al., "Phosphorus out-diffusion in laser molten silicon," *J. Appl. Phys.*, vol. 117, no. 14, p. 145701, 2015.

- [36] B. E. Deal, et al., "Thermal Oxidation of Heavily Doped Silicon," *J. Electrochem. Soc.*, vol. 112, no. 4, p. 430, 1965.

- [37] C. P. Ho, "Thermal Oxidation of Heavily Phosphorus-Doped Silicon," *J. Electrochem. Soc.*, vol. 125, no. 4, p. 665, 1978.