FRAUNHOFER INSTITUTE FOR APPLIED SOLID STATE PHYSICS IAF

#### SCIENCE FOR SYSTEMS

No. 53

Laurenz John

INTEGRATED SUB-MILLIMETER-WAVE HIGH-POWER AMPLIFIERS IN ADVANCED InGaAs-CHANNEL HEMT TECHNOLOGY

Fraunhofer Institute for Applied Solid State Physics IAF

Science for Systems

No 53

Laurenz John

Integrated Sub-Millimeter-Wave High-Power Amplifiers in Advanced InGaAs-Channel HEMT Technology

FRAUNHOFER VERLAG

#### Contact:

Fraunhofer Institute for Applied Solid State Physics IAF Tullastrasse 72 79108 Freiburg Phone +49 761 5159-0 info@iaf.fraunhofer.de www.iaf.fraunhofer.de

Cover illustration: Fraunhofer IAF

#### Bibliographic information of the German National Library:

The German National Library has listed this publication in its Deutsche Nationalbibliografie; detailed bibliographic data is available on the internet at www.dnb.de.

ISBN 978-3-8396-1762-5

#### D 90

Zugl.: Karlsruhe, Univ., Diss. 2021

Print and finishing: Fraunhofer Verlag, Mediendienstleistungen

The book was printed with chlorine- and acid-free paper.

#### © Fraunhofer Verlag, 2021

Nobelstrasse 12 70569 Stuttgart Germany verlag@fraunhofer.de www.verlag.fraunhofer.de

is a constituent entity of the Fraunhofer-Gesellschaft, and as such has no separate legal status.

Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. Hansastrasse 27 c 80686 München Germany www.fraunhofer.de

All rights reserved; no part of this publication may be translated, reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the written permission of the publisher.

Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. The quotation of those designations in whatever way does not imply the conclusion that the use of those designations is legal without the consent of the owner of the trademark.

## Integrated Sub-Millimeter-Wave High-Power Amplifiers in Advanced InGaAs-Channel HEMT Technology

Zur Erlangung des akademischen Grades

### Doktor der Ingenieurwissenschaften (Dr.-Ing.)

von der Fakultät für Elektrotechnik und Informationstechnik des Karlsruher Instituts für Technologie (KIT) genehmigte

### Dissertation

von

### M. Sc. Laurenz John

geb. in Heiligenberg

Tag der mündlichen Prüfung: Hauptreferent: Korreferent:

Mai 2021

Prof. Dr.-Ing. Thomas Zwick

Prof. Dr.-Ing. Ingmar Kallfass

## Kurzfassung

Die vorliegende Arbeit beschreibt die Entwicklung von breitbandigen, monolithisch integrierten Leistungsverstärkern im Frequenzbereich um 300 GHz. Diese Schaltungen sind zentrale Kernkomponenten für den erfolgreichen Aufbau von zukünftigen, hochbitratigen Richtfunkstrecken als auch von innovativen Radarsensoren im unteren THz-Frequenzbereich. Wesentliche Ziele der Arbeit sind die eingehende und umfassende Untersuchung von geeigneten Transistorkonfigurationen und Schaltungskonzepten, die erfolgreiche Realisierung von kompakten Verstärkerzellen für die platzeffiziente Integration in multifunktionalen Frontend-Schaltungen sowie der Aufbau von leistungsstarken Verstärkermodulen mit hoher Linearität.

Auf Transistorebene ist die experimentelle Optimierung der Gate-Drain-Recesslänge für eine Verbesserung der Durchbruchspannung auf über 4V beschrieben. Diese Entwicklung ermöglicht den Betrieb der Bauelemente mit Spannungen größer als 1,5V sowie eine Verbesserung der Leistungsdichte auf Werte von über 250 mW/mm. Des Weiteren werden in dieser Arbeit erstmals monolithisch integrierte Strukturen zur Load-Pull-Charakterisierung im Frequenzbereich oberhalb von 200 GHz untersucht, wodurch einzigartige Möglichkeiten zur Modellverifikation ermöglicht und neue Erkenntnisse für den Verstärkerentwurf bei 300 GHz gewonnen werden können.

Zur erfolgreichen Realisierung von ultrakompakten Submillimeterwellen-Verstärkern mit bisher unerreichter Ausgangsleistung, ist ein neuartiger Modellierungsansatz von Mehrfingertransistoren dargestellt. Dieser basiert auf erprobten Modellen von Zweifinger-Transistorfingern, welche in einer EM-simulierten Mehrfingertransistorschale implementiert werden. Die erfolgreiche Anwendung dieser Modellierungsmethode ermöglicht eine deutliche Reduzierung der benötigten Chipfläche und darüber hinaus eine wesentlich verbesserte Beschreibung der Bauelementeigenschaften von Leistungstransistoren mit bis zu acht Transistorfingern.

Für die Entwicklung von innovativen Leistungsverstärkerzellen und verlustarmen Power-Combining-Netzwerken ist die Analyse und Bewertung kompakter Dünnfilm-Verdrahtungsmöglichkeiten beschrieben. Durch die Realisierung neuartiger Vorderseitenmikrostreifenleitungen mit strukturierter Massefläche wird die Entwicklung sehr hochohmiger Leitungstypen gezeigt, welche die erfolgreiche Realisierung von monolithisch integrierten On-Chip-Combinern mit signifikant verbesserter Effizienz bei THz-Frequenzen ermöglichen.

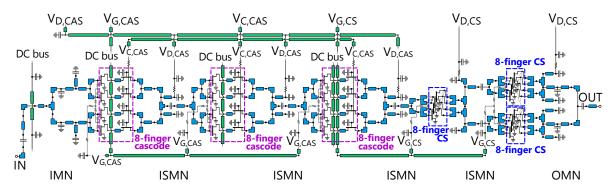

Basierend auf diesen Arbeiten sowie der eingehenden Analyse von parallelen und seriellen Transistorkonfigurationen, wird die Umsetzung einer neuartigen Verstärkertopologie bei 300 GHz demonstriert. Die Topologie basiert auf der Kombination von Kaskoden-Zellen in den Eingangsstufen und Common-Source-Bauelementen in der Ausgangsstufe. Dies ermöglicht die platzeffiziente Parallelschaltung von 32 Transistorfingern mit einer enormen ausgangsseitigen Gesamtgateweite von 512 µm innerhalb einer sehr kompakten Chip-Breite von lediglich 0,35 mm. Aufbauend auf dieser Verstärkertopologie wird

L

eine operative Bandbreite von mehr als 50 GHz und eine Rekord-Ausgangsleistung von 24 mW bei 300 GHz erzielt, was eine Verbesserung der bisherigen maximalen Ausgangsleistung der zugrundeliegenden HEMT-Technologie um den Faktor 4 darstellt. Durch die deutliche Verkleinerung der für die Verstärkerzelle benötigten Chipfläche, wird die Ausgangsleistung pro eingesetzter Chipbreite ebenfalls sehr signifikant um einen Faktor von größer als 4 gesteigert. Die gemessene Ausgangsleistung der sehr kompakten Verstärkerzelle is größer als 20 mW von 286 bis 310 GHz, was den weltweiten Stand der Technik in diesem Frequenzbereich definiert.

Durch den erfolgreichen Aufbau der innovativen Submillimeterwellen-Verstärker in Hohlleitermodule wird eine beeindruckende lineare Ausgangsleistung von 6 mW und eine Sättigungsleistung von mehr als 10 mW über eine 3 dB-Bandbreite von 285 bis 335 GHz erzielt. Mit diesen Ergebnissen wird der Stand der Technik für mHEMT-Verstärkermodule um einen Faktor von bis zu 4 verbessert, wodurch eine signifikante Steigerung der verfügbaren Ausgangsleistung für die Realisierung von Kommunikationsanwendungen als auch hochauflösenden Radarsensoren der nächsten Generation erfolgreich demonstriert wird.

## Abstract

This work examines the realization of broadband InGaAs mHEMT power amplifiers in the frequency band around 300 GHz. These circuits are developed as key components for the implementation of wireless high-capacity communication systems and innovative radar solutions in the lower THz frequency band. The goal is the in-depth investigation of device configurations and amplifier topologies for the realization of highly-compact power amplifier cells, which are suitable for monolithic integration in multifunctional front-end circuits as well as low-loss packaging into waveguide modules.

With the evaluation of different drain-gate recess lengths, the break-down voltage of the mHEMT devices is improved to values above 4 V. This permits the operation of the transistors at voltage levels exceeding 1.5 V and increases the power density to values larger than 250 mW/mm at device level. Furthermore, monolithic integrated circuits for on-chip load pull are demonstrated for the first time in the frequency range above 200 GHz, providing the unique possibility of model verification and new insight for PA-design considerations in the lower THz range around 300 GHz.

To reduce the size of the PA MMICs and maximize the output power per required chip width, a novel modeling approach for multi-finger transistors is implemented. This approach is solely based on two-finger device models which are included in an EMsimulated multi-finger shell. By using this innovative modeling method, highly-compact devices with up to 8 transistor fingers are realized and accurately described. Thus, the superior model accuracy and bandwidth of the symmetric two-finger transistor is utilized and limitations of previously-used HEMT devices are overcome.

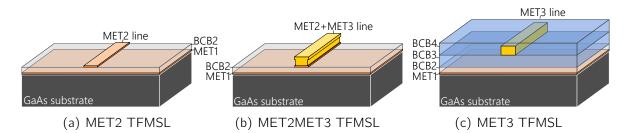

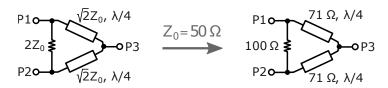

To implement highly-compact power amplifier cells and power-combing networks, thinfilm wiring possibilities are analyzed and evaluated. For the first time, thin-film transmission lines with structured ground metal are implemented in a III-V technology at the lower THz-frequency range. These transmission lines are used as key building block for the realization of novel thin-film combiners with improved combining efficiency in comparison to previously-reported THz power combiners.

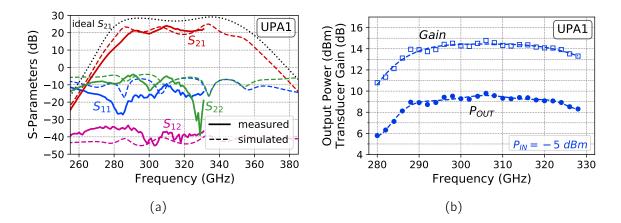

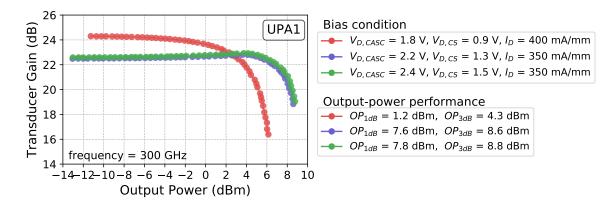

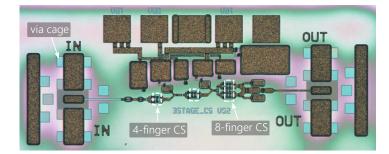

Based on these investigations as well as the analysis of parallel-connected and seriesconnected device configurations, the implementation of a novel 300-GHz PA topology is evaluated. This topology is based on the combination of cascode gain stages at the input and common-source devices in the output stage, which enables the successful and chip-space-efficient integration of 32 parallel transistor fingers with a total gate width of 512 µm on an ultra-compact chip width of only 0.35 mm. State-of-the-art output-power performance is achieved with this chip-size-optimized PA topology, demonstrating high bandwidths and a record output power of 24 mW around 300 GHz. Hence, the outputpower level of the underlying technology is significantly improved by a factor of 4. Since the PA core is implemented on an even reduced absolute die area, when compared to previously-reported mHEMT PA circuits, the output power per required chip width is also increased by a factor larger than 4. The measured output power of this compact amplifier cell is in excess of 20 mW over the frequency range from 286 to 310 GHz, advancing the state of the art for solid-state power amplifier MMICs.

Additionally, with the successful packaging into waveguide modules, more than 10 mW saturated output power and state-of-the-art 6-mW linear output power are demonstrated on waveguide level with a 3-dB bandwidth covering the frequencies from 285 to 335 GHz. These results improve the state of the art for mHEMT amplifier modules by a factor of up to 4, successfully demonstrating a significant increase in available output power for the realization of next-generation communication applications and high-resolution radar sensors.

## Acknowledgment

First, I would like to thank Prof. Dr. Thomas Zwick for supervising this work, giving me the freedom to develop and pursue my own ideas while asking the right critical questions when required. I'd further like to thank my co-supervisor Prof. Dr. Ingmar Kallfass for his support as well as the constructive and pleasant cooperation over the last couple of years.

I was very fortunate to work at Fraunhofer IAF and join a research group that had a tremendous base of knowledge and resources. The work described in this thesis benefited from the contribution of a large number of people in IAF's microelectronics and technology departments, which have developed the InGaAs mHEMT and packaging technologies over the past decades.

I'd like to thank all colleagues for the pleasant atmosphere at work and the continuous support throughout the past four years. The success of this work has been in large part due to the close support of Dr. Axel Tessmann and Dr. Arnulf Leuther. Their ideas and enthusiasm for research have been contagious and a great motivation to achieve the goals of this thesis. I'd further like to thank Prof. Dr. Dr. Oliver Ambacher, Prof. Dr. Rüdiger Quay, and Dr. Jutta Kühn for providing the resources and the possibility to work on an exciting and innovative topic with cutting edge technologies.

A key input for the successful circuit design have been the discussions with my fellow circuit designers at IAF. I acknowledge and thank my office mate Philipp Neininger as well as Dr. Fabian Thome, Dr. Thomas Merkle, Christian Friesicke, Markus Weiss, Dominik Meier, and Bersant Gashi for many refreshing technical and non-technical conversations, ideas and food for thought. I am, furthermore, very grateful to Dr. Sébastien Chartier for proofreading this thesis and his support over the last year of this work.

The access to measurement labs and equipment has been essential to the results obtained in this work. I'd like to thank especially Hermann Massler, Sandrine Wagner, and Roger Lozar for their help and access to the required equipment for device, circuit and module characterization. The waveguide modules have been developed based on the contribution of the whole packaging group. My grateful acknowledgment goes to Birgit Weismann-Thaden, Markus Rießle, Martin Zink, Michael Meister Kuri, and Hans-Peter Stulz for their support of these efforts.

Finally, I would like to thank my friends, family, and dog for their support and patience over the course of the last four years.

## Contents

| 1 | Intro | oduction                                                              | 1  |

|---|-------|-----------------------------------------------------------------------|----|

|   | 1.1   | Technologies for 300-GHz Power Amplifiers                             | 2  |

|   |       | 1.1.1 State of the Art of 300-GHz Power Amplifier Concepts            | 4  |

|   | 1.2   | Goals and Outline of this Work                                        | 7  |

| 2 | Ana   | lysis of Device Configurations and Thin-Film Transmission Lines       | 11 |

|   | 2.1   | Metamorphic High-Electron-Mobility Transistor Technology              | 12 |

|   | 2.2   | Concepts and Device Configurations for sub-mm-Wave Power Amplifiers   | 13 |

|   |       | 2.2.1 Parallel-Connected Power Amplifier Concepts                     | 13 |

|   |       | 2.2.2 Series-Connected Power Amplifier Concepts                       | 15 |

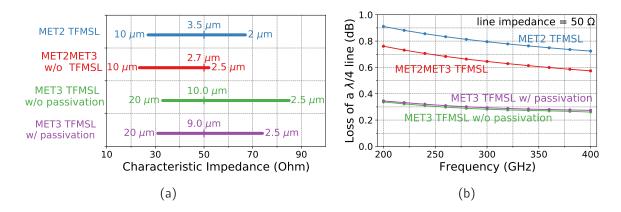

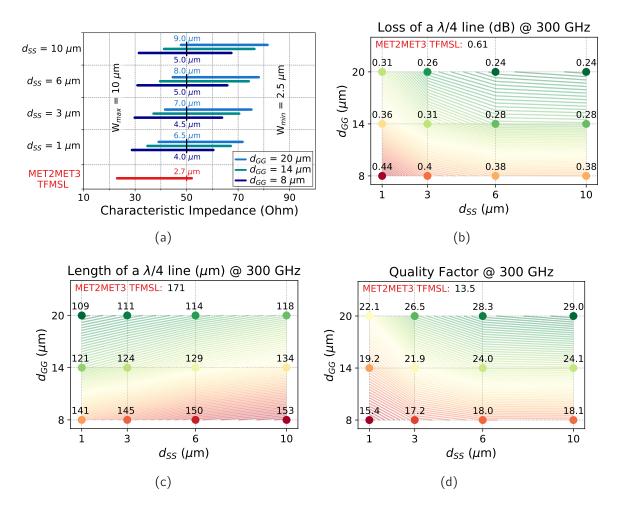

|   | 2.3   | Thin-Film Transmission Lines for Compact sub-mm-Wave Power Amplifiers | 18 |

|   |       | 2.3.1 Traditional Thin-Film Wiring                                    | 21 |

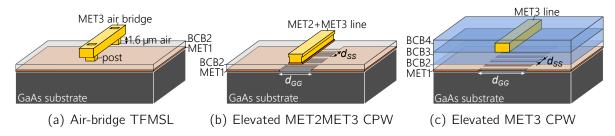

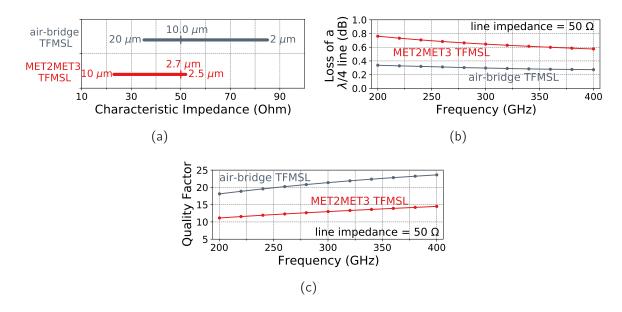

|   |       | 2.3.2 Air-Bridge Thin-Film Wiring                                     | 23 |

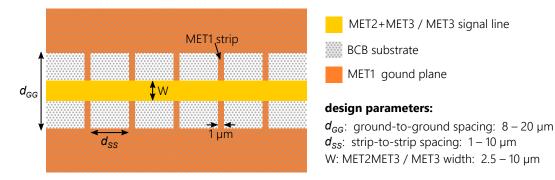

|   |       | 2.3.3 Thin-Film Transmission Lines with Structured Ground Metal       | 24 |

|   | 2.4   | Discussion and Conclusion on Chapter 2                                | 28 |

| 3 | Ana   | lysis of InGaAs mHEMT Devices for Broadband 300-GHz Power             |    |

|   | Amp   | olifiers                                                              | 31 |

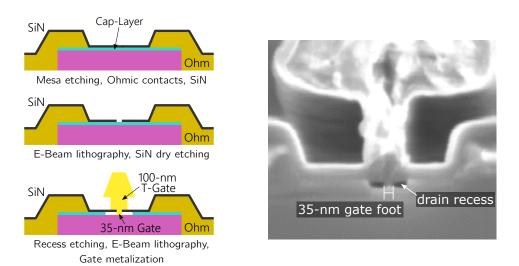

|   | 3.1   | Recess Optimization for Increased Breakdown Voltage                   | 31 |

|   |       | 3.1.1 Evaluation of Recess-Length Impact on DC and Small-Signal       |    |

|   |       | Device Figures                                                        | 32 |

|   |       | 3.1.2 Large-Signal Performance Characterization and Considerations .  | 35 |

|   | 3.2   | Evaluation and Modeling of Multi-Finger Devices                       | 38 |

|   |       | 3.2.1 Impact of Feeding Structures and Layout Complexity              | 40 |

|   |       | 3.2.2 Modeling of Compact Multi-Finger Devices                        | 43 |

|   |       | 3.2.3 Development of Compact Multi-Finger Cascode Devices             | 46 |

|   | 3.3   | Comparison of Device Configurations                                   | 50 |

|   | 3.4   | On-Chip Load Pull of mHEMT Devices at THz Frequencies                 | 53 |

|   |       | 3.4.1 On-Chip Load-Pull Circuit Topology                              | 54 |

|   |       | 3.4.2 On-Chip Load-Pull Characterization                              | 56 |

|   | 3.5   | Discussion and Conclusion on Chapter 3                                | 61 |

| 4 | Dev   | elopment of Compact 300-GHz Power Amplifier MMICs                     | 63 |

|   | 4.1   | Circuit-Simulation Approach                                           | 63 |

|   | 4.2   | Development of a Compact 300-GHz PA Topology                          | 66 |

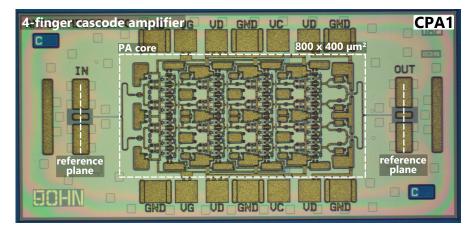

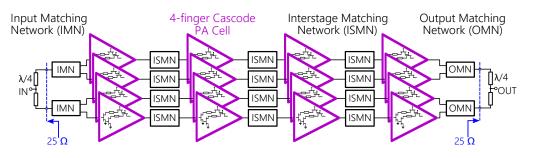

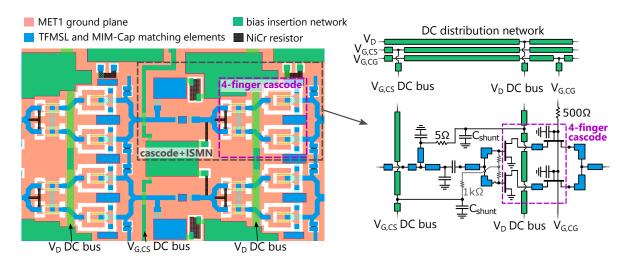

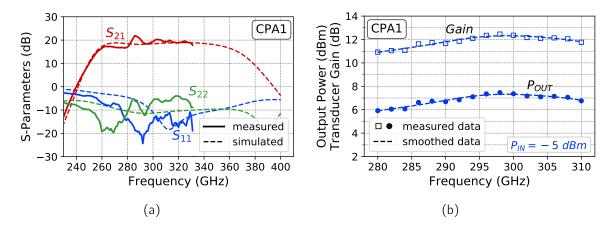

|   |       | 4.2.1 300-GHz Cascode Amplifier Circuits                              | 67 |

|   |       | 4.2.2 Chip-size Optimized 300-GHz Unit Amplifier                      | 72 |

|        | 4.3                                                            | 300-GHz Thin-Film Wilkinson Power Combiners                                                                                                                                                                                                                                                                                                                                   | 77                                                                                                    |

|--------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|        | 4.4<br>4.5                                                     | Combiners                                                                                                                                                                                                                                                                                                                                                                     | 80<br>86<br>89                                                                                        |

| 5      | 300-                                                           | GHz Power Amplifier Waveguide Modules                                                                                                                                                                                                                                                                                                                                         | 93                                                                                                    |

|        | 5.1                                                            | <ul> <li>Considerations for Via Placement in Compact THz MMICs</li></ul>                                                                                                                                                                                                                                                                                                      | 93<br>96<br>99<br>100                                                                                 |

|        | 5.2                                                            | 300-GHz Power Amplifier Waveguide Module5.2.1Measurement Results                                                                                                                                                                                                                                                                                                              | 102<br>103                                                                                            |

|        | 5.3                                                            | Waveguide Power Combiner at 300-GHz                                                                                                                                                                                                                                                                                                                                           | 105                                                                                                   |

|        | 5.4<br>5.5                                                     | Two-Way Combined 300-GHz Power Amplifier                                                                                                                                                                                                                                                                                                                                      | 109<br>112                                                                                            |

|        |                                                                |                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| 6      | Cond                                                           | clusion and Discussion                                                                                                                                                                                                                                                                                                                                                        | 115                                                                                                   |

| 6<br>A |                                                                | GHz State-of-the-Art Power Amplifiers and On-Chip Combiners         300-GHz Power Amplifier MMICs         300-GHz Power Amplifier Modules         300-GHz On-Chip Combiners                                                                                                                                                                                                   | <ul> <li>115</li> <li>119</li> <li>120</li> <li>120</li> </ul>                                        |

| _      | <b>300-</b><br>A.1<br>A.2<br>A.3                               | GHz State-of-the-Art Power Amplifiers and On-Chip Combiners<br>300-GHz Power Amplifier MMICs                                                                                                                                                                                                                                                                                  | <b>119</b><br>119<br>120                                                                              |

| Α      | <b>300-</b><br>A.1<br>A.2<br>A.3                               | GHz State-of-the-Art Power Amplifiers and On-Chip Combiners         300-GHz Power Amplifier MMICs         300-GHz Power Amplifier Modules         300-GHz On-Chip Combiners                                                                                                                                                                                                   | <b>119</b><br>119<br>120<br>120                                                                       |

| Α      | <b>300-</b><br>A.1<br>A.2<br>A.3<br><b>Eleva</b><br>B.1<br>B.2 | GHz State-of-the-Art Power Amplifiers and On-Chip Combiners         300-GHz Power Amplifier MMICs         300-GHz Power Amplifier Modules         300-GHz On-Chip Combiners         300-GHz On-Chip Combiners         ated-CPW and Slow-Wave Thin-Film Transmission Lines         Additional Information on the MET2MET3 ECPW                                                 | <ul> <li>119</li> <li>119</li> <li>120</li> <li>120</li> <li>123</li> <li>124</li> </ul>              |

| B      | 300-<br>A.1<br>A.2<br>A.3<br>Eleva<br>B.1<br>B.2<br>Mod        | GHz State-of-the-Art Power Amplifiers and On-Chip Combiners         300-GHz Power Amplifier MMICs         300-GHz Power Amplifier Modules         300-GHz On-Chip Combiners         300-GHz On-Chip Combiners         ated-CPW and Slow-Wave Thin-Film Transmission Lines         Additional Information on the MET2MET3 ECPW         Additional Information on the MET3 ECPW | <ul> <li>119</li> <li>119</li> <li>120</li> <li>120</li> <li>123</li> <li>124</li> <li>127</li> </ul> |

## **Abbreviations and Symbols**

### Abbreviations

| ADS    | Advanced Design System                        |

|--------|-----------------------------------------------|

| BCB    | Benzocyclobutene                              |

| BEOL   | Back end of line                              |

| B2B    | Back to back                                  |

| CB     | Common base                                   |

| CE     | Common emitter                                |

| CG     | Common gate                                   |

| CI     | Confidence interval                           |

| CPW    | Coplanar waveguide                            |

| CS     | Common source                                 |

| CST    | Computer Simulation Technology AG             |

| DC     | Direct current                                |

| DUT    | Device under test                             |

| ECPW   | Elevated coplanar waveguide                   |

| EM     | Electromagnetic                               |

| FEOL   | Front end of line                             |

| FET    | Field-effect transistor                       |

| FOM    | Figure of merit                               |

| GaAs   | Gallium Arsenide                              |

| HBT    | Heterojunction bipolar transistor             |

| HEMT   | High-electron-mobility transistor             |

| IC     | Integrated circuit                            |

| IMN    | Input matching network                        |

| InGaAs | Indium Gallium Arsenide                       |

| InP    | Indium Phosphide                              |

| ISMN   | Interstage matching network                   |

| ISS    | Impedance standard substrate                  |

| LNA    | Low-noise amplifier                           |

| mHEMT  | Metamorphic high-electron-mobility transistor |

| MAG    | Maximum available gain                        |

| MIM    | Metal-insulator-metal                         |

| MMIC   | Millimeter-wave integrated circuit            |

| MSG    | Maximum stable gain                           |

| NiCr   | Nickel-Chromium                               |

| OMN    | Output matching network                       |

|        |                                               |

| P2P   | Point-to-point                         |

|-------|----------------------------------------|

| PA    | Power amplifier                        |

| PDK   | Process design kit                     |

| RF    | Radio frequency                        |

| SEM   | Scanning electron microscope           |

| SiGe  | Silicon Germanium                      |

| SiN   | Silicon Nitride                        |

| SSPA  | Solid-state power amplifier            |

| TFMSL | Thin-film microstrip transmission line |

| TFR   | Thin-film resistor                     |

| TGW   | Total gate width                       |

| TRL   | Thru-reflect-line                      |

| TSV   | Thru-substrate via                     |

| UA    | Unit amplifier                         |

\_\_\_\_\_

### Symbols

| <i>f</i> <sub>max</sub> Maximum frequency of oscillation, power-gain cutoff frequence | у |

|---------------------------------------------------------------------------------------|---|

| f Eroquency of operation                                                              |   |

| f <sub>op</sub> Frequency of operation                                                |   |

| $f_{\rm T}$ Transit frequency, current-gain cutoff frequency                          |   |

| g <sub>DS</sub> Output conductance                                                    |   |

| <i>g</i> <sub>m</sub> Transconductance                                                |   |

| <i>h</i> <sub>21</sub> Forward current gain                                           |   |

| I <sub>D</sub> Drain current                                                          |   |

| I <sub>D,max</sub> Drain current in saturation                                        |   |

| I <sub>G</sub> Gate current                                                           |   |

| k Rollet stability factor                                                             |   |

| <i>OP</i> <sub>1dB</sub> Output power in 1-dB gain compression                        |   |

| <i>OP</i> <sub>3dB</sub> Output power in 3-dB gain compression                        |   |

| P <sub>DC</sub> DC power                                                              |   |

| P <sub>out</sub> Output power                                                         |   |

| Q Quality factor                                                                      |   |

| R <sub>D</sub> Drain resistance                                                       |   |

| R <sub>S</sub> Source resistance                                                      |   |

| U Unitary power gain, Mason gain                                                      |   |

| V <sub>DS</sub> Drain-source voltage                                                  |   |

| V <sub>G</sub> Gate voltage                                                           |   |

| V <sub>th</sub> Threshold voltage                                                     |   |

| W <sub>G</sub> Gate width                                                             |   |

## **1** Introduction

"Nothing, I guess". This was the reputed response of Heinrich R. Hertz, the physicist who first demonstrated the existence of electromagnetic waves, when asked about any potential application for his "Hertzian waves". Since Hertz's first proof of James C. Maxwell's theory of electromagnetism in 1886 [7, 45], however, the radio waves have significantly shaped and contributed to our economic and social development since the early 20th century.

While the millimeter-wave (mm-wave) frequency spectrum—covering the frequency range from 30 to 300 GHz—has been attracting radar and wireless-communication applications for decades, the purpose has been mainly for scientific and military usage. In recent years, however, mm-wave technologies have been fostered by commercial applications, such as automotive radar and 5G [9, 47], that go well beyond the traditional niche markets. This trend towards ever-higher frequencies and the increased interest for wireless-system implementation at frequencies up to 300 GHz—even at a commercial level—is driven by the available spectrum, which provides the bandwidths for high-capacity communication and high-resolution radar applications.

With the rapid shift to an always connected society of today's digital world, however, the electromagnetic spectrum has become a valuable and scarce resource, due to the increasing integration of sensing devices and technologies into everyday appliances for systems and applications, such as the Internet of things, machine-to-machine communication, and autonomous vehicles. Driven by new businesses and applications, billions of sensors and actuators are being wirelessly connected and every little piece of the frequency spectrum, up to the upper end of the mm-wave frequency range at 275 GHz, has already been allocated for wireless communication, sensing, and radar applications in most parts of the world [29, 31, 86].

Due to the ever-rising global mobile data traffic—which is growing by almost 50 % every year [19]—engineers, researchers, and spectrum regulators are looking to the submillimeter-wave frequency bands around and above 300 GHz [1, 2]. Especially the frequency band around 300 GHz has attracted a lot of attention for the implementation of high-data-rate wireless point-to-point (P2P) links in recent years [16, 22, 40, 95, 104]. Enabled by the high absolute bandwidths, which are available at the THz-frequency range (0.3–3 THz), wireless backhaul links have become feasible with the capability to handle the predicted Tbit/s throughput in the backbone of beyond-5G communication networks, either as an extension or replacement of fiber-optical connections [15, 69, 88].

While the next generations of mobile communication networks are, in addition, discussed as a crucial technology for autonomous vehicles [33], another key enabling technology for future self-driving transportation solutions are millimeter-wave radar sensors [20, 91]—which are already significantly contributing to the road safety of today. As the bandwidth for automotive radar applications is typically below a couple of Gigahertz, broadband millimeter-wave active and passive imaging systems have demonstrated manifold applications in safety and security, due to their ability to operate in harsh environmental conditions like snow, fog, dust and penetrate materials such as plastic, drywall, and clothing [71, 72]. While broadband W-band radar systems, with a bandwidth of operation exceeding 25 GHz, have demonstrated a resolution close to 7 mm at 80 GHz [83], the high achievable bandwidth, increasing resolution, and shrinking antenna dimensions are a strong motivation to increase the center frequency to the lower terahertz-frequency band around 300 GHz. Broadband radar systems in this frequency range, for instance, have demonstrated imaging solutions with sub-4-mm resolution [14, 74].

One of the key building blocks for most of these wireless communication or imaging systems is the power amplifier in the output stage of the transmitter. Yet, achieving sufficient output-power levels to compensate the rising atmospheric attenuation and free-space path loss [103] is a major challenge when increasing the frequency of operation well above 100 GHz. This is due to the shrinking dimensions of the active devices—which are scaled down in order to achieve the required cutoff frequencies for sub-millimeter-wave operation—reducing the breakdown voltage and available power density on the device level.

### 1.1 Technologies for 300-GHz Power Amplifiers

With the progressive scaling of junction dimensions and junction thicknesses of active devices, high-bandwidth transistor technologies featuring power-gain cutoff frequencies  $(f_{\rm max})$  above 1 THz have been demonstrated over the last decade [61, 66, 70, 118]. Driven by the growing interest in communication, radar, and imaging applications at frequencies around 300 GHz, even silicon-based CMOS technologies have demonstrated active circuits up to 325 GHz [81, 116]. Up to date, however, the best performance in terms of bandwidth, gain, and output power of 300-GHz stand-alone-amplifiers as well as receive and transmit circuits is enabled and has been demonstrated by III-V high-electron-mobility transistor (HEMT) and heterojunction bipolar transistor (HBT) devices.

When requiring high gain and lowest noise figures—not only considering the power density on device level—the InGaAs-channel HEMT has proven to be the most suitable semiconductor device technology for the development of high-dynamic-range transmit and receive solutions at the lower THz band. Especially InGaAs metamorphic HEMT (mHEMT) devices, which are processed on GaAs wafers, have demonstrated state-of-the-art low-noise amplifiers [113, 110] as well as chipsets for broadband radar [75] and communication [57] applications with state-of-the-art noise figures above 100 GHz. Furthermore, by integrating multiplier, mixing and amplifier circuits on a single die—as shown with the integrated 220–260-GHz InGaAs mHEMT single-chip radar front end in [75]—high complexity on circuit level has been demonstrated with III-V HEMT devices.

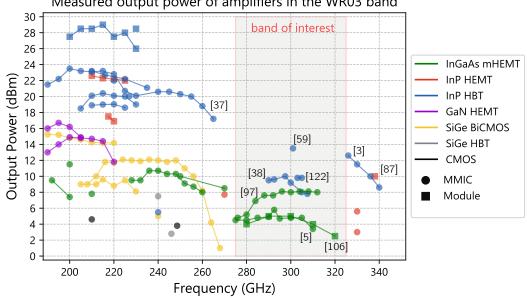

While InGaAs mHEMT devices have demonstrated state-of-the-art noise figures at mm-wave and THz frequencies, the generation of high RF-power levels of 10 dBm and more, has proved to be a major challenge. As the bias voltage for safe long-term operation is typically in the range of 1.0 V, the power density is limited on device level. Fig. 1.1 shows the state of the art in terms of measured output power demonstrated by H-band amplifiers, excluding the results of this thesis. This frequency range is dominated by InP-based HBT and HEMT technologies with significantly larger breakdown voltages and,

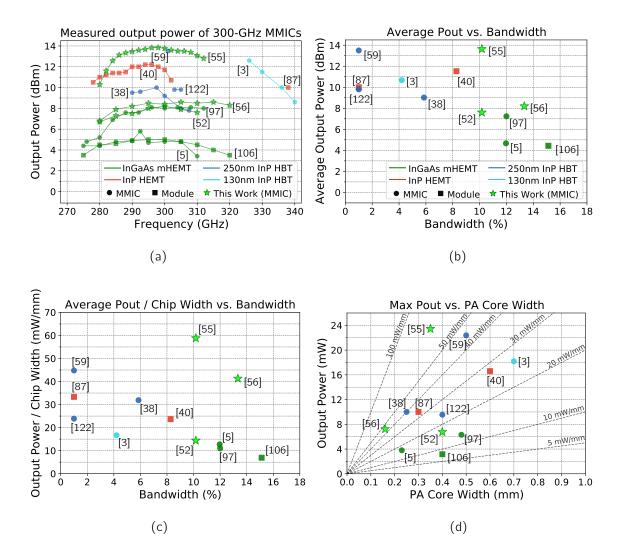

Measured output power of amplifiers in the WR03 band

Figure 1.1: State-of-the-art measured output power of solid-state power amplifier MMICs and modules at H-band frequencies, excluding the results of this thesis.

| Technology   | <b>f</b> ⊤<br>(GHz) | <b>f</b> <sub>max</sub><br>(GHz) | $f{BV}_{ m off}$ (V) | $\mathbf{V}_{	ext{bias}}$ $(ee)$ | Wiring type                   | Company/Institute      |

|--------------|---------------------|----------------------------------|----------------------|----------------------------------|-------------------------------|------------------------|

| InP HBT      | 392                 | 859                              | > 4.5                | 2.0                              | thin-film microstrip line     | Teledyne Scientific    |

| InP HEMT     | 500                 | 1200                             | > 4                  | > 1.8                            | (grounded) coplanar waveguide | Northrop Grumman Corp. |

| InGaAs mHEMT | >500                | >1000                            | > 3.5                | 1.0                              | (grounded) coplanar waveguide | Fraunhofer IAF         |

**Table 1.1:** Most relevant III-V HEMT and HBT technologies for H-Band operation

therefore, a larger power density on device level, compared to the depicted mHEMT technologies. Hence, the highest output power levels at H-band have been reported for InP HBT and InP HEMT based PA MMICs biased at 1.8–2.2 V [3, 37, 38, 59, 87, 122]. In [37], 17–24-dBm output power was reported between 180–265 GHz and at a narrow frequency band around 300 GHz, up to 13.5 dBm has been demonstrated in [59], both using a 250-nm InP HBT technology.

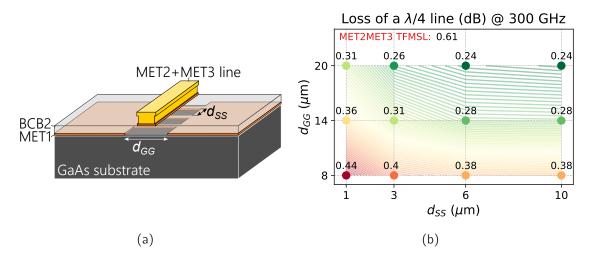

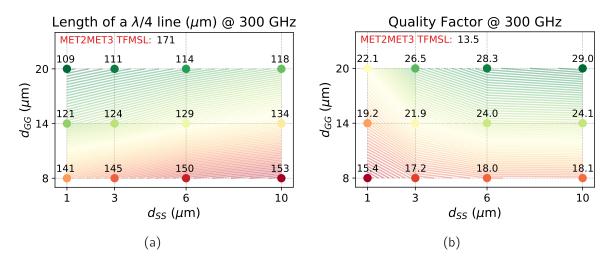

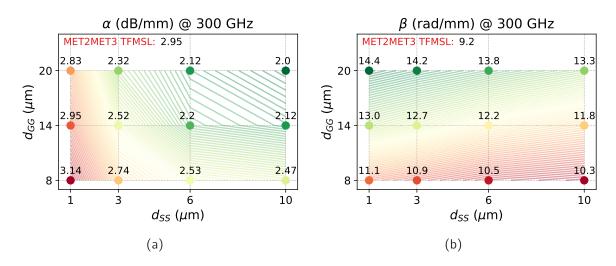

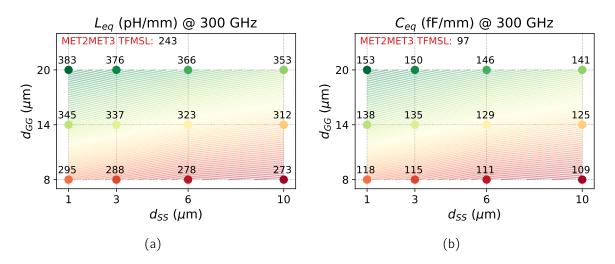

A comparison of the three most relevant MMIC technologies for 300-GHz operation is shown in Table 1.1. Important single-device characteristics such as cutoff frequencies, breakdown voltage, and maximum available/stable gain are key indicators for the capability of a semiconductor technology in terms of achievable power gain at a certain frequency on device level. The implementation of chip-size optimized multi-functional MMICs and amplifiers as well as the performance on circuit level, in addition, strongly depend on the wiring possibilities for matching and bias-insertion network design. Hence, the available layer stack including metals and dielectrics for signal routing is another key feature of semiconductor technologies. The most common types of on-chip transmission lines at frequencies above 100 GHz are the coplanar waveguide (CPW) and the thin-film microstrip line (TFMSL). While CPW transmission lines are primarily implemented in two-metal-layer HEMT technologies, the TFMSL environment requires additional dielectric layers on the wafer front side and has been widely used in InP HBT technologies.

Key figures such as the feasible impedance range and attenuation of the transmission lines, however, depend on the exact layer sequence and thickness of the underlying technologies.

While the active-device characteristics as well as wiring possibilities are fundamentally limiting the achievable PA performance for a given technology—the choice of topology and active-device configuration, additionally, significantly impacts the achievable output power on circuit level. The device configuration, in this sense, means the arrangement of active devices in common-source (CS), common-gate (CG), cascode, or stacked configuration, for example—and the circuit topology describes which and how many devices are cascaded or parallelized in a series or parallel power combining concept, respectively. To give more detailed information on the circuit topologies of the 300-GHz PAs of Fig. 1.1, the implemented device configurations are evaluated in the following section.

### 1.1.1 State of the Art of 300-GHz Power Amplifier Concepts

To put the concepts and measured output-power performance of the state of the art of power amplifiers operating around 300 GHz in the WR03-band into context, a detailed summary is provided in Tab. 1.2. The measured saturated output-power level of the listed amplifiers was already introduced in Fig. 1.1. In addition, Tab. 1.2 gives more details on the implemented circuit topologies as well as key characteristics, such as the implemented transistor periphery in the output stage (total gate width, TGW), chip dimensions, and supply voltages.

Two figure of merits (FOMs) are used to evaluate the output-power performance on circuit level. The first is the measured output power normalized to the implemented device periphery ( $P_{out}/TGW$ )—which fundamentally depends on the power density of the underlying technology, as well as the efficiency of the employed combiner topology. This FOM, therefore, can be used to directly compare the performance of amplifiers which are implemented in the same technology and to further asses the employed topology in terms of feasible output power on device level as well as power-combining efficiency. The second FOM is used to evaluate the compactness of the implemented PA cores, by normalizing the measured output power to the used chip width ( $P_{out}/W$ ). This FOM indicates the efficiency of the implemented PA topologies in terms of how much chip area is required to achieve a certain output power performance. This is especially relevant when considering further parallelization, as well as chip and system integration.

In general, the output-power density ( $P_{out}/TGW$ ) of vertical HBT and lateral HEMT devices cannot directly be compared, due to their fundamental differences in the respective transistor functionality. However, the results reported for the upper mm-wave frequency range show, that the InP HBT power amplifier circuits benefit from a higher power density on device level—which is, on the other hand, demonstrated over significantly smaller bandwidths around 300 GHz, in comparison to InGaAs-channel HEMT circuits, as can be seen in Tab. 1.2.

All of the listed InP HBT topologies are implemented with the transistor of the last stage being in common-base (CB) configuration. This is due to the fact, that the analysis of 250-nm InP HBT devices in CB and common-emitter (CE) configuration has showed that—when considering the gain performance in large-signal operation—the gain and

| Frequency <sup>*</sup><br>(GHz) | Technology            | Topology                                    | Chip width <sup>♠</sup><br>(mm) | <b>TGW</b><br>(μm) | <b>V</b> <sub>DC</sub> ★<br>(V) | <b>P</b> ₀ut,sat<br>(dBm) | <b>P<sub>out</sub>/TGW</b> <sup>‡</sup><br>(mW/mm) | P <sub>out</sub> ∕W <sub>ch</sub><br>(mW/mn |       |

|---------------------------------|-----------------------|---------------------------------------------|---------------------------------|--------------------|---------------------------------|---------------------------|----------------------------------------------------|---------------------------------------------|-------|

| 180-260                         | 250-nm InP<br>HBT     | 3-stage, cascode,<br>16-way combined        |                                 | 384                | 2.7                             | 20-24                     | 645                                                | 225                                         | [37]  |

| 290-307.5                       | 250-nm InP<br>HBT     | 3-stage, cascode,<br>2-way combined         | 0.25                            | 32                 | 1.95                            | 7.8–10                    | 312                                                | 40                                          | [38]  |

| 300-305                         | 250-nm InP<br>HBT     | 4-stage,<br>common-base,<br>4-way combined  | 0.4                             | 40                 | 1.8                             | 9.5–9.8                   | 238                                                | 24                                          | [122] |

| 301                             | 250-nm InP<br>HBT     | 4-stage, cascode,<br>2-way combined         | 0.5                             | 96                 | 2.2                             | 13.5                      | 233                                                | 45                                          | [59]  |

| 326-340                         | 130-nm InP<br>HBT     | 2-stage,<br>double-stack,<br>4-way combined | 0.7                             | 80                 | 1.8                             | 8.6–12.6                  | 227                                                | 25                                          | [3]   |

| 338                             | sub-35-nm InP<br>HEMT | 4-stage,<br>common-source<br>2-way combined |                                 | 160                | 2.2                             | 11†                       | 79                                                 | 42                                          | [87]  |

| 275-320                         | 35-nm InGaAs<br>mHEMT | 3-stage, cascode,<br>2-way combined         | 0.4                             | 72                 | 0.9                             | $5-7^{\dagger}$           | 69                                                 | 13                                          | [106] |

| 270-310                         | 35-nm InGaAs<br>mHEMT | 1-stage, triple-stac                        | k 0.23                          | 40                 | 3.4                             | 4–6                       | 100                                                | 17.3                                        | [5]   |

| 270-317                         | 35-nm InGaAs<br>mHEMT | 1-stage, triple-stacl<br>2-way combined     |                                 | 80                 | 3.0                             | 3–6                       | 50                                                 | 8                                           | [4]   |

| 275-312                         | 35-nm InGaAs<br>mHEMT | 5-stage,<br>common-source<br>4-way combined |                                 | 128                | 1.2                             | 5–8                       | 49                                                 | 13                                          | [97]  |

Table 1.2: Comparison of PA results and topologies around 300 GHz in the WR03 band.

The frequency range corresponds to the reported large-signal bandwidth.

Required chip width of the PA core including matching networks and the first stage of shunt capacitors in the bias insertion network, without RF/dc-pads.

$\star$ : Applied drain-source voltage ( $V_{DS}$ ) and collector-emitter voltage ( $V_{CE}$ ) of single HEMT and HBT devices.

1: Total gate width, device periphery in the output stage.

†: Only packaged results are reported. The depicted results include the reported values minus the specified transition loss.

\*: Chip width of the PA core.

power density of CE devices significantly decreases above 200 GHz, as reported in [118]. This consequently reduces the usefulness of the CE device configuration for PA circuits at the upper mm-wave frequency band. Therefore, state-of-the-art InP HBT PA circuits below 200 GHz typically use a CE power-amplifier cell [37]. For higher frequencies up to 300 GHz, a cascode topology is mostly implemented in InP HBT PA circuits, using the advantageous large-signal performance of the CB devices [37, 38].

The wiring type of the listed InP HBT PAs is TFMSL—which is used to parallelize up to 16 cascode PA cells in [37]—achieving state-of-the art 13.5-dBm output power around 300 GHz [59]. Looking at the output power per device periphery ( $P_{out}/TGW$ ) and per required chip width ( $P_{out}/W$ ), however, the 300-GHz results reported in [38, 59, 122] are significantly inferior to the ones reported up to 260 GHz [37], which have been realized in the same 250-nm InP HBT technology. Thus—considering the higher supply voltage and larger implemented finger width used in [37]—the 300-GHz PAs evidently still provide room for significant improvement in terms of output-power level per required chip width.

When comparing the InP-HBT PA topologies depicted in Tab. 1.2, only [3] claims the implementation of a series-connected topology with a 4-way combined double stack configuration (transistor stacking is discussed in detail in Section 2.2.2). While output-power levels above 10 mW are achieved over a small bandwidth with this topology, the implemented device periphery is significantly larger than the ones reported with the cascode topology in [38]. Therefore, when considering the 227-mW/mm power density per device periphery—which is the lowest of the listed InP HBT results around 300 GHz—it has to be concluded, that the claimed double-stack implementation is not substantiated by the reported measurement results in [3]. Keeping in mind the different combiner losses and

supply voltages listed in Tab. 1.2, the results reported in [3] rather demonstrate a performance level which is comparable to the classical cascode topology—showing no improved output-power performance by implementing the stacked topology around 300 GHz.

In InGaAs-channel HEMT technologies, on the other hand, the cascode configuration has very often been implemented in LNA and PA circuits up to THz frequencies above 400 GHz—due to its large levels of small-signal gain which can be provided in comparison to CS transistors. Yet, in the 300-GHz state of the art shown in Tab. 1.2, only one mHEMT cascode PA topology has been reported with [106]. In contrast, [5] and [4] report on 300-GHz PA circuits based on a triple-stack PA cell and mere CS HEMT amplifiers are described in [97] and [87].

All of the depicted 300-GHz HEMT PAs are implemented in CPW-wiring environment, which typically leads to a larger required chip area for matching network implementation in comparison to compact TFMSL circuits. When comparing the output power per required chip width of the InP HBT as well as InGaAs mHEMT results depicted in Tab. 1.2, the mHEMT results are significantly below 20 mW/mm, in contrast to up to 45 mW/mm for InP-based 300-GHz circuits. This is in large part due to the lower operating voltage—resulting in a lower power density on device level for the mHEMT devices—and in part caused by the CPW-wiring environment, which limits the implementation of compact 300-GHz PA cells.

When considering the results of the triple-stack mHEMT PA circuits reported in [4] in comparison to the cascode performance demonstrated by [106]—as for the stacked-HBT topology in [3]—no improvement in terms of output power per device periphery is shown for the stacked-HEMT topologies. Both the triple-stack circuit in [4] as well as the cascode design in [106] report on a two-way combined PA topology with tandem-X couplers at the same frequency and in the same technology. Therefore—keeping in mind possible power-density variations on device level, since the MMICs were not measured on the same wafer—a direct comparison of the parallelized stacked PA cell in [4] as well as the cascode PA cell in [106] is reasonable. Comparing the measured results, the triple-stack topology achieves significantly lower output-power levels, despite an even larger implemented total gate width (TGW) and higher supply voltage per device than the cascode circuit. Even when considering the slightly higher compression level of the cascode measurement data, no output-power improvements and, therefore, no successful transistor stacking at 300 GHz can be concluded from the data reported in [4]<sup>1</sup>.

In general, it can be concluded from the results listed in Tab. 1.2, that no superior device configuration in terms of significantly improved large-signal performance can be derived from the small number of different 300-GHz circuits, which were realized in the same InGaAs mHEMT technology. Within the same technology, single-device PA cells (CS for example) as well as cascode and stacked PA cells have demonstrated no clear advantage in terms of output-power performance on circuit level—neither per device periphery nor per required chip width.

<sup>&</sup>lt;sup>1</sup> The triple stack reported in [5] is excluded in this discussion, due to the large ripple shown in the frequency-sweep measurements in [5], which indicates a large measurement uncertainty. However, since the same triple-stack PA cell was implemented in [4] with significantly inferior large-signal performance, only [4] is used to evaluate the triple-stack performance.

### **1.2 Goals and Outline of this Work**

This work examines the development of broadband solid-state power amplifiers (SSPAs) in Fraunhofer IAF's InGaAs mHEMT technology, covering the frequency band around 300 GHz. Wireless communication and imaging systems based on this HEMT technology have set the state of the art around 300 GHz. By using high-gain and low-noise monolithic front-end chip sets with an excellent bandwidth in the range of 50 GHz, real-time capable 300-GHz P2P links with data rates in excess of 100 Gbit/s and imaging solutions with sub-4-mm resolution have been demonstrated [15, 57, 80]. The available output power, however, has been limited to power levels below 3 mW (5 dBm), using the packaged 300-GHz PA MMIC reported in [106]. To overcome this limitation and increase the operating range of wireless 300-GHz systems, the realization of the first HEMT based 300-GHz power amplifiers with output-power levels larger than 10 mW (10 dBm) is described in this thesis. These power amplifiers are required as key components for the development of next-generation high-performance THz P2P links and the exploration of novel applications for highly-broadband sensing systems at the lower THz frequency band.

The goal is the in-depth investigation of device configurations and topologies for the implementation of amplifiers with high output power. While large bandwidths in the range of 50 GHz are targeted, one of the key design goals is the miniaturization of amplifier circuits and the realization of highly-compact PA cells on the smallest chip size possible. Since power amplifiers typically require a large amount of chip area in comparison to other circuit components, a compact implementation is essential to enable the monolithic integration of multifunctional transmit-receive solutions on a single MMIC. Hence, the indepth investigation of innovative chip-size-optimized PA cells at the lower THz frequency range around 300-GHz is described in detail in this work. By achieving highly-compact circuit dimensions, the integration as reusable IP blocks in next-generation multi-channel MMICs and THz front ends with high-bandwidth and outstanding dynamic range is made possible. In addition, by reducing the required die area for single-chip front ends, the costs and efforts for processing, handling, as well as packaging of the MMICs can be notably reduced.

The circuit dimensions are, furthermore, of utmost importance when considering the assembly into waveguide modules. A key challenge in the successful packaging of standalone amplifier circuits is the suppression of cavity resonances when surrounding the MMIC with a closed cavity and a conductive surface material—as it is typically done in split-block waveguide packaging technologies. The theory tells us that cavity modes can exist and be excited for a width of the cavity that exceeds one half of a free space wavelength [26]. At 300 GHz, this corresponds to a width of 500 µm. Increasing the width of the chip beyond this limit possibly increases the complexity and costs for MMIC packaging if additional measures for cavity-mode suppression are needed. Thus, to ensure the successful packaging of the PA MMICs developed in this work, a maximum chip width of 500 µm was targeted. On this limited chip area, however, DC pads as well as biasdistribution networks also need to be integrated. This requirement limits the width of the PA-core circuit to less than 400-µm. The PA circuits described in the following chapters, therefore, have been designed for a reduced chip width while maximizing the total number of gate fingers in the output stage, and hence, maximizing the achievable output power at the required width of the integrated circuit. This figure of merit ( $P_{out}$ /chip width) was introduced in the previous section and is sought to be maximized, as this FOM indicates the efficiency of the implemented PA topology in terms of how much area is required on the wafer to achieve a certain output-power performance.

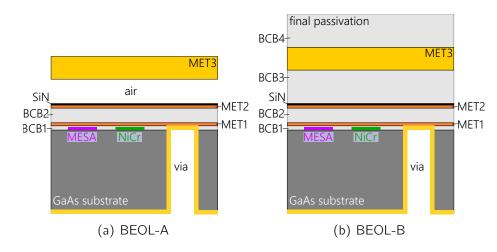

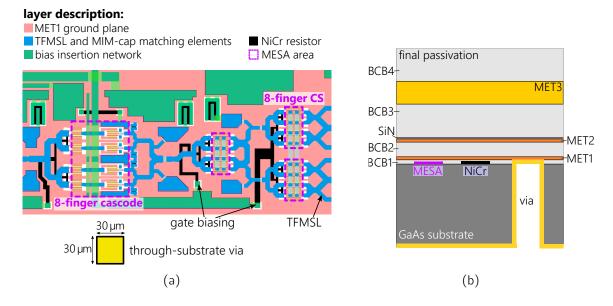

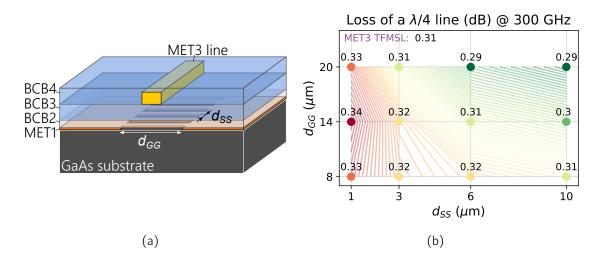

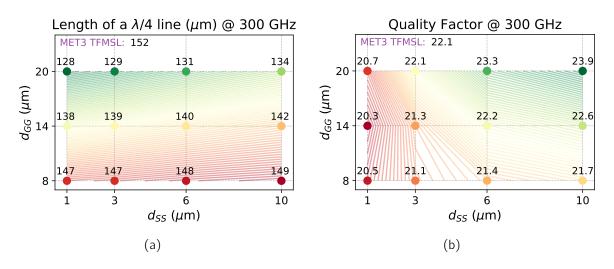

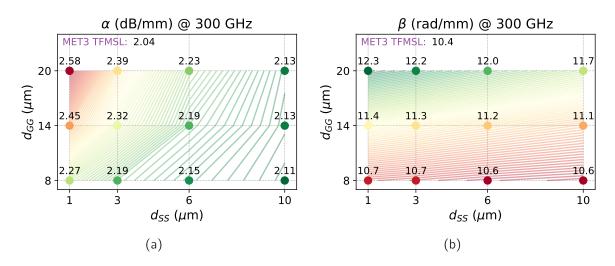

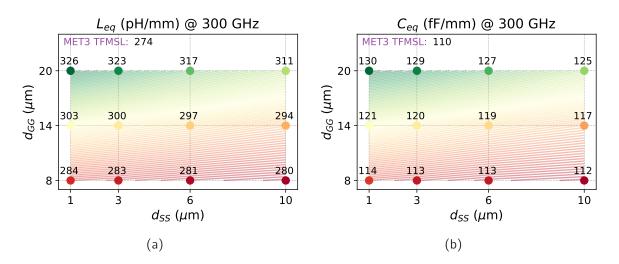

With recent developments of the back-end-of-line (BEOL) process of Fraunhofer IAF's InGaAs mHEMT technology—which includes the addition of a third metal layer as well as several additional dielectric layers in the former two-metal-layer BEOL—the implementation of TFMSL wiring has been made possible. Therefore, thin-film wiring and the associated possibilities for the design of innovative chip-size-optimized TFMSL matching and power-combining networks are investigated in depth at the frequency range around 300 GHz in this thesis.

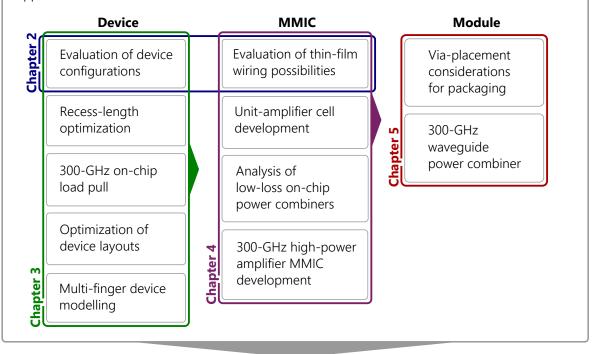

The results which are achieved on circuit level in this work are based on the comprehensive analysis of single transistors and device configurations, their implementation and modeling in chip-size-reduced PA cells, as well as the investigation of novel low-loss thin-film wiring possibilities for compact amplifier and combiner circuits. Fig. 1.2 shows an overview and the graphical structure of this thesis. The approach to improve the 300-GHz PA performance of the underlying InGaAs mHEMT technology on MMIC and module level can be divided into three parts. Each part deals with extensive design-related investigations as well as numerous improvements regarding three different system levels of the PA development: the device level, the MMIC level, and the module level.

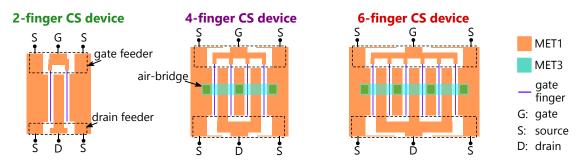

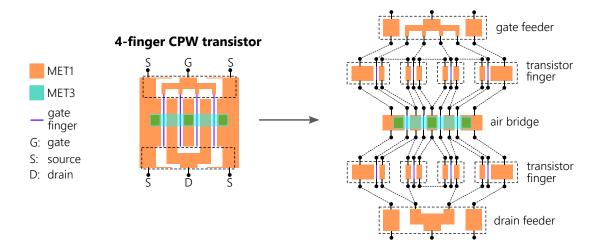

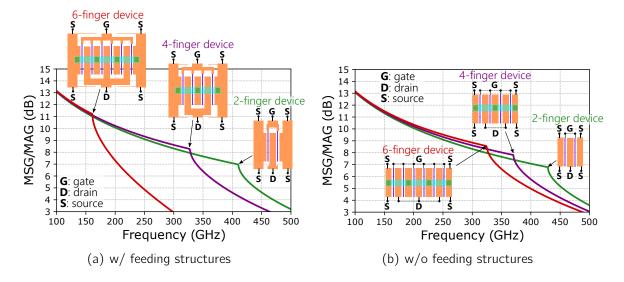

The first part—described in Chapter 3—includes detailed investigations on the transistor level, which are related to device-level performance as well as multi-finger-transistor implementation and modeling. In order to increase the breakdown voltage and, furthermore, improve the power density on device level, the length of the drain-gate recess is investigated and optimized experimentally. To maximize the total gate-width, novel multi-finger CS and cascode device layouts are developed, enabled by thin-film feeding structures which permit an accurate in-phase matching and feeding of multiple two-finger devices in parallel. The on-chip large-signal characterization of single devices—which are used for load-target definition and large-signal-model verification—is investigated for the first time at frequencies above 200 GHz, using unique in-situ load-pull MMICs with tunable output-matching networks at 300 GHz.

The PA-circuit design on MMIC level describes the second cornerstone of this thesis, which is covered in Chapter 4. Based on the multi-finger cascode and CS devices with up to eight transistor fingers described in Chapter 3, a highly-compact unit-amplifier (UA) topology is developed with the focus on maximizing the total gate width in the output stage and, hence, increasing the achievable output power on the smallest chip width possible. As the discussion of previously implemented PA circuits in the underlying mHEMT technology in Section 1.1.1 shows, no clearly superior topology can be derived from the prior-realized 300-GHz PAs. Thus, possible device configurations for a suitable 300-GHz PA implementation are evaluated thoroughly and design considerations for achieving an improved 300-GHz output power performance over a wide bandwidth with high linearity is described in detail. To implement several UA cells in parallel, novel TFMSL on-chip power combiners are investigated—including elevated CPW and air-bridge TFMSL environments. This permits the efficient parallelization of several UA cells in the BEOL of this mHEMT technology, by using thin-film wiring. Based on the UA cell and the power

**Goal** Development of novel 300-GHz InGaAs mHEMT amplifiers with high output power, broadband performance, and highly-compact chip dimensions, suitable for monolithic, module, and next-generation THz-system integration.

**Approach** In-depth investigation, development, and optimization of active devices as well as new device/circuit layouts and topologies, which are most suitable for power amplifier applications at 300 GHz.

**Results** Successful demonstration of chip-size optimized 300-GHz high-power amplifier MMICs and waveguide modules with state-of-the-art output power performance.

**Figure 1.2:** Graphical structure of this thesis. Depicted are the goals, approaches, and results. The design approach is categorized in investigations regarding the device level, MMIC level, as well as module level. The Chapters 3 to 5 are structured accordingly. Device configurations and thin-film transmission lines are first introduced in Chapter 2 as key building blocks for the subsequent device and circuit design. A detailed summary and assessment of the key achievements, results, and findings is provided in Chapter 6.

combiners, high-power amplifier MMICs with state-of-the-art output power performance are demonstrated.

The third main topic covered in this thesis is dedicated to the module integration and packaging of 300-GHz PA circuits, which is described in Chapter 5. While throughsubstrate vias are not needed for TFMSL matching networks to be functional, throughwafer connections are, nonetheless, required for most MMIC-to-waveguide transitions and the suppression of in-package resonances when considering MMIC packaging. Yet, the necessity of vias within the active circuit area of compact TFMSL MMICs strongly depends on the amplifier topology and device layout used. In order to avoid substrate resonances after packaging, the requirements for via placement were investigated and are described in detail, including design rules for their implementation in TFMSL circuits. To increase the output-power performance on the module level, a low-loss 3-dB waveguide coupler is developed for efficient MMIC parallelization on waveguide level. The measured performance of the packaged PA MMICs is described and discussed in detail in the second part of Chapter 5.

As a basis for the development of multi-finger devices in different device configurations in Chapter 3 and, furthermore, the design of compact PA MMICs discussed in Chapter 4, the IAF-mHEMT MMIC technology is first introduced in Chapter 2. This includes the evaluation of thin-film wiring possibilities in the available BEOL variants—which is required for the feeding of the multi-finger devices, as well as for the design of the compact matching and power combining networks described in this work. In addition, the general PA concepts of parallel-connected as well as series-connected topologies are introduced in Chapter 2 and the corresponding limitations are discussed—this includes, for example, the limitations of stacked-FET topologies at 300-GHz, which are evident from the state-of-the-art evaluation in the previous Section 1.1.1.

A detailed discussion and conclusions of the above-mentioned investigations on device, MMIC, and module level is covered in Chapter 6—which provides a summary of key results, findings, and achievements, which are described in the following chapters.

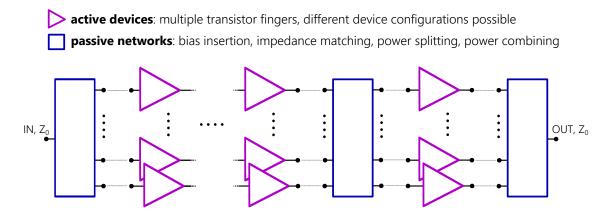

## 2 Analysis of Device Configurations and Thin-Film Transmission Lines

A general block diagram of a typical RF power amplifier topology is shown in Fig. 2.1, consisting of multiple active devices in parallel as well as matching networks for impedance transformation and power splitting/combining. Within a given technology, the implemented topology and choice of active-device configuration can significantly impact key figures such as the achievable bandwidth, gain, output power, and circuit dimensions, for example. Furthermore, a certain topology which shows great potential at the lower mm-wave frequency range, possibly provides no significant benefit at the THz-frequency band around 300 GHz. Hence, the choice of a proper topology is a crucial part of the power amplifier design—including the choice of the active-device configuration as well as the selection of the wiring type for the implementation of the passive impedance transformation networks depicted in Fig. 2.1.

The theoretical analysis of RF power amplifier concepts as well as modeling and design procedures to achieve good linearity, high efficiency, or high bandwidth, for example, are well covered in the literature [12, 21, 35, 92]. This chapter's aim is to introduce the underlying InGaAs-channel mHEMT technology and to provide an analysis of the abovementioned two key building blocks for the realization of highly-compact 300-GHz PA circuits: the transistor configuration of the active devices as well as the monolithic transmission lines for the implementation of compact matching networks and low-loss power combiners. The results of these evaluations will be required for the discussion of the modeling and design approach of multi-finger devices and chip-size-optimized PA MMICs described in the following chapters.

**Figure 2.1:** General block diagram of an RF power amplifier, consisting of parallel active devices and matching networks. The active device configurations and wiring possibilities for sub-mm-wave PA circuits are discussed in detail in this chapter.

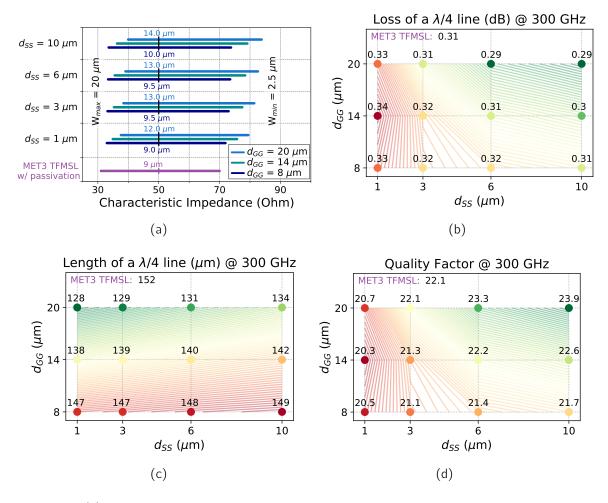

The MMIC fabrication including transistors, capacitors, resistors, and multiple metal layers for interconnections is, in general, divided into two parts. The front-end-of-line (FEOL) part consists of the processing of the active devices, including the epitaxial growth of the heterostructure, mesa etching, and gate processing. The processing of metal and dielectric layers which are used for matching and bias-insertion network design, on the other hand, is generally included in the BEOL part of the fabrication. III-V HEMT and HBT technologies on GaAs and InP substrates, furthermore, typically feature a backside process including wafer thinning and through-substrate-via processing, which is required for packaging and most MMIC-to-waveguide transitions.

In the following section (Section 2.1), the FEOL of the InGaAs-channel mHEMT technology is introduced, including key device figures which are relevant for the achievable PA performance at the lower THz band. In Section 2.2, the basic concepts and limitations of parallel-connected and series-connected devices for 300-GHz power amplifiers are introduced, taking into account the relevant characteristics of the used HEMT technology. The available BEOL variants, along with thin-film transmission lines, are then discussed in detail in Section 2.3.

### 2.1 Metamorphic High-Electron-Mobility Transistor Technology

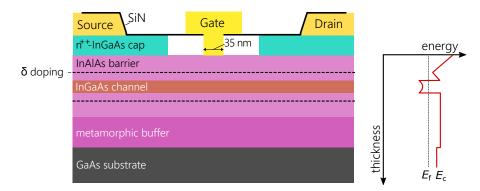

Fraunhofer IAF's 35-nm gate-length mHEMT devices are based on an InGaAs/InAlAs double heterostructure with high In-content in the InGaAs channel [65, 64, 66]. Fig. 2.2 shows the simplified cross section of the HEMT devices, which are processed on 100-mm semi-insulating GaAs wafers by molecular beam epitaxy (MBE). To adapt the lattice constant of the GaAs substrate, a ternary grown metamorphic buffer is used, with a linear In<sub>x</sub>Al<sub>0.48</sub>Ga<sub>0.52-x</sub>As (x = 0  $\rightarrow$  0.52) transition. The electrons are confined in a single In<sub>0.8</sub>Ga<sub>0.2</sub>As layer, using In<sub>0.52</sub>Al<sub>0.48</sub>As barriers with double-sided  $\delta$ -doping. The heterostructure is capped with a highly doped In<sub>0.53</sub>Ga<sub>0.47</sub>As-cap layer for reduced ohmic contact and low source resistance. The corresponding band diagram of this layer sequence is shown in Fig. 2.2 on the right.

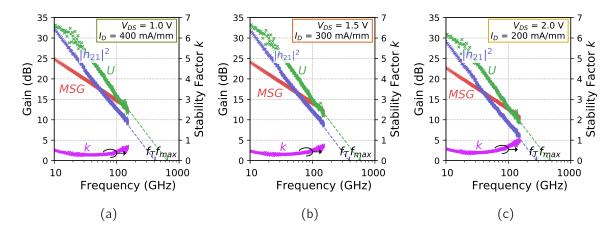

Typical device characteristics of a single HEMT are listed in Fig. 2.3 on the right. The mHEMT devices have been developed for MMIC applications up to 800 GHz, featur-

Figure 2.2: Simplified cross section of Fraunhofer IAF's 35-nm gate-length mHEMT and an illustration of the corresponding conduction band edge diagram.

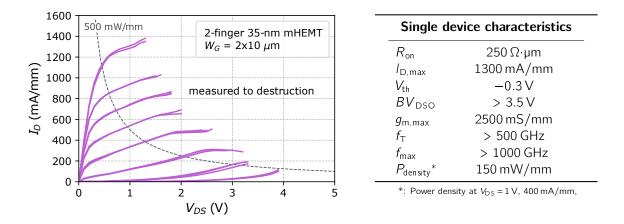

**Figure 2.3:** Output characteristics (left) and typical characteristics (right) of a 35-nm InGaAs-channel mHEMT 2-finger device with  $2\times10$ -µm gate width ( $W_{\rm G}$ ).

ing a transition frequency  $f_{\rm T}$  and power-gain cutoff frequency  $f_{\rm max}$  above 500 GHz and 1000 GHz, respectively. For power-amplifier development, the current and voltage limits are of particular interest. Therefore, the output characteristics of devices which have been measured to destruction by sweeping the drain-source voltage at a constant gate voltage, are depicted on the left in Fig. 2.3. At a knee voltage of 0.6 V, the saturation current  $I_{\rm D,max}$  is typically in the range of 1200 to 1300 mA/mm and the off-state drain-source breakdown voltage  $BV_{\rm DSO}$  is above 3.5 V. Hence, at a typical bias condition of 1 V and 400 mA/mm for PA applications, the power density on device level is around 120 to 150 mW/mm in load-pull measurements at the lower mm-wave frequency band. Device configurations and PA concepts to increase the output power on MMIC level, are discussed in the following section.

### 2.2 Concepts and Device Configurations for sub-mm-Wave Power Amplifiers

In general, the maximum output power—which is achievable with a single transistor—is fundamentally limited by the current and voltage limitations of the underlying device technology. In order to increase the output power for a given technology, single devices are connected in series and/or in parallel to increase the output power level by voltage and/or current combining.

#### 2.2.1 Parallel-Connected Power Amplifier Concepts

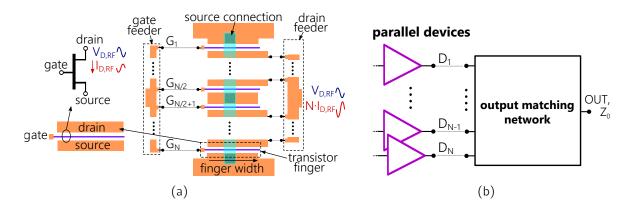

The most straightforward method to increase the output power in PA circuits on device level is to increase the current swing by maximizing the total gate width. This is done by means of maximizing the single-finger width as well as the number of transistor fingers per device, as depicted in Fig.2.4(a).

Increasing the finger width, however, impacts the achievable gain, bandwidth, and the maximum frequency of operation. This is due to the fact that parasitic device capacitances as well as ohmic losses of the transistor fingers scale with the finger width,

Figure 2.4: Simplified (a) N-finger common-source device and (b) schematic view of the parallelconnected amplifier topology, which is used to increase the output-power performance by combing the current of multiple parallelized devices or circuits.

limiting the extrinsic cutoff frequencies and achievable gain. Furthermore, additional losses and phase imbalances, introduced by the feeding structures of multi-finger devices, can impact the single-device performance in a similar way—limiting the achievable gain, bandwidth and output power on the device level. Especially at sub-mm-wave frequencies, and due to the increasing electrical length of multi-finger feeding structures, this impact cannot be neglected and is evaluated in detail in Section 3.2.1.

To further increase the total gate width in PA circuits and, hence, increase the output power, several multi-finger devices or prematched multi-transistor power cells are parallelized, as illustrated in Fig. 2.1. This N-way parallelization is realized using outputmatching and power-combining circuits to match the system impedance  $Z_0$  to the output of the parallelized devices, as shown in Fig. 2.4(b). Assuming ideal and lossless power combining—which is far from being attainable in practice at sub-mm wave frequencies the output power scales with the number N of parallel devices according to

$$P_{\rm OUT,N} = N \cdot I_{\rm DS,RF} \cdot V_{\rm D,RF}, \qquad (2.1)$$

with  $V_{DS,RF}$  and  $I_{D,RF}$  being the RF drain-source voltage and RF drain current, respectively, of the single devices.

By increasing the total gate width and adding up the current on device level, the impedance level—and therefore the optimum load impedance—decreases in accordance to the increasing gate width. Since the ideal load-line resistance decreases by the same number the device capacitances are increasing, the theoretically achievable matching bandwidth is not affected by the increasing impedance-transformation ratio. This is due to the fact, that only the product  $R \cdot C$  of the capacitance C and the resistance R of an RC-parallel element is relevant for the achievable matching limit [10, 30]. The achievable insertion loss as well as feasible power combining efficiency, on the other hand, is limited by the larger impedance-transformation ratios which need to be covered by the matching networks [13, 85]. Hence, high-order impedance-transformation networks are required to achieve broadband matching—decreasing the combining efficiency at sub-mm-wave frequencies due to high transmission-line losses—and the chip dimensions of power amplifier circuits tend to get large in comparison to other circuit components. This, however, imposes a major challenge for the assembly of the PA circuit as well

on-chip integration into complex front-end MMICs. Since compact chip dimensions are a key parameter of the developed PA cells in this work, the implementation of chip-sizeoptimized multi-finger devices is described in Chapter 3.

#### 2.2.2 Series-Connected Power Amplifier Concepts

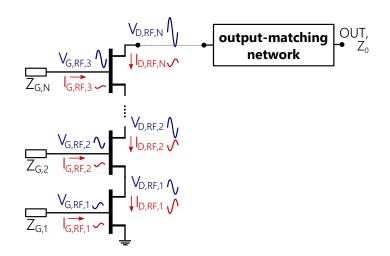

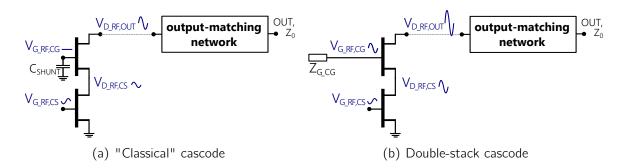

In contrast to the parallel-connected current-combing PA topology, the stacking of multiple transistors in a series-connected device configuration potentially provides benefits in terms of gain, reduced chip size as well as higher output-impedance levels [101]. The simplified schematic of the stacked-FET topology with N in series-connected devices is shown in Fig. 2.5. The depicted voltage and current swings indicate the general behavior in the stacked-FET configuration—yet both phase and amplitude are not to scale.

The input signal is applied to the lowest device in common-source configuration, acting as a current source for the *N*-1 stacked devices in common-gate configuration. By adding up the drain-source voltages of the *N* in series connected FETs, the outputvoltage swing—and, hence, the output power—is increased. In order to realize an increased voltage swing, the voltages need to be added and swing in phase. To achieve this, the depicted voltage swing at the gates of the common-gate devices needs to be implemented. This can be achieved by careful selection of the passive gate impedances  $Z_{G,2}$  to  $Z_{G,N}$ , as well as possible impedance transformation networks in-between the stacked devices, which are not depicted in Fig. 2.5.

As mentioned above, a significant benefit of the increased output-voltage swing is the higher output and load impedance, reducing the effort for impedance matching and permitting more efficient broadband output matching. Furthermore, by stacking the devices in series, the chip width is only increased by the layout dimensions of the required impedance matching networks at the gates of the CG devices. Hence, by combining multiple devices in a series-connected topology, compact and chip-size-efficient power gain becomes feasible.

Figure 2.5: Simplified schematic of N in-series connected transistors, a topology which is used to increase the output-power performance by voltage combining. The depicted voltage and current swings indicate the general behavior—both phase and amplitude are not to scale.

Yet, the maximum number of devices which can be stacked to increase the outputpower level is limited—as described with the prospects and limitations of stacked-FET approaches in [114, 115]. Since the current gain of the CG devices is smaller than unity and the RF gate current of each stage is contributing to the respective source current, the output current swing of an *N*-stacked FET is reduced with each additional CG device:

$$I_{\mathsf{D},\mathsf{RF},\mathsf{N}} < I_{\mathsf{D},\mathsf{RF},\mathsf{N}-1}.$$

(2.2)

Furthermore, with the dependency of the current gain on the transit frequency  $f_{T}$  as well as the frequency of operation  $f_{op}$ , the maximum achievable output power with N stacked devices is given in [115] by

$$P_{\text{OUT,N}} = N \cdot V_{\text{DS,RF,1}} \cdot I_{\text{D,RF,1}} \left(\frac{f_{\text{T}}}{f_{\text{op}} + f_{\text{T}}}\right)^{N-1}.$$

(2.3)

Due to the linear voltage-related growth and the exponential current-related decrease of the output power, in dependency on N, an optimum number of  $N_{\text{max}}$  stacked devices for maximum output-power performance exists and can be calculated from (2.3). This maximum number of stacked devices is given by

$$N_{\max} = \left( ln \left( 1 + \frac{f_{\text{op}}}{f_{\text{T}}} \right) \right)^{-1}.$$

(2.4)

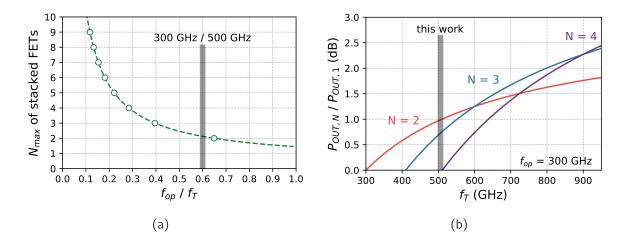

The optimum number of stacked devices is, therefore, dependent on the ratio of the frequency of operation  $f_{op}$  to the current-gain cutoff frequency  $f_T$  of the corresponding semiconductor technology. This dependency of  $N_{max}$  versus  $f_{op}$  normalized to  $f_T$ , is depicted in Fig. 2.6(a).

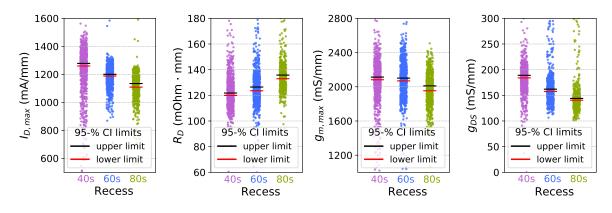

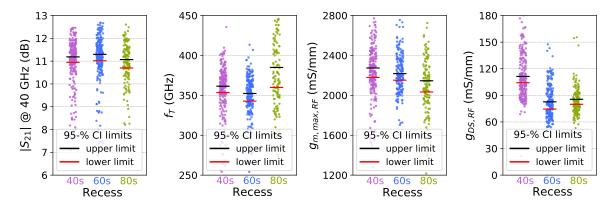

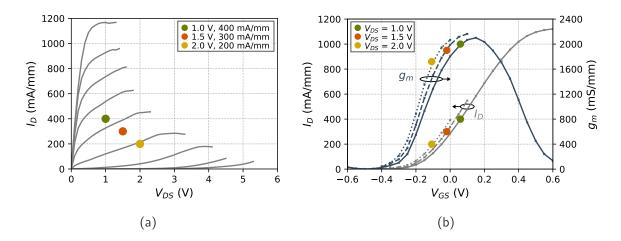

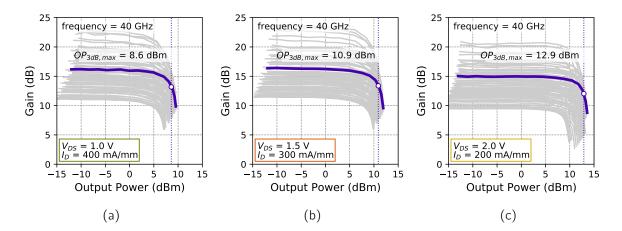

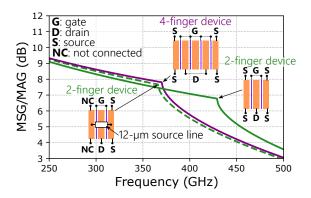

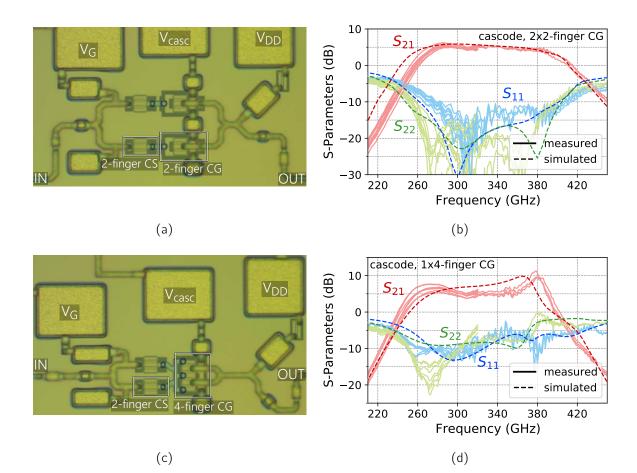

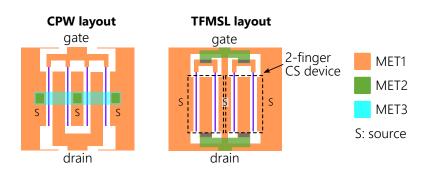

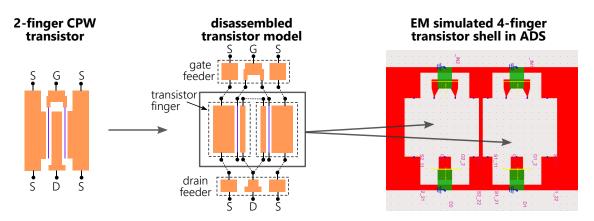

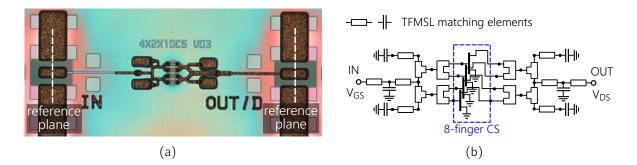

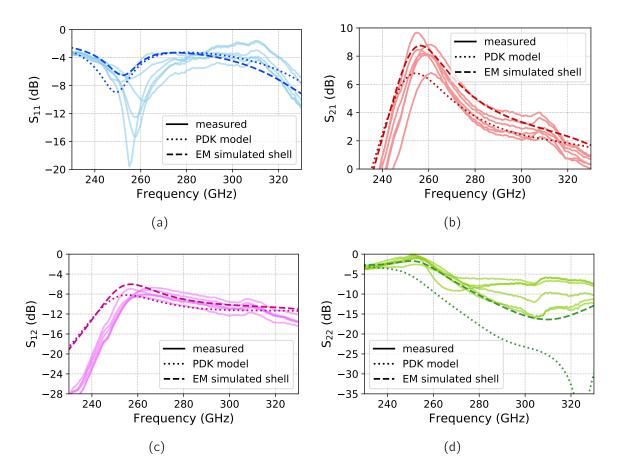

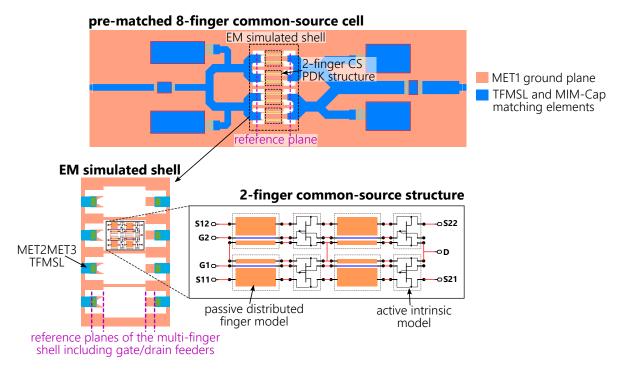

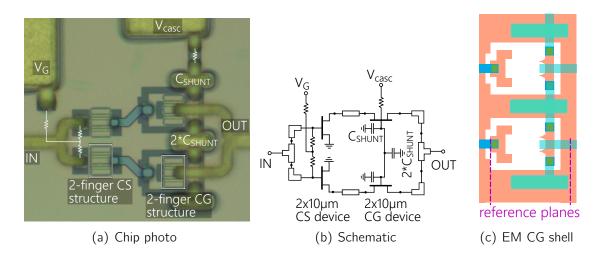

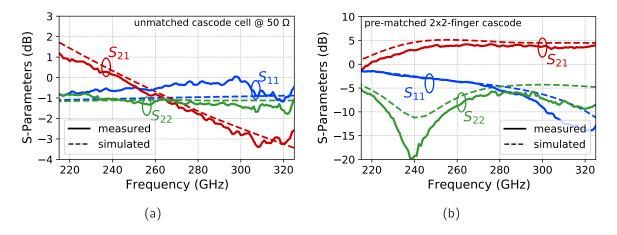

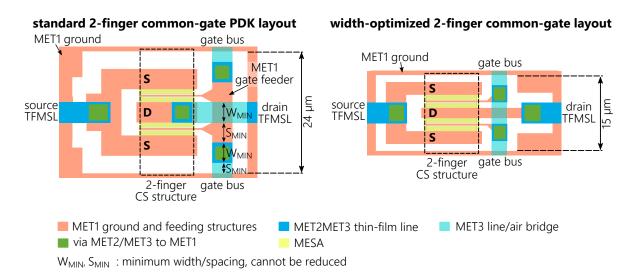

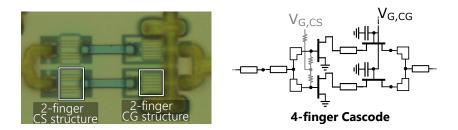

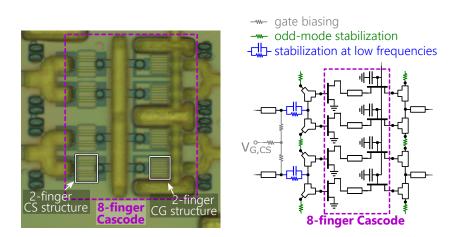

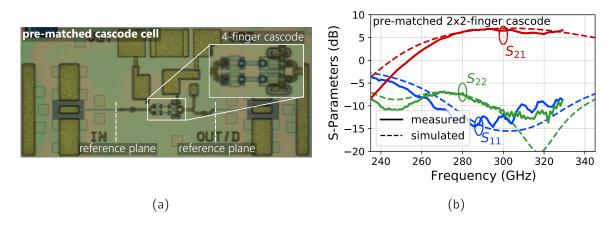

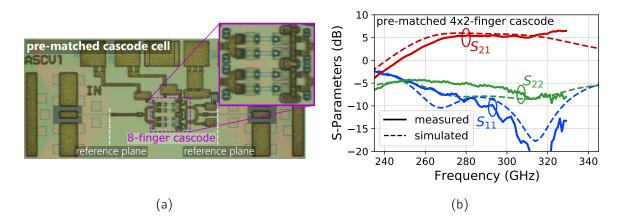

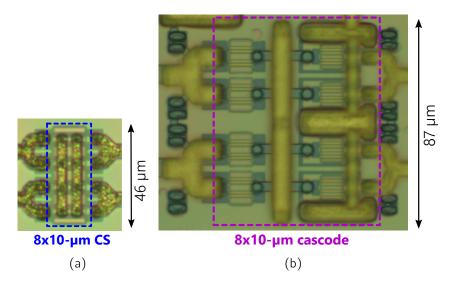

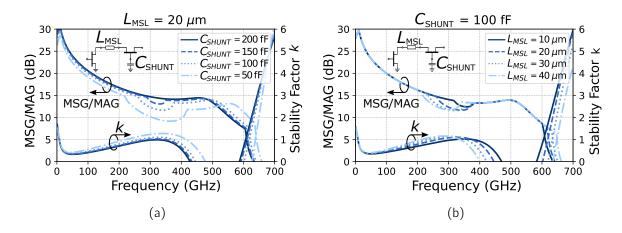

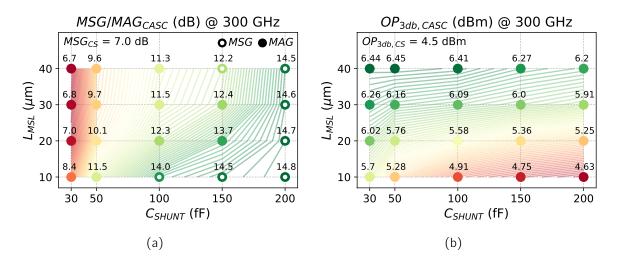

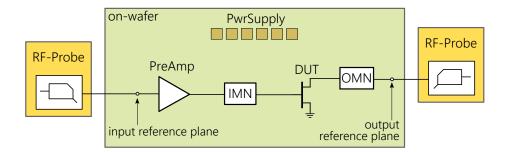

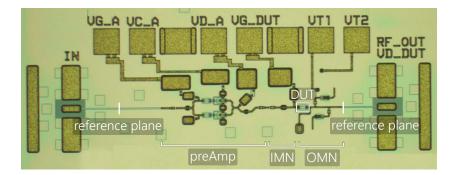

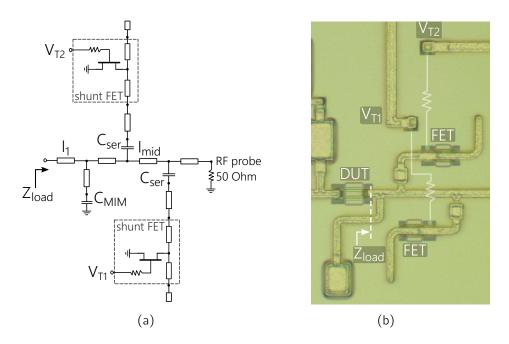

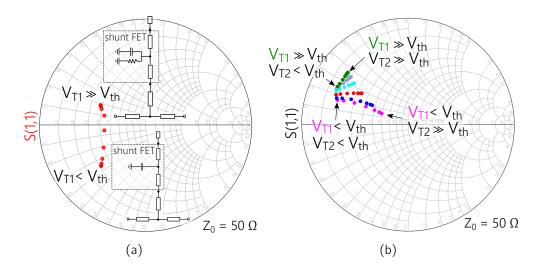

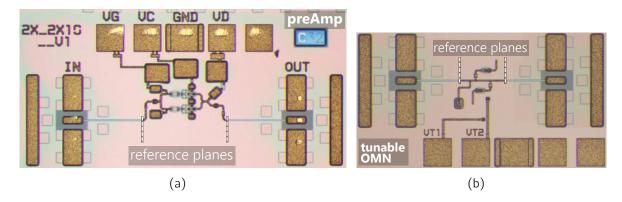

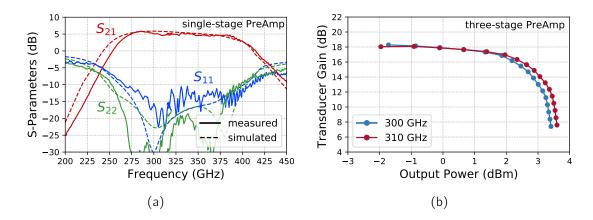

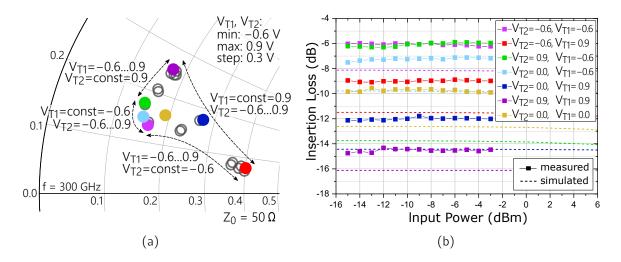

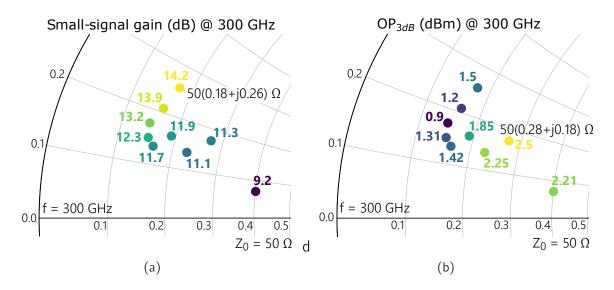

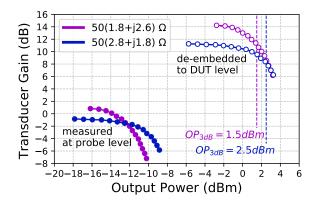

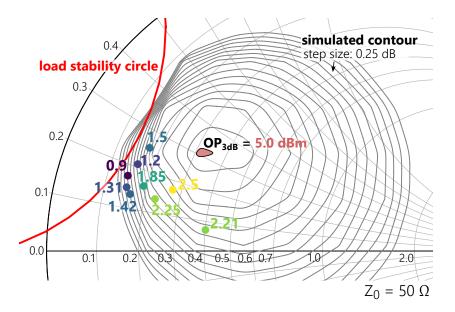

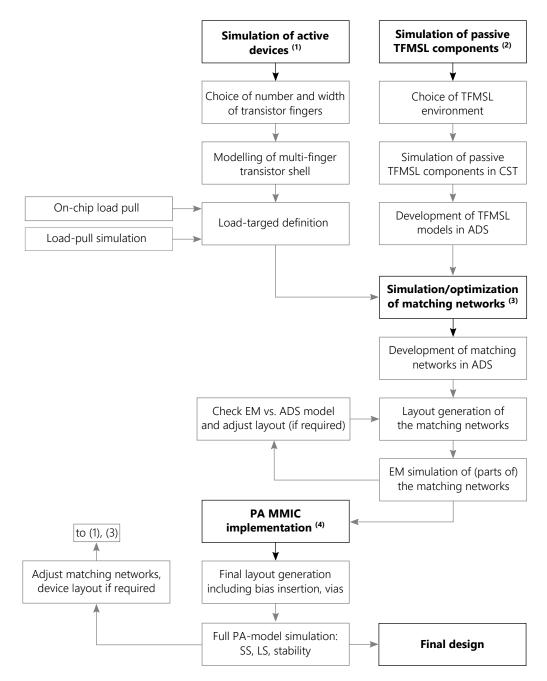

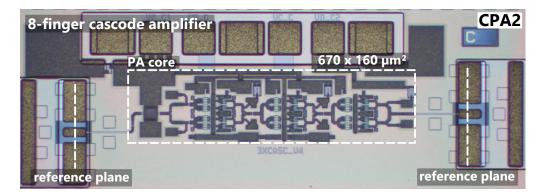

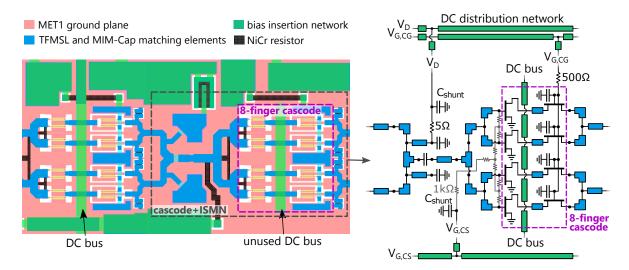

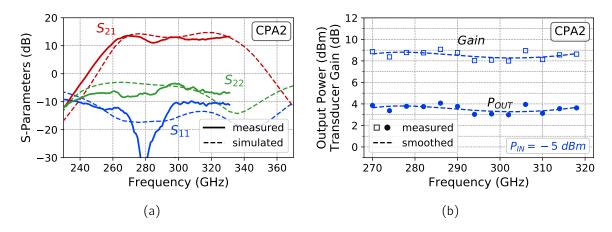

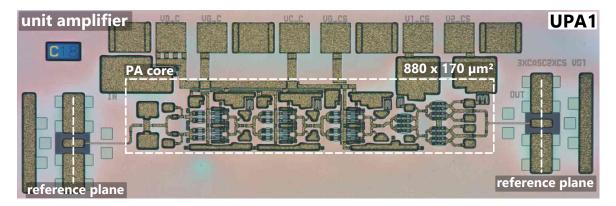

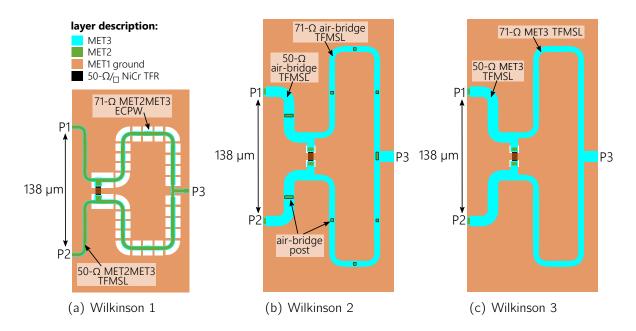

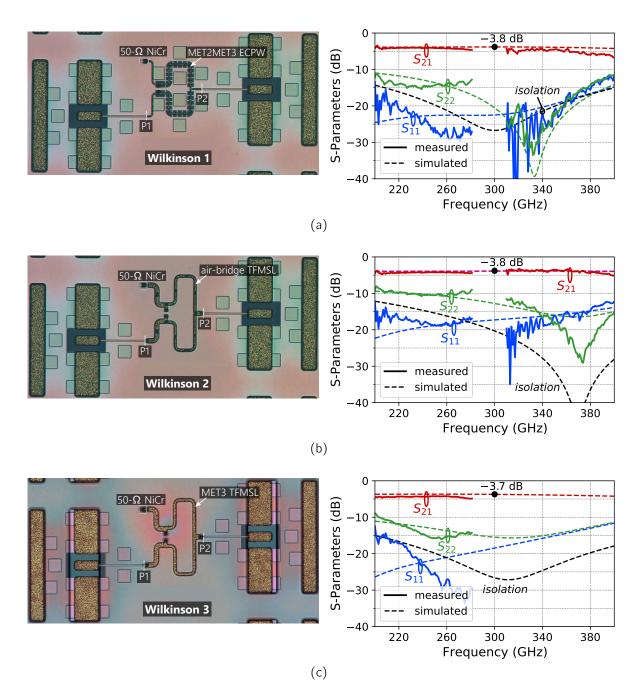

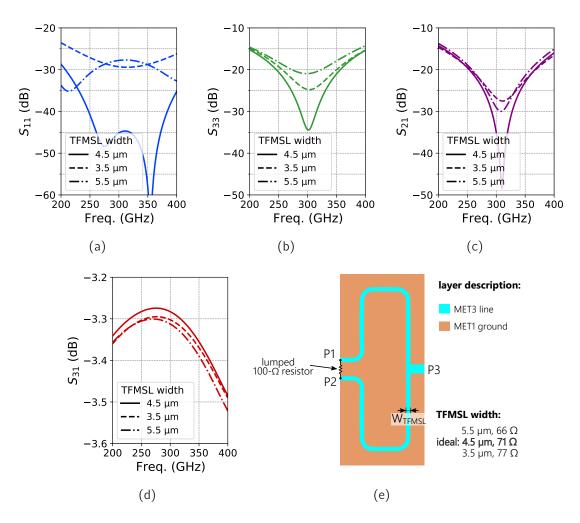

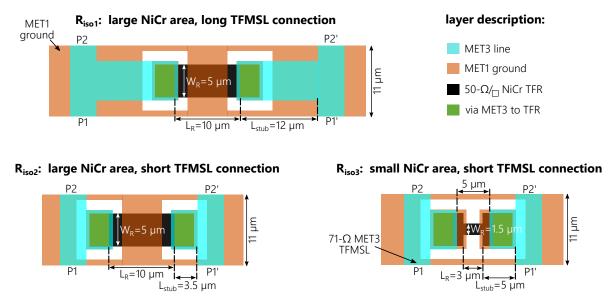

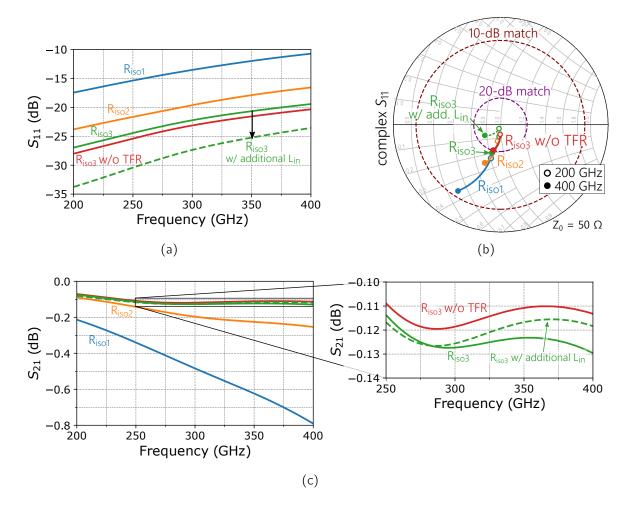

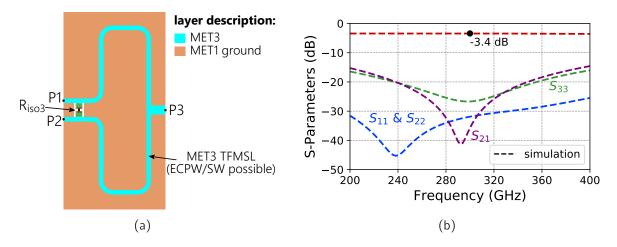

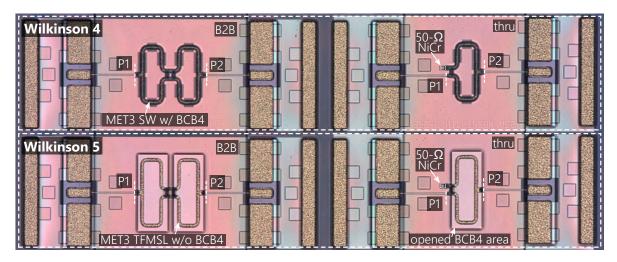

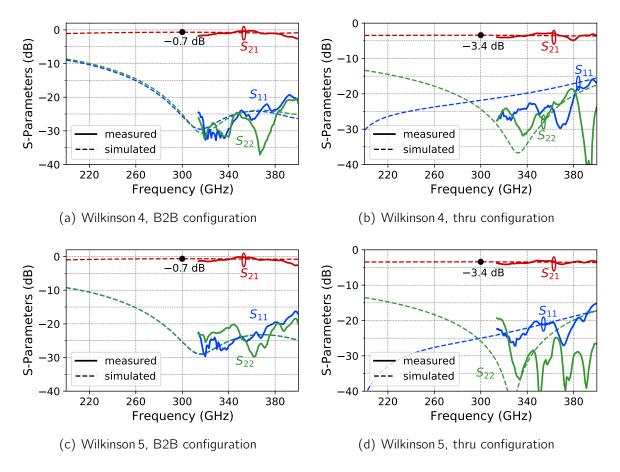

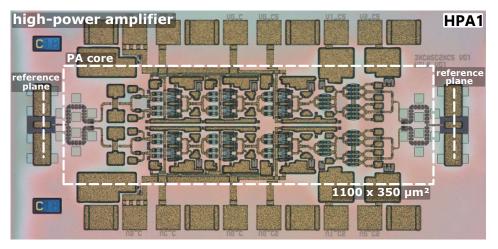

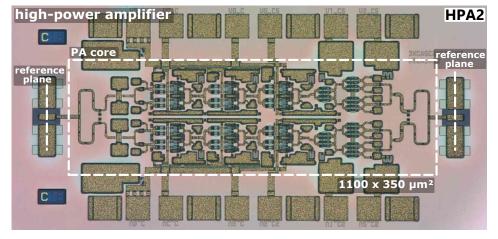

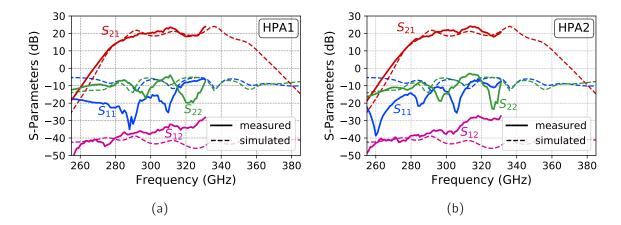

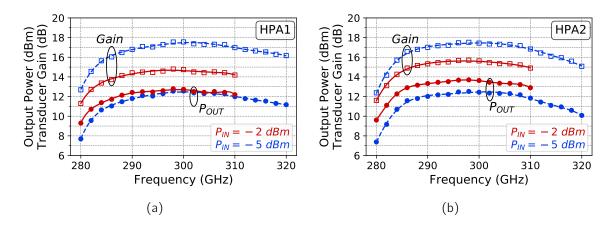

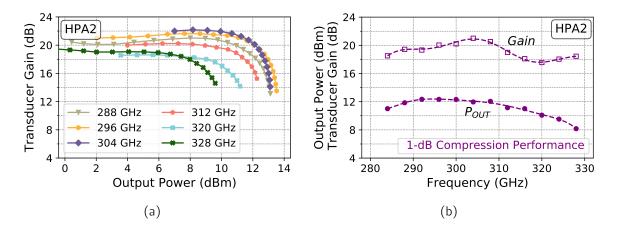

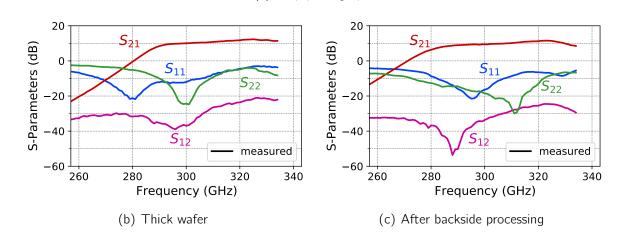

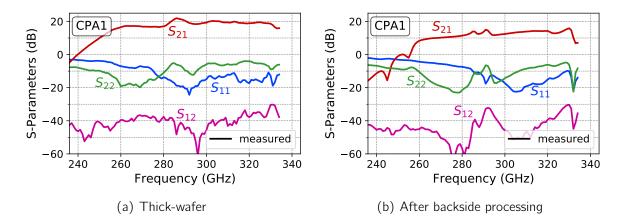

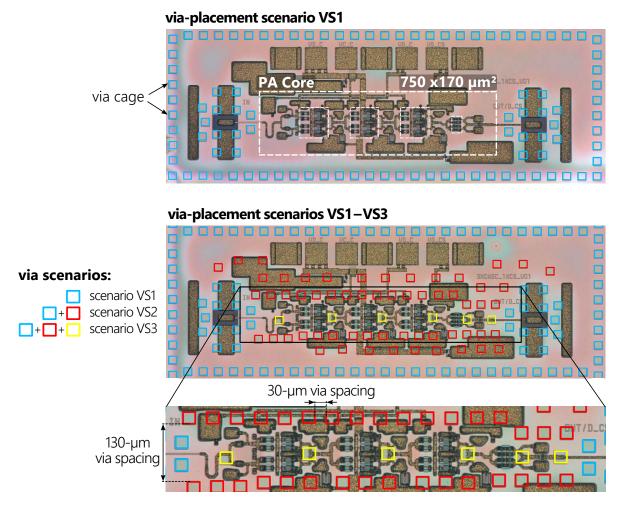

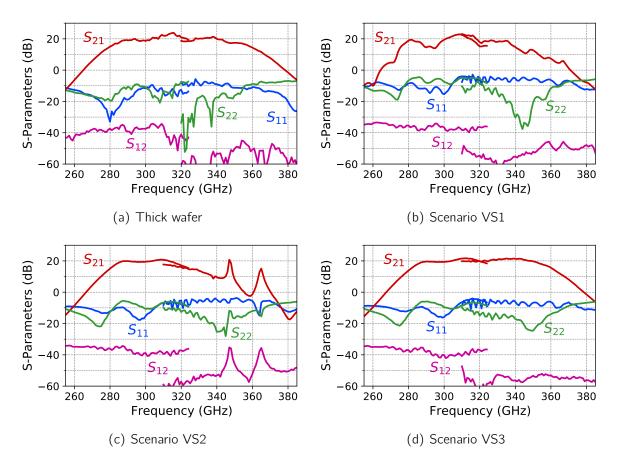

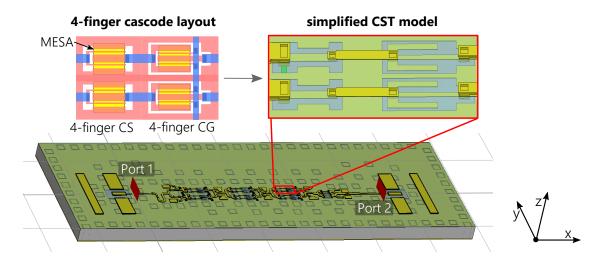

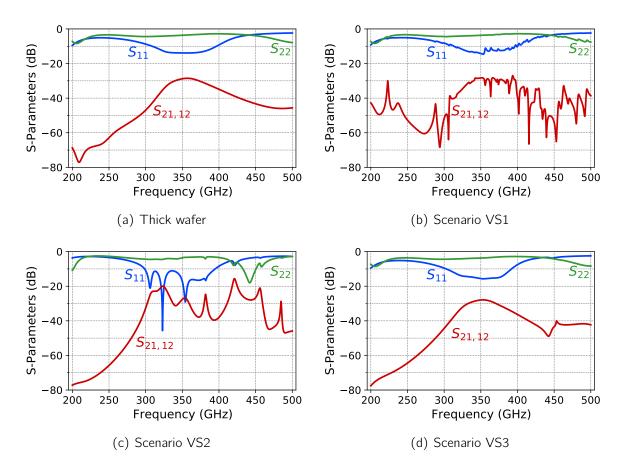

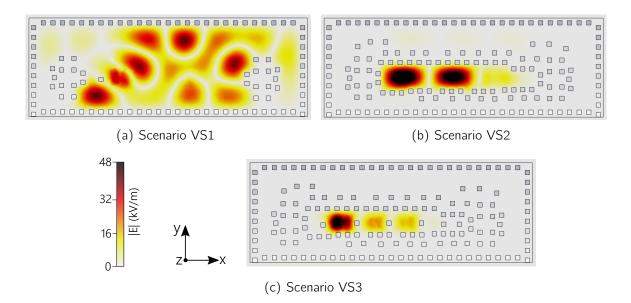

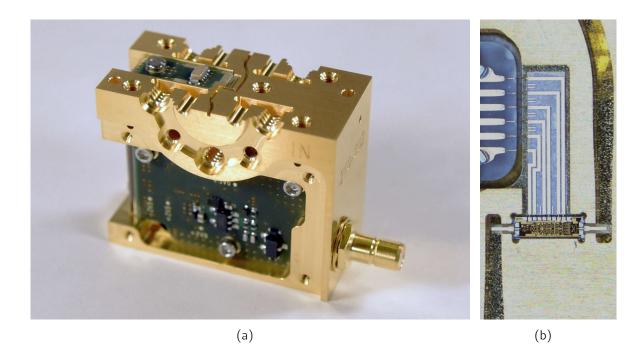

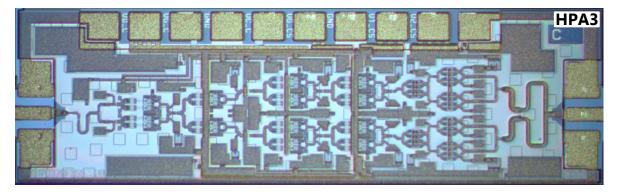

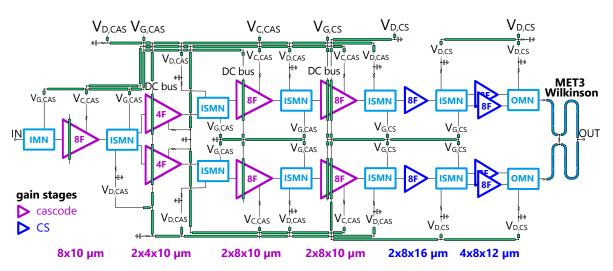

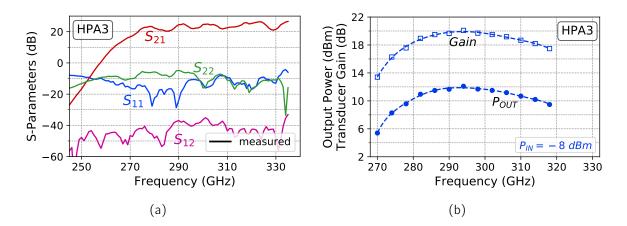

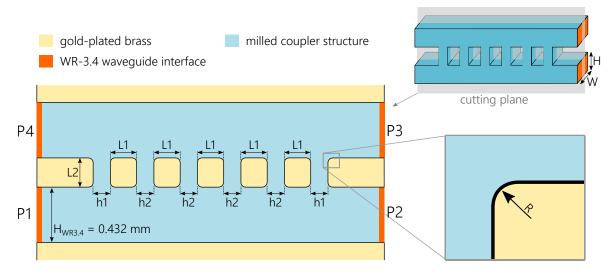

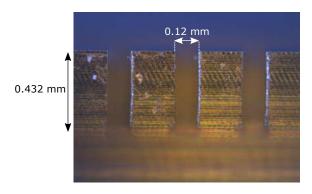

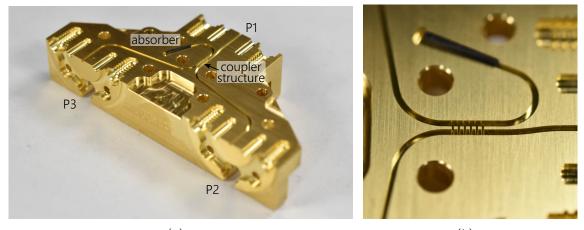

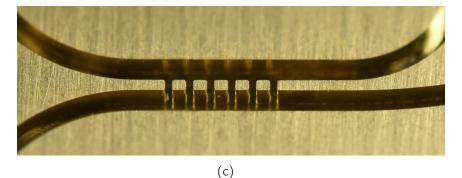

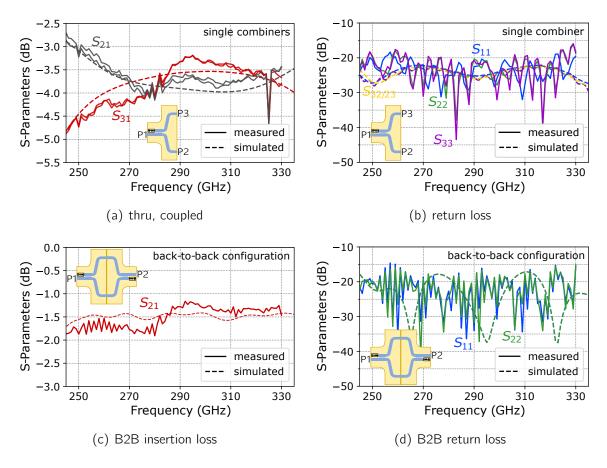

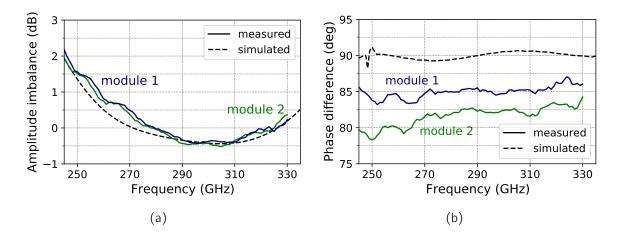

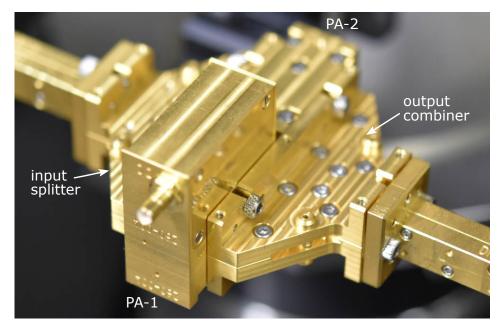

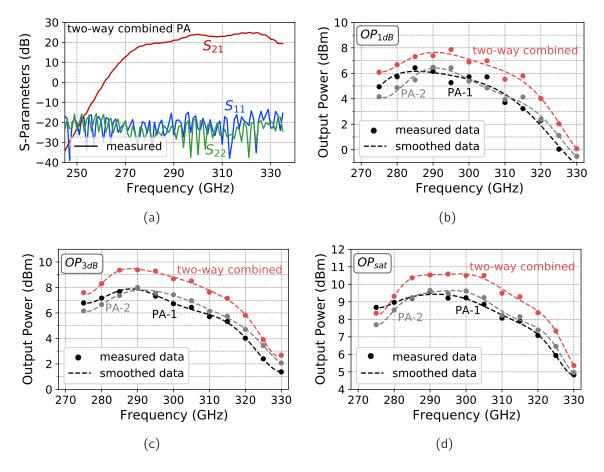

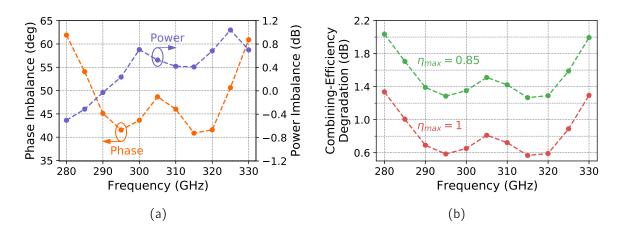

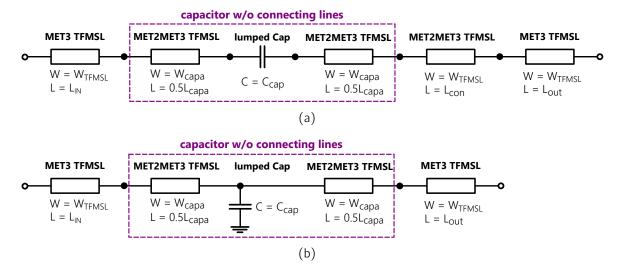

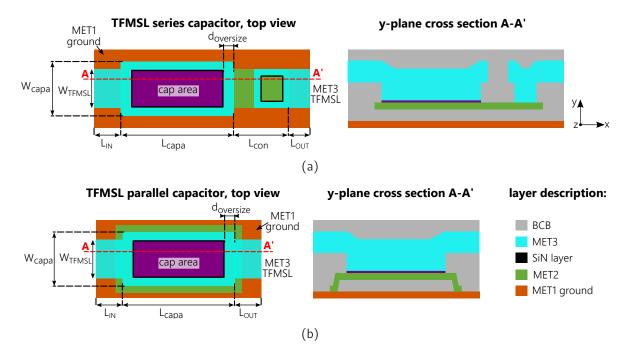

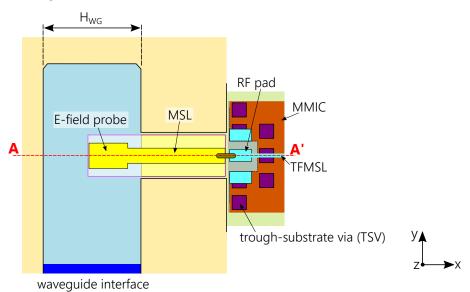

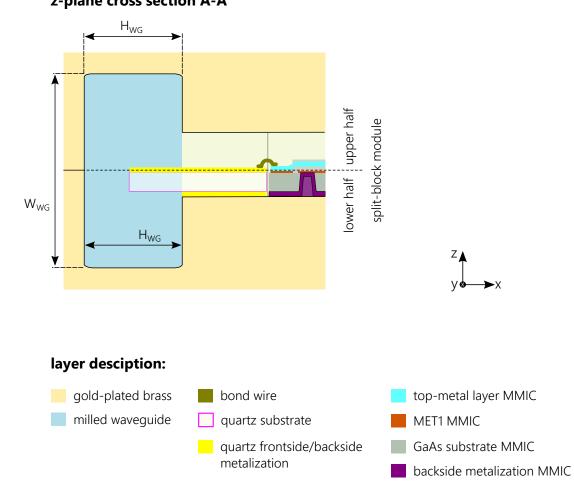

Due to the described current limitation, the stacking of multiple devices is only beneficial at frequencies well below the current-gain cutoff frequency. To stack at least two devices for slightly improved large-signal performance in a cascode configuration, e.g., the frequency of operation needs to be below approximately three-fourths of the underlying technology's  $f_T$ . For the operation of two stacked transistors around 300 GHz, this would require an  $f_T$  larger than 400 GHz. With the  $f_T$  of 500 GHz, this requirement is satisfied for the 35-nm mHEMT technology used in this work.