## HIGH THROUGHPUT SOLAR CELL PROCESSING BY OXIDATION OF WAFER STACKS

M. Meßmer, S. Lohmüller, F. Braun, J. Weber, A. Wolf

Fraunhofer Institute for Solar Energy System (ISE), Heidenhofstr. 2, 79110 Freiburg, Germany Phone: +49 761 4588-2287; e-mail: marius.messmer@ise.fraunhofer.de

ritolie. +49 /01 4300-2207, e-mail. marius.messiner@ise.mauliloier.ue

ABSTRACT: In this work, we investigate two approaches for high throughput emitter formation and thermal oxidation for passivated emitter and rear cells (PERC). The low temperature stack oxidation (LoTSOx) approach uses wafer stacks in the typical low temperature thermal oxidation process in the PERC manufacturing sequence. With the LoTSOx approach, we reach similar energy conversion efficiencies of  $\eta = 22.2\%$  in comparison to state-of-the-art PERC processing but with 3.1 times higher throughput. The second approach, using a shortened low pressure POCl<sub>3</sub> diffusion and a high temperature stack oxidation (HiTSOx approach) with laser-doped selective emitter, yields a peak conversion efficiency of  $\eta = 22.0\%$  and low specific contact resistances  $\rho_c \approx 0.6 \text{ m}\Omega\text{cm}^2$ . We further investigate different diffusion and oxidation processes for the HiTSOx approach resulting in a wide range of emitter sheet resistances  $R_{\text{sh}}$ . We reach low emitter dark saturation current densities of  $j_{0e} = 12 \text{ fA/cm}^2$  at  $R_{\text{sh}} = 389 \Omega/\text{sq}$  while stacking the wafers during the oxidation process.

Keywords: High throughput, wafer stacks, LP-POCl<sub>3</sub> diffusion, thermal oxidation, HiTSOx

### 1 INTRODUCTION

The passivated emitter and rear cell (PERC) [1, 2] is the mainstream solar cell device structure. According to ITRPV (international technology roadmap) expert survey it is expected to remain in this leading market share position for the coming years [3]. In addition, a significant increase in the production tool throughput is predicted [3]. Several process steps in the fabrication of PERC solar cells must be adapted to reach high throughputs. For this, several approaches are under investigation [4]. The PERC sequence usually incorporates a phosphorus oxychloride (POCl<sub>3</sub>) diffusion after texturing to form the emitter as well as a low temperature oxidation / annealing process between chemical edge isolation and plasma enhanced chemical vapor deposition (PECVD) for passivation [2]. Newest generations of tube furnaces can process up to 1,600 wafers per process tube.

The aim of this work is to strongly increase the production tool throughput of the thermal processes while maintaining a high solar cell performance. We increase the potential throughput by a factor up to 3.1 by implementation of horizontally stacked wafers during the oxidation process. Two approaches are investigated: (i) the low temperature stack oxidation (LoTSOx) which is based on stacking wafers in the low temperature thermal oxidation process typically used in the PERC sequence as surface passivation, and (ii) the high temperature stack oxidation (HiTSOx) [5, 6] for simultaneous emitter drive-in and surface passivation. For the latter, the diffusion process is adapted. Both approaches are implemented in the PERC fabrication sequence.

# 2 HIGH THROUGHPUT APPROACHES

#### 2.1 Low temperature stack oxidation LoTSOx

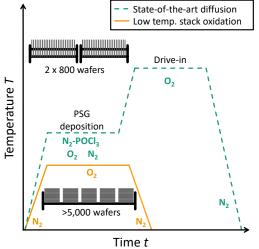

The first approach investigated in this paper is the <u>low</u> temperature <u>stack ox</u>idation LoTSOx. This approach follows the typical fabrication sequence for PERC solar cells including thermal oxidation like the baseline process at Fraunhofer ISE [2]. Figure 1 depicts the state-of-the-art diffusion process using phosphorus oxychloride (POCl<sub>3</sub>) as liquid dopant precursor. The subsequent thermal oxidation process features low temperature as mentioned in Ref. [2, 7] and thus hardly affects the doping profile and grows a thin silicon dioxide  $SiO_2$  as a passivation layer. Both processes usually capture 1,600 wafers (M6 configuration). In the LoTSOx approach, a highly increased throughput of more than 5,000 wafers per batch can be achieved by horizontally stacking of the wafers on top of each other, resulting in a 3.1 times higher throughput. It can be used for solar cells with homogeneous or selective emitter.

**Figure 1:** Schematic illustration of the state-of-the-art tube furnace POCl<sub>3</sub> diffusion process as a function of the temperature *T* over time *t* with a typical process throughput of 1,600 wafers (M6 configuration). Further, the low temperature stack oxidation (LoTSOx) with a throughput of more than 5,000 wafers is illustrated.

#### 2.2 High temperature stack oxidation HiTSOx

The <u>high</u> temperature stack <u>ox</u>idation HiTSOx has already been introduced in Ref. [5, 6]. It uses adapted POCl<sub>3</sub> diffusion shortened to only the deposition phase. Thereby, the throughput of the diffusion process is increased by a factor of 1.8. Laser doping from this phosphosilicate glass (PSG) layer [8, 9] shows high suitability [5] for the formation of a laser-doped selective emitter (LDSE) and is used for solar cell processing in this work. Homogeneous emitter formation with the HiTSOx approach is also possible but not investigated here. The drive-in of the phosphorus atoms is shifted to the thermal oxidation process where again horizontally stacking of the wafers increases the throughput to more than 5,000 wafers per batch, increasing the throughput by a factor of 2.4. This stack oxidation process features plateau temperatures in the range of typical drive-in temperatures between  $850^{\circ}C < T_{\text{plateau}} < 900^{\circ}C$  [6]. During this process, the phosphorus incorporated in the silicon is redistributed and diffuses in further. At the same time, a silicon dioxide SiO<sub>2</sub> grows on the wafer surface, which serves as a passivation layer in combination with a hydrogen rich capping layer.

A cost of ownership (COO) calculation for the HiTSOx approach shows a COO reduction of 41% compared to the state-of the art approach [4]. In this calculation, M6 sized wafers and a possible throughput of 1,600 wafers per process tube for state-of-the-art diffusion and thermal oxidation are taken into account.

## 3 EXPERIMENT

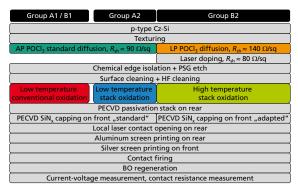

In this investigation, two solar cell batches are manufactured, as depicted in Figure 2. Group A1 and B1 represent the respective reference groups with common PERC fabrication sequence featuring a homogeneous emitter. Group A2 is meant for investigating the low temperature stack oxidation LoTSOx approach as described in section 2.1 and Group B2 the high temperature stack oxidation (HiTSOx) approach as described in section 2.2. For the manufacturing, we use M2 p-type boron-doped Cz-Si wafers with a base resistivity of  $\rho_b \approx 0.8 \ \Omega cm$ . An alkaline texturing process (including saw-damage etching, texturing and surface cleaning) is performed for all groups prior to the diffusion processes. An atmospheric pressure (AP) POCl<sub>3</sub> diffusion process forms the homogeneous emitter for the reference groups as well as for the LoTSOx approach in Group A2. For the HiTSOx approach in Group B2, an adapted low pressure (LP) POCl<sub>3</sub> diffusion with only the deposition step is performed [6]. Laser diffusion from the phosphosilicate glass (PSG) forms the highly doped region of the selective emitter [8, 9] in Group B2. Then, for all groups, a chemical edge isolation process removes the emitter on the rear side, including the PSG removal on both sides. Subsequently, a wet chemical surface cleaning oxidizes a very shallow part of the emitter surface. The grown oxide is then removed in diluted hydrofluoric acid (HF) prior to the thermal oxidation processes. For the

**Figure 2:** Experiment plan for two solar cell batches A and B, whereby the reference groups A1 and B1 are fabricated similarly. Group A2 represents the low temperature stack oxidation approach (LoTSOx) and Group B2 the high temperature stack oxidation (HiTSOx) approach.

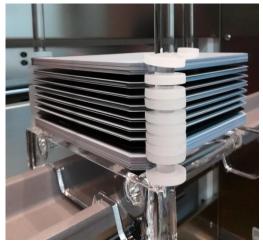

reference groups, a conventional low temperature oxidation process [2, 7] is used (one wafer per slot in vertical orientation), whereas for Group A2, a similar process is used but in this case with horizontally stacked wafers in an experimental setup, see Figure 3. For Group B2, an adapted high temperature stack oxidation is performed. Subsequently, the rear side of all groups is deposited with a passivation stack of AlOx/SiOxNy/SiNz using plasma enhanced chemical vapor deposition (PECVD). For the front side, silicon nitride (SiN<sub>x</sub>) is also deposited by PECVD, serving as anti-reflection coating and surface passivation. For Group A1/2 and B1, the "standard" SiNx layer is used. For Group B2, a layer adapted in thickness is used to maintain low reflectance. After passivation, some samples (fabricated in a different batch) are fired and measured by quasi-steady-state photoconductance (QSSPC) to determine the implied open-circuit voltage  $iV_{oc}$ . For the cells, an infrared laser process locally removes the rear stack layers to form a dotshaped local contact opening (LCO) for the remaining samples. The metallization is applied using screenprinting. For the rear side a full-area aluminum paste is used. The front side contains 120 fingers without busbars printed in a silver grid. After screen-printing, contact firing is performed in an industrial conveyor belt furnace with variation in the peak temperature. Then, the PERC cells are regenerated to mitigate boron-oxygen (BO) related light-induced degradation [10]. Finally, current-voltage measurements are performed in an industrial inline cell tester. For characterization, 1 cm-wide stripes are cut from selected solar cells to determine the specific contact resistance  $\rho_c$  for the front contact according to the transfer length measurement (TLM) [11].

Besides the PERC cell fabrication, symmetric lifetime samples are fabricated to investigate the emitter dark saturation current density  $j_{0e}$  of different combinations of diffusion and oxidation processes. Therefore, *n*-type Cz-Si wafers with a base resistivity of  $\rho_b \approx 6 \ \Omega \text{cm}$  are used. After the texturing sequence, a variation in POCl<sub>3</sub> diffusion is performed (four different LP POCl<sub>3</sub> processes and the reference AP POCl<sub>3</sub> process). Then, the PSG is wet chemically cleaned. The thermal oxidation is varied using five different high temperature stack oxidations and the reference low temperature oxidation. The variations in diffusion and oxidation aim to cover a wide range of

**Figure 3:** Experiment setup for stack oxidation processes. In this quartz boat, wafer groups can be separated by quartz rings.

emitter sheet resistances  $R_{\rm sh}$  which is measured by means of inductive coupling [12]. Subsequently, both sides are passivated with either the standard SiN<sub>x</sub> for the reference group or the adapted SiN<sub>x</sub> for the HiTSOx approach applied by PECVD and the samples are fired. These symmetrical test samples are then characterized using QSSPC measurements to determine the effective lifetime at five spots per sample. Then,  $j_{0e}$  is obtained by the procedure described in Ref. [13].

#### 4 RESULTS

### 4.1 LoTSOx

Table 1 shows the current-voltage characteristics for the LoTSOx approach (group A2 in Figure 2) and the reference process sequence (group A1 in Figure 2) measured in an industrial cell tester after BO regeneration. Comparing the median results of the measurement shows that the LoTSOx approach as well as the reference process sequence result in PERC solar cells with an energy conversion efficiency  $\eta$  of  $\eta \approx 22.2\%$ . The short-circuit current density  $j_{sc}$  and the open-circuit voltage  $V_{oc}$  are measured to be  $j_{sc} \approx 40.4 \text{ mA/cm}^2$  and  $V_{oc} \approx 673 \text{ mV}$ , respectively, while the fill factor is about  $FF \approx 81.7$  %. The best PERC cells in this investigation yield  $\eta = 22.2\%$ for both process sequences. In the investigation in Ref. [5], we found that free-standing wafers in a thermal oxidation process show an about 3 nm thicker silicon dioxide in comparison to stacked wafers. Apparently, the different behavior of the silicon dioxide growth has no significant influence on the solar cell performance as the results are independent on the loading configuration that was used for the thermal oxidation process.

To summarize, the LoTSOx approach enables high throughput thermal oxidation processes without energy conversion efficiency losses due to stacking.

**Table 1:** Current-voltage characteristics of the PERC solar cells fabricated by LoTSOx approach (A2) as well as for the reference group (A1). The median and the best cell for each group are shown. The number of cells per group is shown in brackets. The measurements are performed by an industrial cell tester after boron-oxygen regeneration.

|                            | Process<br>sequence | $j_{ m sc}$ / (mA/cm <sup>2</sup> ) | V <sub>oc</sub> /<br>mV | FF /<br>%            | η /<br>%             |

|----------------------------|---------------------|-------------------------------------|-------------------------|----------------------|----------------------|

| M<br>e<br>d<br>i<br>a<br>n | Ref<br>(6)          | $40.4 \pm 0.1$                      | 673<br>±<br>1           | $81.7 \pm 0.1$       | $22.2 \\ \pm \\ 0.1$ |

|                            | LoTSOx (4)          | $40.4 \pm 0.1$                      | 673<br>±<br>1           | $81.6 \\ \pm \\ 0.1$ | 22.2<br>±<br>0.1     |

| B<br>e                     | Ref                 | 40.4                                | 673                     | 81.7                 | 22.2                 |

| s<br>t                     | LoTSOx              | 40.4                                | 674                     | 81.7                 | 22.2                 |

#### 4.2 HiTSOx

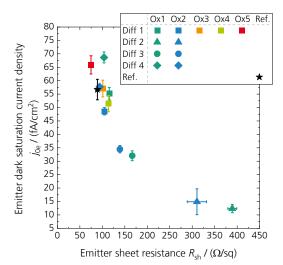

The emitter sheet resistance  $R_{sh}$  and the emitter dark saturation current density  $j_{0e}$  measured using the symmetric lifetime samples are shown in Figure 4 for the variation of LP POCl<sub>3</sub> diffusion processes and high temperature stack oxidation processes in the HiTSOx

**Figure 4:** Emitter dark saturation current density  $j_{0e}$  on textured surfaces after SiO<sub>2</sub>/SiN<sub>x</sub> passivation and firing as a function of the emitter sheet resistance  $R_{sh}$ .

approach. This investigation shows  $j_{0e}$  between  $12 \text{ fA/cm}^2 < j_{0e} < 69 \text{ fA/cm}^2$  within a wide range of emitter sheet resistance of 389  $\Omega/sq > R_{sh} > 73 \Omega/sq$ . With stacking the wafers during high temperature oxidation,  $j_{0e}$ down to  $j_{0e} = (12 \pm 2) \text{ fA/cm}^2$  at  $R_{sh} = (389 \pm 10) \Omega/\text{sq}$  is reached. For the combination of "Diff 4" and "Ox 2",  $R_{\rm sh}$ and  $j_{0e}$  values similar to the ones for the reference manufacturing sequence  $(j_{0e} = (57 \pm 4) \text{ fA/cm}^2$ at  $R_{\rm sh} = (89 \pm 4) \,\Omega/{\rm sq}$  are achieved. Compared to the reference sequence, the combinations in the HiTSOx approach result in up to 15 nm thicker oxide thicknesses [5]. This is the reason why the  $SiN_x$  thickness needs to be somewhat thinner to maintain low reflectance at 600 nm wavelength. However, the different ratios between SiO<sub>2</sub> thickness and SiNx thickness for the reference group and the HiTSOx combination Diff 4 and Ox 2 does not influence the passivation quality.

The combination of Diff 1 and Ox 1 with  $j_{0e} = (55 \pm 2)$  fA/cm<sup>2</sup> at  $R_{sh} = (115 \pm 1)$  Ω/sq is chosen for the PERC fabrication in Group B2 (compare Figure 2). By the laser doping process, 150 µm-wide finger structures are formed resulting in a local sheet resistance of  $R_{sh} \approx 80$  Ω/sq. The energy conversion efficiency for these PERC cells as well as for the reference group (see Group

B1 in Figure 2) are shown in Table 2 (as also reported in Ref. [6]). The cells of the reference process using AP POCl<sub>3</sub> diffusion for homogeneous emitter formation yield a peak energy conversion efficiency of  $\eta = 22.2\%$ , while the cells with the HiTSOx approach and selective emitter peak at  $\eta = 22.0\%$ . Comparing median results, the reference process reaches  $\eta \approx 22.2\%$  with  $V_{\rm oc} \approx 675 \,\mathrm{mV}$ while the HiTSOx approach results in  $\eta \approx 21.9\%$  with the main loss in  $V_{oc}$  ( $V_{oc} \approx 670 \text{ mV}$ ). As the implied opencircuit voltages  $iV_{oc}$  for the reference sequence and the HiTSOx approach are almost equal (fabricated in a different batch) with  $iV_{oc} = 682 \text{ mV}$  and  $iV_{oc} = 681 \text{ mV}$ , respectively, the recombination in the contact area with the dark saturation current density in the metallized area and the dark saturation current density in the laser-doped area may be the reason for the  $V_{\rm oc}$  loss. This needs to be further investigated.

We also determined the specific contact resistance  $\rho_c$  of the front contacts of the cells fabricated with the HiTSOx approach with selective emitter via TLM measurements. Table 3 shows the results for three

**Table 2:** Current-voltage characteristics of PERC solar cells fabricated by HiTSOx approach as well as for the reference group. The median and the best cell for each group are shown. The number of cells is shown in brackets. The measurements are performed by an industrial cell tester after boron-oxygen regeneration.

|                            | Process<br>sequence         | $j_{ m sc}$ / (mA/cm <sup>2</sup> )                                       | V <sub>oc</sub> /<br>mV       | FF /<br>%                                    | η /<br>%                                   |

|----------------------------|-----------------------------|---------------------------------------------------------------------------|-------------------------------|----------------------------------------------|--------------------------------------------|

| M<br>e<br>d<br>i<br>a<br>n | Ref<br>(4)<br>HiTSOx<br>(6) | $ \begin{array}{r} 40.3 \\ \pm \\ 0.1 \\ 40.2 \\ \pm \\ 0.1 \end{array} $ | $675 \pm 1 \\ 670 \pm 1 \\ 1$ | 81.6<br>$\pm$<br>0.1<br>81.1<br>$\pm$<br>0.1 | $22.2 \\ \pm \\ 0.1 \\ 21.9 \\ \pm \\ 0.1$ |

| B<br>e<br>s<br>t           | Ref                         | 40.3                                                                      | 675                           | 81.7                                         | 22.2                                       |

|                            | HiTSOx                      | 40.3                                                                      | 672                           | 81.1                                         | 22.0                                       |

**Table 3:** Specific contact resistances  $\rho_c$  for the HiTSOx approach with selective emitter obtained by transfer length method (TLM) measurements on alkaline textured and phosphorus-doped surfaces after contact firing with the respective set peak firing temperatures  $T_{\text{set,peak}}$  (SiO<sub>2</sub> and PECVD SiN<sub>x</sub> passivation layer).

| Set peak firing<br>temperature<br><i>T</i> <sub>set,peak</sub> / °C | Specific contact resistance $ ho_{c} / m\Omega cm^{2}$ |

|---------------------------------------------------------------------|--------------------------------------------------------|

| 820                                                                 | $0.63\pm0.45$                                          |

| 840                                                                 | $0.61\pm0.51$                                          |

| 860                                                                 | $0.57\pm0.50$                                          |

|                                                                     |                                                        |

different set peak firing temperatures  $T_{\text{set,peak}}$ . We reach low specific contact resistances around  $\rho_c \approx 0.6 \text{ m}\Omega\text{cm}^2$ , almost independent from  $T_{\text{set,peak}}$ . The  $\rho_c$  in our investigation is as low as for the reference process reported in Ref. [7], which also points out the successful implementation of the new HiTSOx approach.

As higher efficiencies are expected with selective emitter in comparison to homogeneous emitter, more investigations are necessary. Therefore, variations in diffusion, oxidation and laser processing need to be performed on cell level with the HiTSOx approach. However, this first cell experiment shows the promising potential of this high throughput application.

# 5 SUMMARY AND CONCLUSION

In this work, we fabricated PERC solar cells with two approaches for thermal oxidation enabling processing of more than 5,000 wafers by stacking the wafers which means up to 3.1 times higher throughput. The first one is the low temperature stack oxidation (LoTSOx) approach. Here, the commonly used low temperature thermal oxidation process is performed in a tube furnace while the wafer are horizontally stacked in the quartz boat. The median energy conversion efficiency is not influenced due to stacking of the wafers and reaches  $\eta = 22.2\%$  with homogeneous emitter, which is the same as for the reference group with vertically loaded wafers (one wafer per slot).

The second approach uses a shortened POCl<sub>3</sub> diffusion with only the deposition step and a subsequent high temperature stack oxidation. The shortened diffusion process enables an additional 1.8 times higher throughput Together with the increased throughput in the oxidation process, it reduces the cost of ownership by 41% compared to the state-of-the-art PERC processing. PERC solar cells with laser-doped selective emitter fabricated with the HiTSOx approach exhibit a peak energy conversion efficiency of  $\eta = 22.0\%$  and a median of  $\eta = 21.9\%$  which is already high in comparison to the reference sequence with homogeneous emitter and conventional moderate thermal oxidation. Further, the HiTSOx approach yields low specific contact resistances of the front contact around  $\rho_c \approx 0.6 \text{ m}\Omega \text{cm}^2$  independent from the set peak firing temperature.

A variation in the diffusion and stack oxidation processes for the HiTSOx approach allows a wide range of emitter sheet resistances  $R_{\rm sh}$  to be covered. Emitter dark saturation current densities as low as  $j_{0\rm e} = (12 \pm 2)$  fA/cm<sup>2</sup> are reached at  $R_{\rm sh} = (389 \pm 10) \Omega/{\rm sq}$ .

Promising results are reached with our approaches with highly increased throughputs. Further work will investigate the HiTSOx approach with a wide variation in the laser processing as well as homogeneous emitter formation to further improve high throughput solar cell processing.

### ACKNOWLEDGEMENTS

The authors would like to thank all colleagues at the Fraunhofer ISE PV-TEC. This work was funded by the German Federal Ministry for Economic Affairs and Energy within the research project "CUT-A PLUS" under contract number 0324282 and "GENESIS" under contract number 0324274C.

#### REFERENCES

- A. W. Blakers, A. Wang, A. M. Milne, J. Zhao, and M. A. Green, "22.8% efficient silicon solar cell," *Appl. Phys. Lett.*, vol. 55, no. 13, pp. 1363– 1365, 1989.

- [2] R. Preu, E. Lohmüller, S. Lohmüller, P. Saint-Cast, and J. M. Greulich, "Passivated emitter and rear cell—Devices, technology, and modeling," *Applied Physics Reviews*, vol. 7, no. 4, p. 41315, 2020.

- [3] ITRPV consortium, "International Technology Roadmap for Photovoltaic (ITRPV): Results 2021," 2021.

- [4] M. Meßmer, A. Wolf, M. Zimmer, F. Meyer, G. Hoppe, A. Lorenz, S. Tepner, D. Ourinson, G. Emanuel, S. Nold, B. Goraya, and F. Clement, "Increasing Throughput of Industrial PERC Production," *Photovoltaics International*, 2021, to be published.

- [5] M. Meßmer, S. Lohmüller, J. Weber, A. Piechulla, S. Nold, J. Horzel, and A. Wolf, "High Throughput Low Energy Industrial Emitter Diffusion and

Oxidation," in 37th EU PVSEC, online, 2020, pp. 370–377.

- [6] M. Meßmer, A. Wolf, S. Lohmüller, and J. Weber, "Industrial High Throughput Emitter Formation and Thermal Oxidation by the HiTSOx Approach," *Sol. RRL (Solar Rapid Research Letter)*, submitted 2021.

- [7] E. Lohmüller, J. M. Greulich, P. Saint-Cast, S. Lohmüller, S. Schmidt, U. Belledin, T. Fellmeth, S. Mack, G. Emanuel, K. Krieg, M. Zimmer, R. Kunert, F. Zobel, M. Linse, J. Horzel, M. Meßmer, A. Wolf, and R. Preu, "Front side optimization on boron- and gallium-doped Cz-Si PERC solar cells exceeding 22% conversion efficiency," in *37th EU PVSEC*, online, 2020.

- [8] L. Ventura, A. Slaoui, and J. C. Muller, "Realization of selective emitters by rapid thermal and laser assisted techniques," in *13th EU PVSEC*, Nice, 1995, pp. 1578–1581.

- [9] U. Jäger, M. Okanovic, M. Hörteis, A. Grohe, and R. Preu, "Selective emitter by laser doping from phosphosilicate glass," in 24th EU PVSEC, Hamburg, Germany, 2009, pp. 1740–1743.

- [10] A. Herguth and G. Hahn, "Boron-oxygen related defects in cz-silicon solar cells degradation, regeneration and beyond," in 24th EU PVSEC, Hamburg, Germany, 2009, pp. 974–976.

- [11] H. H. Berger, "Contact Resistance and Contact Resistivity," *J. Electrochem. Soc.*, vol. 119, no. 4, p. 507, 1972.

- [12] M. Spitz, U. Belledin, and S. Rein, "Fast inductive inline measurement of the emitter sheet resistance in industrial solar cell fabrication," in 22nd EU PVSEC, Milano, 2007, pp. 47–50.

- [13] A. Kimmerle, J. Greulich, and A. Wolf, "Carrierdiffusion corrected J0-analysis of charge carrier lifetime measurements for increased consistency," *Solar Energy Materials and Solar Cells*, vol. 142, pp. 116–122, 2015.