# TECHNISCHE UNIVERSITÄT DRESDEN

### Fakultät Elektrotechnik und Informationstechnik

### CHAIR OF MATERIALS SCIENCE AND NANOTECHNOLOGY

### DESIGN AND LAYOUT OF A TRANSIMPEDANCE AMPLIFIER (TIA) AT 50 GHZ FOR OPTICAL RECEIVERS IN IHP 130NM SIGE BICMOS TECHNOLOGY

October 31, 2022

Author: Mr.Lavakumar Navilipuri

Internal Supervisors: First Reviewer: PROF.DR.GIANAURELIO CUNIBERTI Second Reviewer: ASSOC.PROF.(PD) DR.HANS-GEORG BRAUN

> External Supervisor: MR.ANDY HEINIG, FRAUNHOFER IIS/EAS

Fakultät Elektrotechnik und Informationstechnik

#### Task Formulation for a Master Thesis

|                       | for Optical Receivers in IHP 130nm SiGe BiCMOS Technology       |

|-----------------------|-----------------------------------------------------------------|

| Subject:              | Design and Layout of a Transimpedance Amplifier (TIA) at 50 GHz |

| Studies:              | Nanoelectronic Systems                                          |

| Matriculation Number: | 4821932                                                         |

| Student´s Name:       | Lavakumar Navilipuri                                            |

#### **Objectives of work**

Optical fiber communication has emerged as a critical contributor to today's industrial development, economic progress, and modern society. Extending the bandwidth of analog frontend circuits for optical communications is critical to cope with the ever-increasing traffic. The transimpedance amplifier (TIA), acting as the electrical front-end of an optical receiver, is an essential block in optical communication systems.

In the Optical receiver, the photodetector converts incident light into a small photocurrent. The transimpedance amplifier (TIA) amplifies the current received from the photodiode to an adequate voltage level for the following stages. Front-end circuits for high-speed applications usually require the characteristics of low-noise and broad-bandwidth. With no exception, the TIA design entails many trade-offs between total input-referred noise, bandwidth, transimpedance gain, supply voltage, and power dissipation, presenting difficult challenges.

#### Focus of the work

This thesis focuses on the design and layout of a transimpedance amplifier (TIA) for optical receivers in IHP 130nm SiGe BiCMOS technology at a 50 GHz frequency range. The designed TIA should have a minimum transimpedance gain of 60 dBOhms, a minimum bandwidth of 40 GHz, and a maximum input-referred noise of  $20 pA/\sqrt{Hz}$ . To achieve this, the following sub-tasks have to be followed:

- Literature review of state-of-the-art transimpedance amplifier (TIA) architectures.

- Comparison of different architectures will be used to decide on a certain topology.

- Designing the schematic in IHP 130nm SiGe BiCMOS technology.

- Designing the layout in IHP 130nm SiGe BiCMOS technology.

- The pre and post-layout results will be compared with one another alongside the theoretical considerations where ever possible.

- The performance will be measured against the state-of-the-art architectures.

Master thesis will be written in English.

Advisor: 1st Reviewer: 2<sup>nd</sup> Reviewer: Mr. Andy Heinig Prof. Dr. Gianaurelio Cuniberti Assoc. Prof. (PD) Dr. Hans-Georg Braun

Start: 23.05.2022

Thesis due: 31.10.2022

Prof. Dr.-Ing. T. Mikolajick Chairman of Examination Board

Prof. Dr. Gianaurello Curitberticuration of Materials unibertianaurelio Cunibani Responsible Professoren University of Technology D-01062 Dresden, Germany

# Statement Of Authorship

I, Lavakumar Navilipuri, born on Nov 17th, 1994 in Telangana, India, hereby affirm that I have completed this thesis work on the subject of "Design and Layout of a Transimpedance Amplifier (TIA) at 50 GHz for Optical Receivers in IHP 130nm SiGe BiCMOS Technology" without the unauthorized help of third parties. The thesis work was done in collaboration between Fraunhofer IIS, Institutsteil EAS, Dresden and Technische Universität, Dresden. Thoughts taken directly or indirectly from external sources are marked as such. In selecting and evaluating the material and in preparing the manuscript, I received support from the following persons:

Mr. Andy Heinig, Fraunhofer IIS, Institutsteil EAS. Assoc.Prof.(PD) Dr.Hans-Georg Braun, Technische Universität Dresden.

Additional persons were not involved in the intellectual preparation of the presented thesis work. I am aware that non-compliance with this declaration can lead to the subsequent withdrawal of the thesis.

Lavakumar Navilipuri. Dresden, October 31, 2022.

# Acknowledgement

I would like to start by thanking my supervisor Mr. Andy Heinig from Fraunhofer IIS, Institutsteil EAS, for the constant support right from the selection process until the successful completion of my thesis. I am grateful for all the inputs, suggestions, guidance, and support offered by my supervisor and the whole efficient electronics team at Fraunhofer IIS, Institutsteil EAS.

I want to thank my supervisors Prof. Dr. Gianaurelio Cuniberti and Assoc. Prof.(PD) Dr. Hans-Georg Braun from TU Dresden. I am forever indebted to their support and guidance throughout the thesis work.

Last but not least, I would like to thank my family and friends for being the strongest pillars of my strength always and forever. Lastly, I would like to extend my thanks to everyone who helped me throughout this journey.

# Abstract

Today's technology allows for a quick and efficient transmission of enormous amounts of data. Optical fibres are currently the most effective way to transmit enormous amounts of data. A photodiode (PD) generates current from the optical fibre's light to receive the data transmitted. However, this current is very small. It is necessary to use an amplifier that, in addition to amplifying the photodiode current, also converts it into a voltage for the optical receiver's subsequent phases. These amplifiers also referred to as transimpedance amplifiers, are an essential component of optical receivers because they must have a high gain to amplify the photodiode current and a large bandwidth to pick up high data rate signals.

This thesis thoroughly analyses these amplifiers, outlining the advantages and disadvantages of various topologies. This thesis uses mathematical equations to describe the operation of the Transimpedance Amplifier (TIA) and to identify the optimal range between the gain, the bandwidth, and the noise (input-referred noise) to produce the amplifier with the desired characteristics. Electrical simulations were used to test all the theoretical assertions and the entire system's behaviour for the four topologies of the common base, common emitter, regulated cascode, and darlington pair.

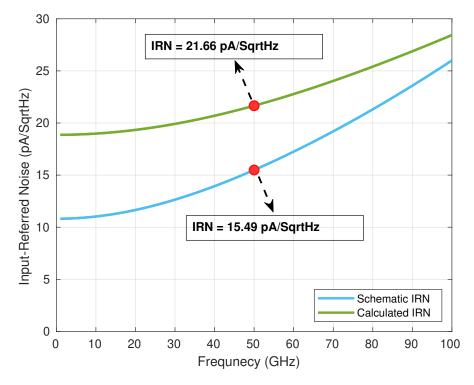

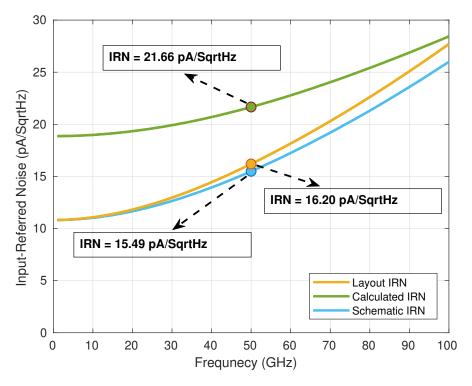

The minimum transimpedance gain target for the TIA is 60 dB $\Omega$  with a minimum bandwidth of 40 GHz. The designed TIA should have an input-referred noise of less than 20 pA/ $\sqrt{\text{Hz}}$ . After thoroughly examining these four topologies, a layout is designed for darlington pair TIA with resistive feedback. The implemented TIA has achieved a transimpedance gain of 63.74 dB $\Omega$  with a broad bandwidth of 60.84 GHz. The designed TIA has achieved a low input-referred noise of 16.20 pA/ $\sqrt{\text{Hz}}$ . The designed TIA has a chip size of just 0.0064 mm<sup>2</sup> and uses 30.53 mW of DC power.

# List of Figures

| 1.1  | Cisco forecast for global device and connection growth (2018-2023) [1].  | 12       |

|------|--------------------------------------------------------------------------|----------|

| 1.2  | Historical increase in the $B \cdot L$ product with new technologies [3] | 13       |

| 1.3  | Basic blocks of Fibre Optic Communication System                         | 14       |

| 1.4  | Front-end diagram of a typical optical Transmitter                       | 16       |

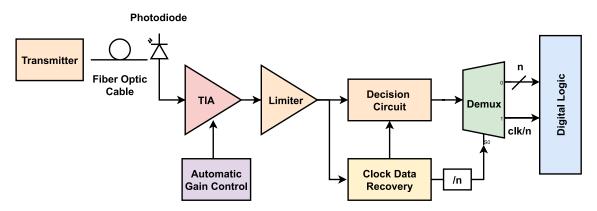

| 1.5  | Front-end diagram of a typical optical receiver                          | 16       |

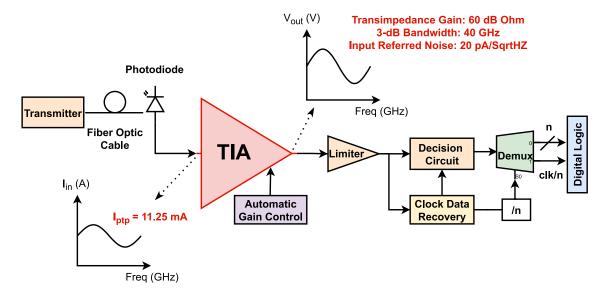

| 1.6  | Required specifications for TIA design.                                  | 18       |

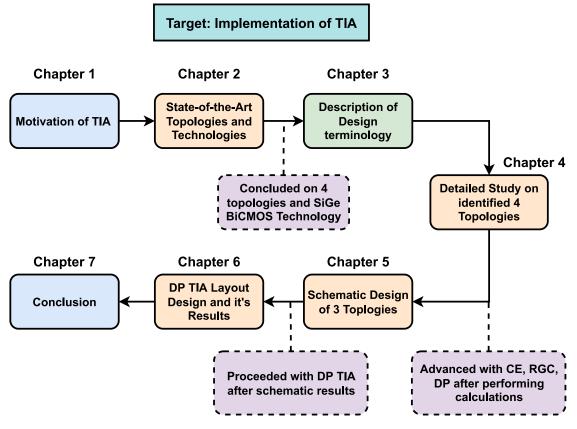

| 1.7  | Thesis Structure                                                         | 19       |

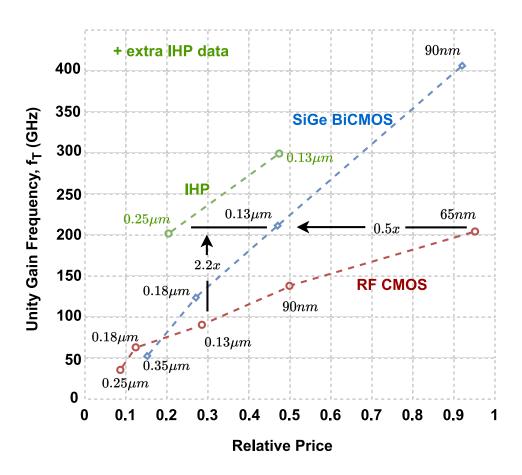

| 2.1  | Comparison between BiCMOS and CMOS technologies with respect             |          |

|      | to RF performance vs cost $[31]$                                         | 24       |

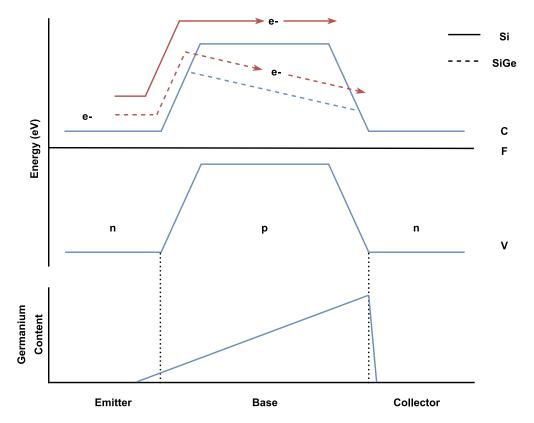

| 2.2  | Ge concentration (bottom) and band structure (top) of a SiGe het-        |          |

|      | erojunction bipolar transistor                                           | 25       |

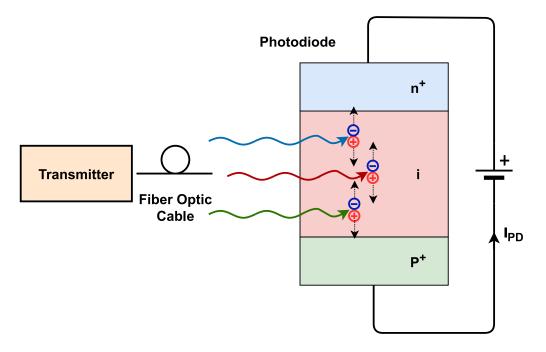

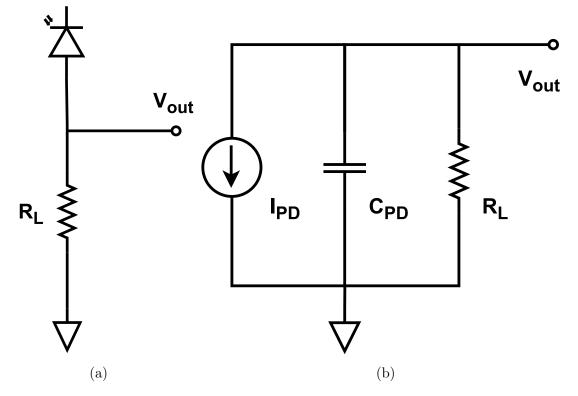

| 3.1  | PIN Photodiode.                                                          | 27       |

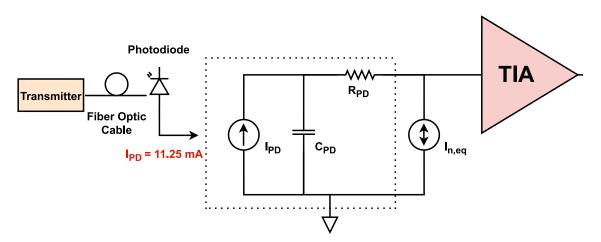

| 3.2  | Basic receiver front-end model [15] showing the input impedance and      |          |

|      | noise component $I_{n,eq}$ added to the TIA by PD. Dotted box is a small |          |

|      | signal equivalent circuit of a photodiode.                               | 27       |

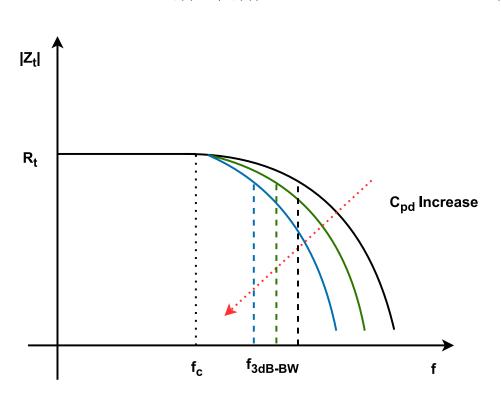

| 3.3  | Frequency Response of a TIA with changing Photo-Diode Capacitance.       | 29       |

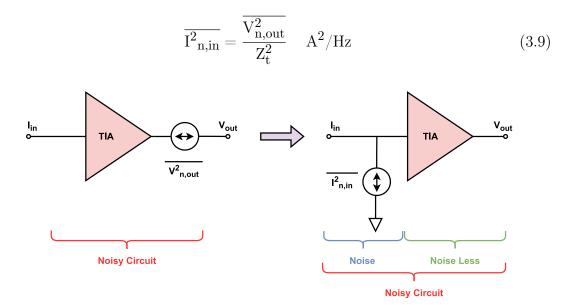

| 3.4  | Input Referred Noise Current                                             | 32       |

| 4.1  | (a). Circuit diagram of a single resistor TIA. (b). Equivalent small-    | ~ ~      |

| 1.0  | signal model.                                                            | 35       |

| 4.2  | Circuit diagram of a basic common base TIA.                              | 36       |

| 4.3  | Equivalent small signal model of a Common base TIA.                      | 37       |

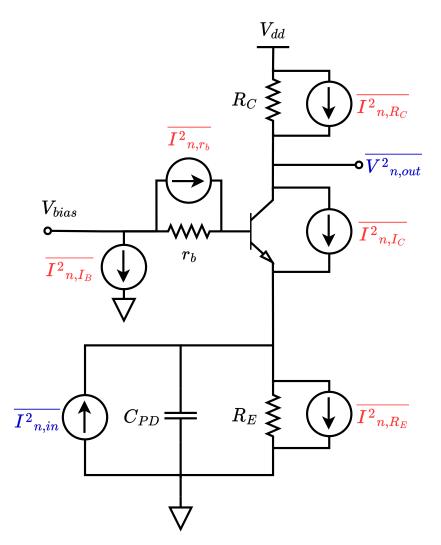

| 4.4  | CB TIA with individual noise sources (in red)                            | 38       |

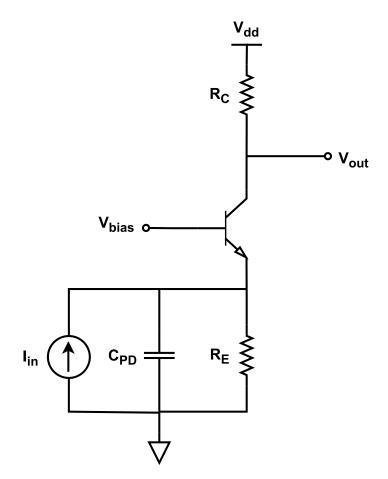

| 4.5  | Circuit diagram of a basic common emitter TIA.                           | 40       |

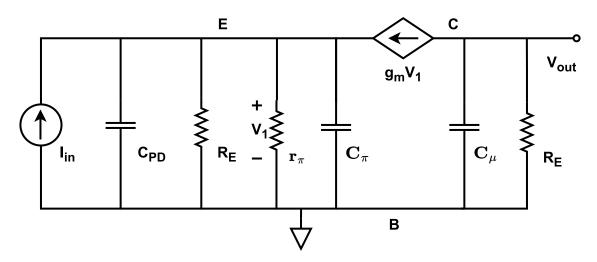

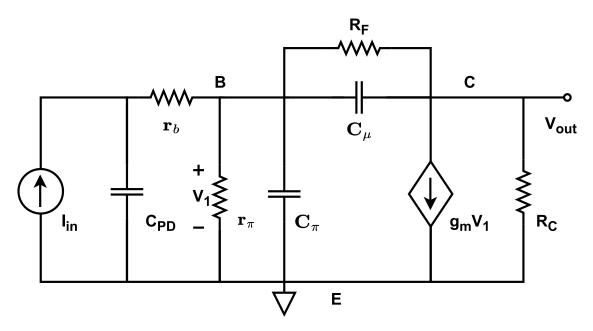

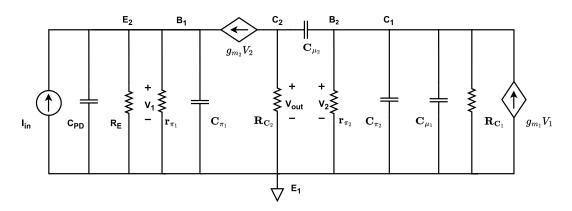

| 4.6  | Equivalent small signal model of a Common emitter TIA                    | 41       |

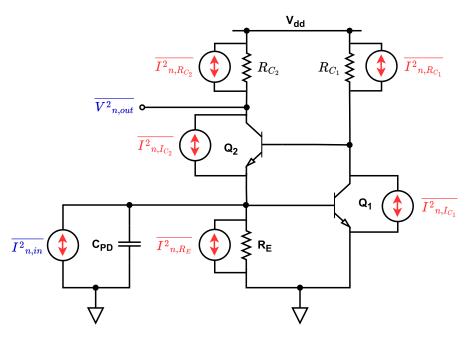

| 4.7  | CE TIA with individual noise sources (in red)                            | 42       |

| 4.8  | Circuit diagram of a basic regulated cascode TIA.                        | 43       |

| 4.9  | Equivalent small signal model of a regulated cascode TIA                 | 44       |

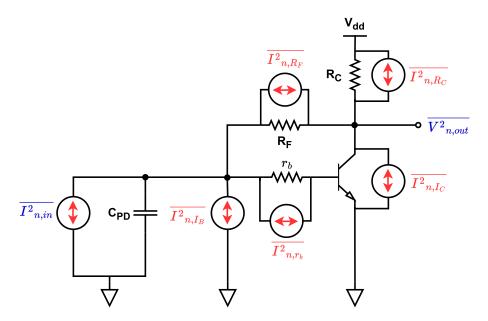

| 4.10 | RGC TIA with individual noise sources (in red)                           | 45       |

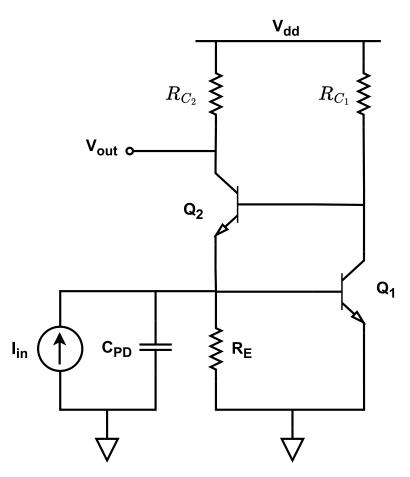

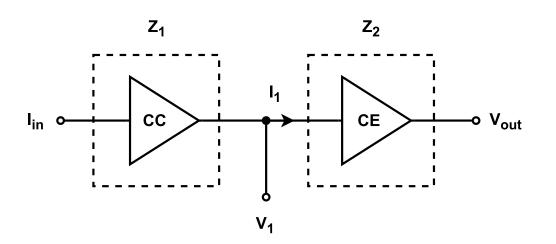

| 4.11 |                                                                          | 17       |

| 1 19 |                                                                          | 47<br>49 |

| 4.12 | Darlington TIA with individual noise sources (in red)                    |          |

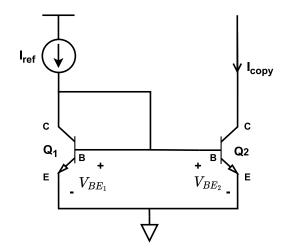

| 5.1  | Current mirror circuit for DC bias.                                      | 53       |

| 5.2  | Schematic diagram of a Common Emitter with Negative Resistive            | <u> </u> |

| -    | Feedback TIA                                                             | 54       |

| 5.3  | Transimpedance gain and bandwidth results of the CE TIA                  | 55       |

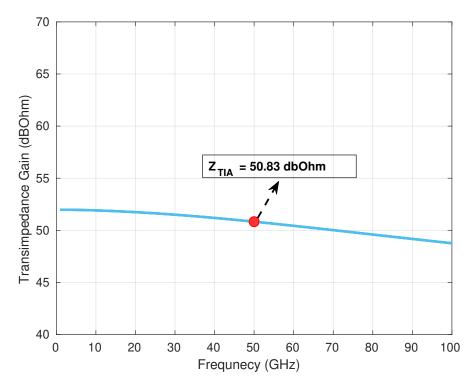

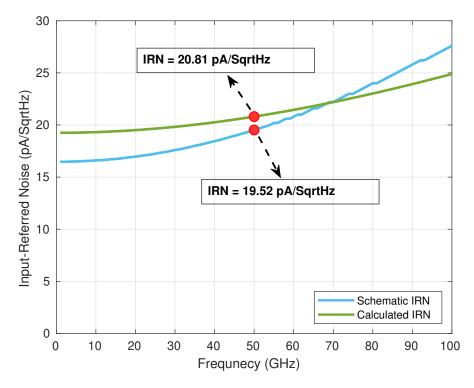

| $5.4 \\ 5.5$                              | Input-Referred Noise of CE TIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\frac{56}{57}$ |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| $\begin{array}{c} 5.5 \\ 5.6 \end{array}$ | Transimpedance gain and bandwidth results of the Regulated Cas-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |

| 5.7                                       | code TIA.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | $\frac{58}{59}$ |

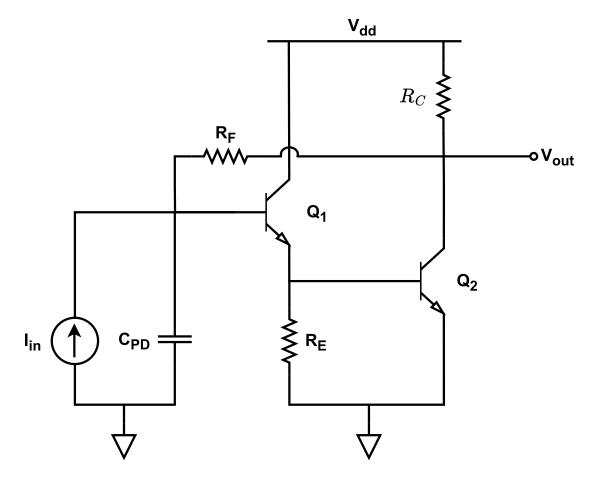

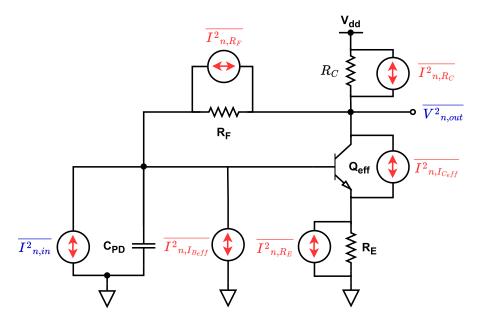

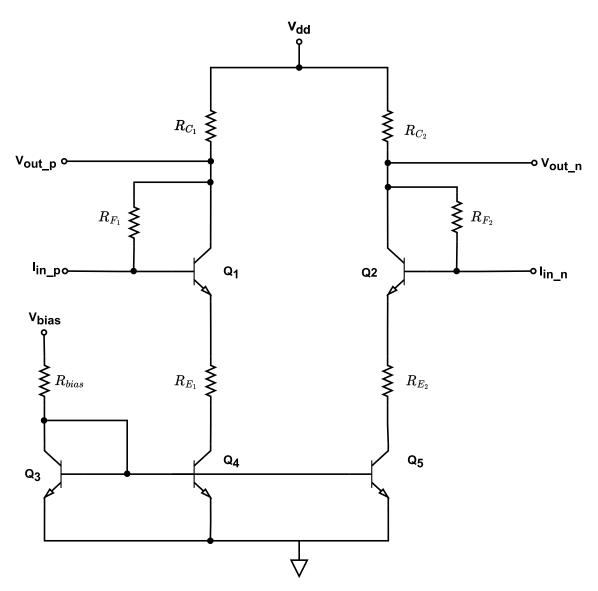

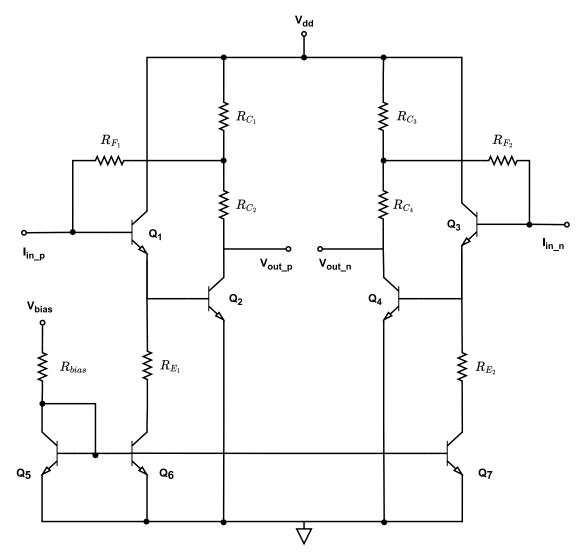

| 5.8                                       | Schematic diagram of a Darlington pair with Negative Resistive Feedback TIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60              |

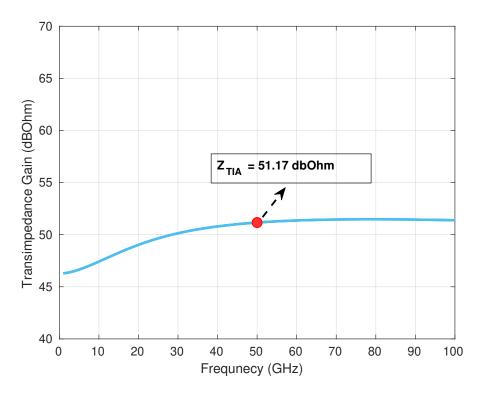

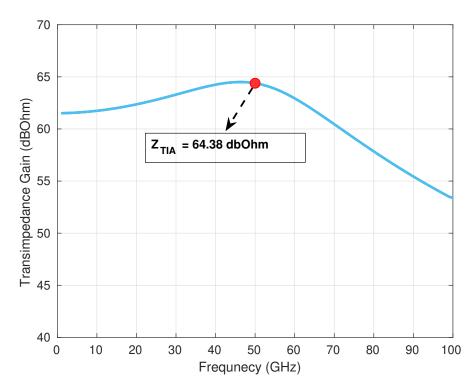

| 5.9                                       | Transimpedance gain and bandwidth results of the Darlington Pair TIA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 61              |

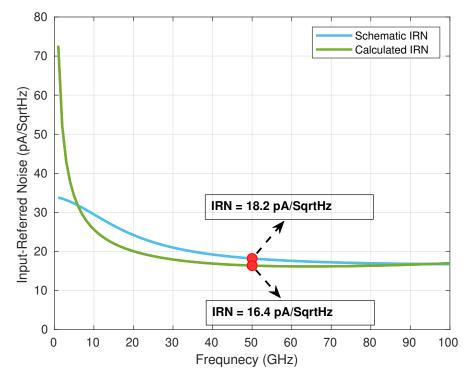

| 5.10                                      | Input-Referred Noise of Darlington Pair TIA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62              |

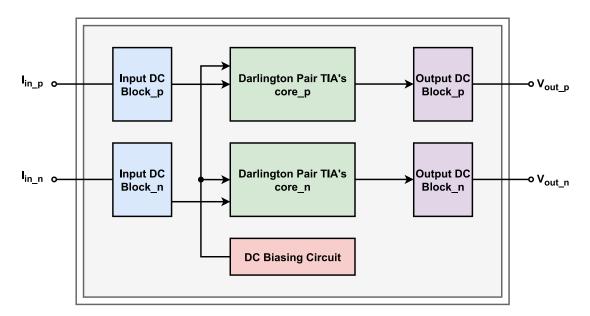

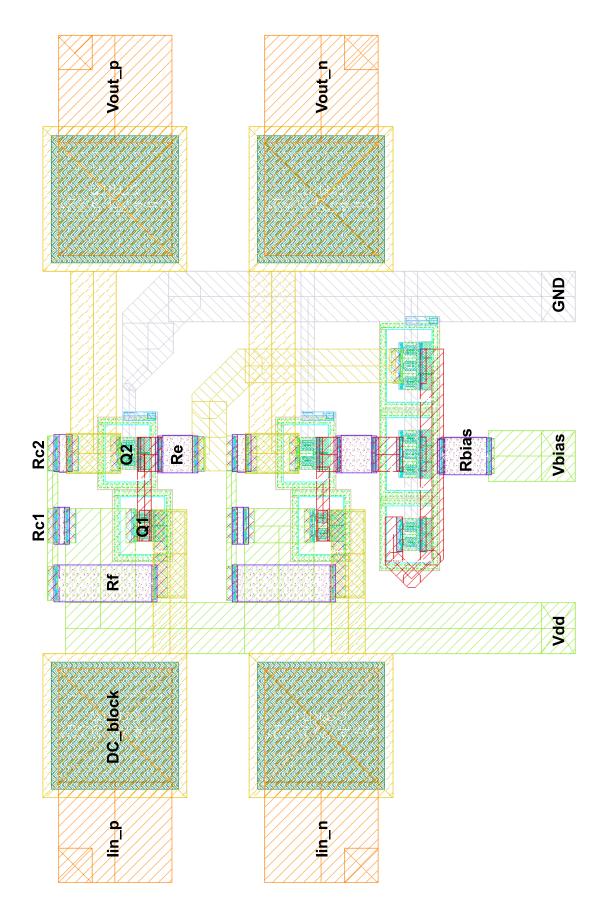

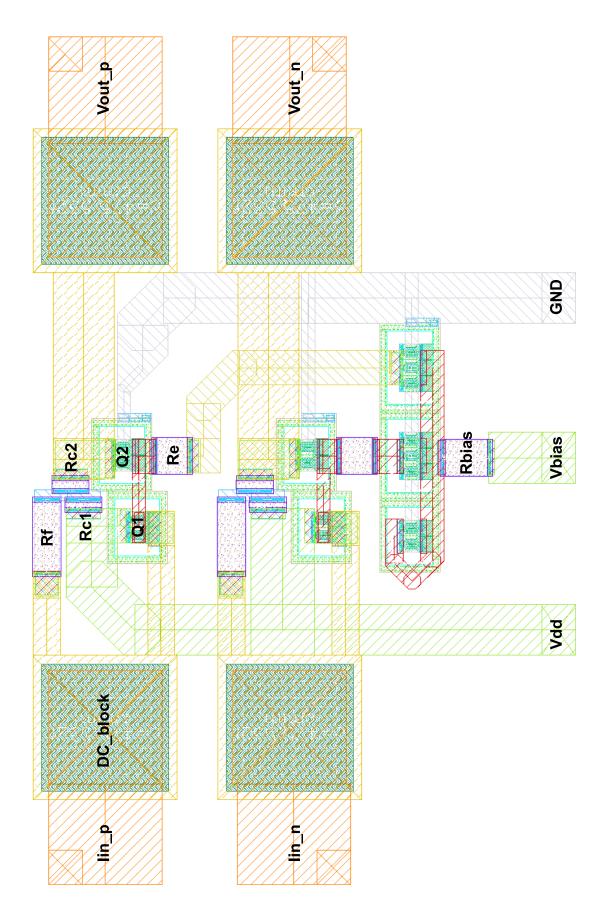

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Floor planning diagram for the darlington pair TIAs layout Initial layout of the designed darlington pair TIA with resistive feed-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64              |

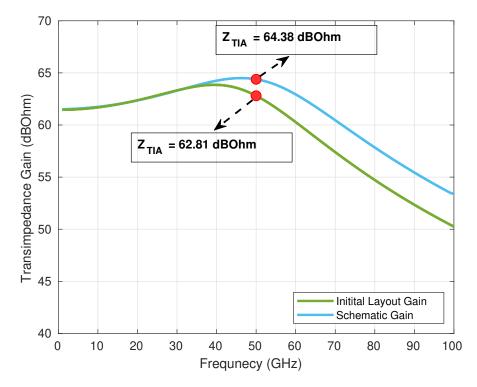

| 6.3                                       | back                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66              |

|                                           | tial layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68              |

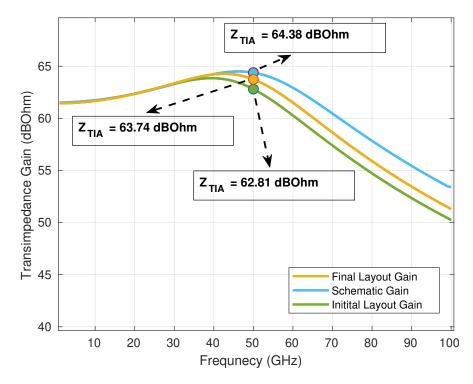

| $\begin{array}{c} 6.4 \\ 6.5 \end{array}$ | Final layout of the designed darlington pair TIA with resistive feedback.<br>Transimpedance gain and bandwidth results of the initial layout vs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70              |

| 6.6                                       | final layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 71<br>71        |

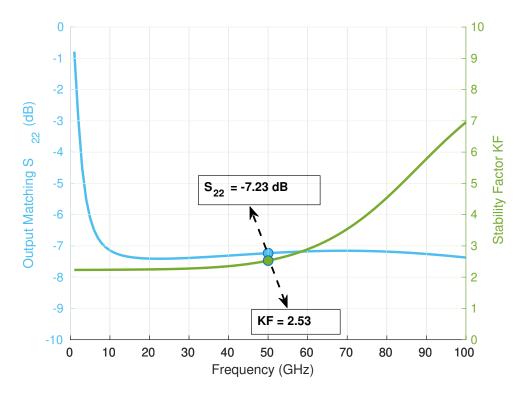

| 6.7                                       | Output impedance $(S_{22})$ and stability factor (KF) of the final TIAs layout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72              |

| 6.8                                       | Process corner setup for designed TIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73              |

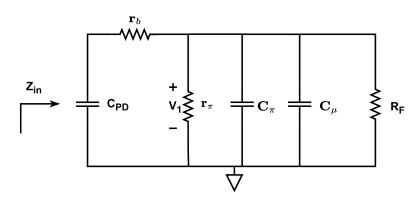

| A.1                                       | Equivalent small signal model of a common emitter TIA while finding input impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82              |

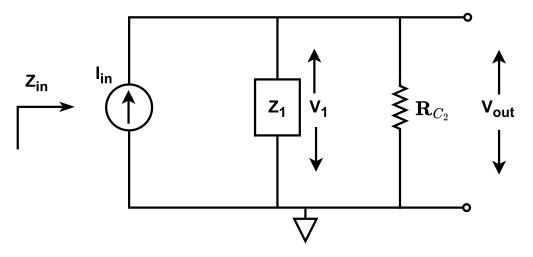

| A.2                                       | Equivalent small signal model of a common emitter TIA while finding output impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83              |

| A.3                                       | Equivalent small signal model of a regulated cascode TIA while find-<br>ing input impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 84              |

| A.4                                       | Equivalent small signal model of a regulated cascode TIA while find-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -               |

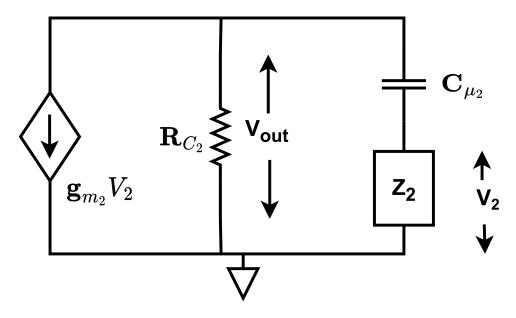

| A.5                                       | ing output impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 86              |

|                                           | common emitter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87              |

# List of Tables

| 2.1 | Comparison of State-of-the-Art TIA Circuits                              | 22 |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | Peak transit frequencies for different high-speed SiGe HBT technologies. | 25 |

| 4.1 | Comparison of performance parameters for different TIA topologies        | 50 |

| 5.1 | Final values of components in CE TIA with negative resistive Feedback.   | 55 |

| 5.2 | Final values of components in RGC TIA                                    | 57 |

| 5.3 | Final values of components in DP TIA with negative resistive Feedback.   | 60 |

| 5.4 | Comparison of results obtained from different schematic designs $\ldots$ | 62 |

| 6.1 | Thickness of different metal layers available for routing                | 65 |

| 6.2 | Comparison of area consumed by different components on the chip          | 69 |

| 6.3 | Maximum and minimum values of all performances parameters                | 74 |

| 6.4 | Comparison of results obtained from calculations, schematic design       |    |

|     | and layout design                                                        | 74 |

| 7.1 | Comparison of State-of-the-Art TIA Circuits with this work               | 76 |

# Abbreviations

| ARPAnet         | Advanced Research Projects Agency Network                   |

|-----------------|-------------------------------------------------------------|

| BiCMOS          | Bipolar Complementary Metal-Oxide-Semiconductor             |

| BCS, TYP, & WCS | Best-Case Scenario, Typical Scenario, & Worst-case Scenario |

| CB              | Common Base                                                 |

| CE              | Common Emitter                                              |

| CC              | Common Collector                                            |

| CAGR            | Compound Annual Growth Rate                                 |

| CERN            | European Council for Nuclear Research                       |

| DP              | Darlington Pair                                             |

| DRC             | Design Rules Check                                          |

| GHz & THz       | Giga-Hertz & Tera-Hertz                                     |

| Gbps & Tbps     | Gigabit per second & Terabit per second                     |

| HBT             | Heterojunction Bipolar Transistor                           |

| IRN             | Input-Referred Noise                                        |

| LED             | Light-Emitting Diodes                                       |

| LVS             | Layout vs Schematic Check                                   |

| M2M             | Machine to Machine                                          |

| MUX & DMUX      | Multiplexer & Demultiplexer                                 |

| PD              | Photo-Diode                                                 |

| PEX             | Parasitic Extraction                                        |

| RGC             | Regulated Cascode                                           |

| RMS             | Root Mean Square                                            |

| SNR             | Signal-to-Noise Ratio                                       |

| TIA             | Transimpedance Amplifier                                    |

| TCP IP          | Transmission Control Protocol Internet Protocol             |

| Tx & Rx         | Transmitter & Receiver                                      |

# Symbols

| $V_{th}$                          | Threshold voltage                        |

|-----------------------------------|------------------------------------------|

| nm                                | Nanometer                                |

| $\mathrm{dB/km}$                  | Decibel per kilometer                    |

| $V_{p-p}$                         | Peak-to-Peak Voltage                     |

| $\mu A$                           | Micro Ampere                             |

| $\mathrm{dB}\omega$               | Decibel Ohm                              |

| $\mathrm{pA}/\sqrt{\mathrm{Hz}}$  | pico Ampere per Square-root Hertz        |

| $\mathrm{C}_{\mathrm{PD}}$        | Photodiode Parasitic Capacitance         |

| $I_{PD}$                          | Photodiode Current                       |

| $\mathrm{fF}$                     | femto Farad                              |

| $I_{in}$                          | Input Current                            |

| Vout                              | Output Voltage                           |

| $\mathbf{Z}_{\mathrm{TIA}}$       | Transimpedance Gain                      |

| $\mathbf{f}_{\mathbf{c}}$         | Corner Frequency                         |

| $\mathrm{K}_\mathrm{F}$           | Rollet Stability factor                  |

| $\mathrm{S}_{11},\mathrm{S}_{22}$ | Input and Output Reflection Coefficients |

| $\mathrm{S}_{12},\mathrm{S}_{21}$ | Reverse and Forward voltage gains        |

| $C_{T}$                           | Total Capacitance                        |

| V <sub>n,out</sub>                | Noise Voltage                            |

| $I_{n,in}$                        | Input-referred Noise Current             |

| $\mathbf{R}_{\mathbf{C}}$         | Collector Resistance                     |

| $I_{\rm C}$                       | Collector Current                        |

| $g_{\rm m}$                       | Transconductance                         |

| $\mathrm{p}_n, \mathrm{z}_n$      | Poles and Zeros                          |

| $\mathrm{R}_{\mathrm{L}}$         | Feedback Resistor                        |

| $\mathrm{R}_{\mathrm{E}}$         | Emitter Resistance                       |

| $V_{CE}$                          | Emitter Voltage                          |

# Contents

| $\mathbf{St}$ | atem                                    | nent of Authorship                                                                                                                                                                             | <b>2</b>                                      |

|---------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Ac            | cknov                                   | wledgement                                                                                                                                                                                     | 3                                             |

| Al            | ostra                                   | let                                                                                                                                                                                            | 4                                             |

| $\mathbf{Li}$ | st of                                   | Figures                                                                                                                                                                                        | 6                                             |

| $\mathbf{Li}$ | st of                                   | Tables                                                                                                                                                                                         | 7                                             |

| Al            | obre                                    | viations                                                                                                                                                                                       | 8                                             |

| Sy            | mbo                                     | ols                                                                                                                                                                                            | 9                                             |

| 1             | <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4 | FoductionFibre Optical CommunicationOptical Transceivers Overview1.2.1Optical Transmitters1.2.2Optical ReceiversGoal and Approach of this ThesisThesis Structure                               | <b>12</b><br>13<br>15<br>15<br>16<br>17<br>18 |

| 2             | Lite<br>2.1<br>2.2                      | erature Review<br>State-Of-The-Art                                                                                                                                                             | <b>20</b><br>20<br>23                         |

| 3             | <b>Des</b><br>3.1<br>3.2                | ign ConsiderationsPhotodetectorsPerformance of TIAs3.2.1Transimpedance Gain3.2.2Bandwidth3.2.3Noise Sources3.2.4Input-Referred Noise (IRN) Current3.2.5Impedance Matching3.2.6Stability Factor |                                               |

| 4             | <b>Tra</b><br>4.1<br>4.2<br>4.3         | nsimpedance Amplifier Topologies         Introduction                                                                                                                                          | <b>34</b><br>34<br>36<br>39                   |

|    | $4.4 \\ 4.5 \\ 4.6$                           | Regulated Cascode TIA                                                                                                                                  | 42<br>46<br>49                         |

|----|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 5  | 5.1                                           | nsimpedance Amplifier Schematic Design<br>Common Emitter with Negative Resistive Feedback TIA                                                          | <b>51</b><br>53                        |

|    | $5.2 \\ 5.3 \\ 5.4$                           | Regulated Cascode TIA                                                                                                                                  | 56<br>59<br>62                         |

| 6  | Tra                                           | nsimpedance Amplifier Layout Design                                                                                                                    | 63                                     |

|    | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | Initial Layout                                                                                                                                         | 65<br>65<br>67<br>68<br>68<br>69<br>74 |

| 7  | Con                                           | clusion                                                                                                                                                | <b>75</b>                              |

|    | 7.1                                           | Future Scope                                                                                                                                           | 77                                     |

| Bi | bliog                                         | raphy                                                                                                                                                  | 81                                     |

| Α  | Mat<br>A.1<br>A.2<br>A.3                      | <b>hematical Analysis</b> Common Emitter TIA With Resistive Feedback         Regulated Cascode TIA         Darlington Pair TIA With Resistive Feedback | 84                                     |

# Chapter 1 Introduction

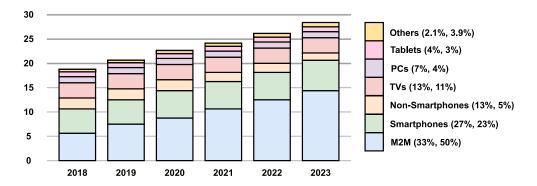

The modern internet is powered by the TCP/IP protocol, which was shifted from ARPAnet (the internet's predecessor) in January 1983, enabling various types of computers on different networks to communicate. The sudden popularity of the World Wide Web and the dot-com bubble in the late 1990s caused a global leap in information access and diffusion, both in the commercial and domestic sectors, resulting in the information age and an economy based on information technology. Enterprises in various domains have begun to explore the possibilities of capitalizing on this new paradigm and can now communicate easily with their employees, customers, and associates, leading to a rise in the number of users and the diversification of connected devices (PCs, tablets, TVs, smartphones). This increase in global internet traffic is explained in the Cisco Annual Internet Report (2018-2023) [1]. Figure 1.1 forecasts a rise of 10% Compound Annual Growth Rate (CAGR) for devices and connections from 2018 to 2023. Every year, plenty of new devices with enhanced capabilities and intelligence are introduced and adopted in the market. A growing number of Machine to Machine (M2M) applications, such as smart meters, video surveillance, healthcare monitoring, transportation, and package tracking, contribute significantly to the growth of devices and connections. This scenario necessitates one thing to provide a satisfactory user experience: higher data transfer rates. The global internet system's data rate must be increased from tens of Gbps to Tbps. This means that bandwidth requirements will increase by more than a factor of 100. Such data rates necessitate using low-loss, high-bandwidth media [2]. Out of all the available communication mediums in the market, optical fibres have the best data transfer performance.

Figure 1.1: Cisco forecast for global device and connection growth (2018-2023) [1].

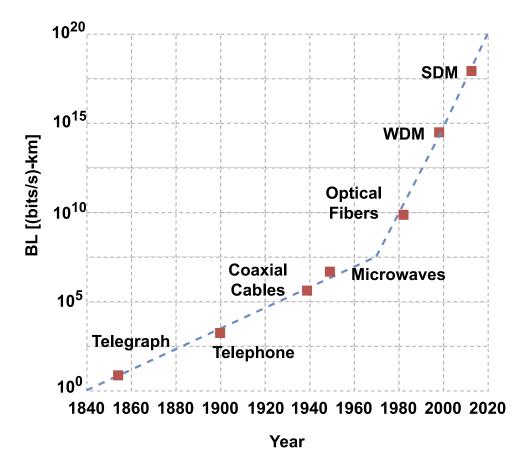

Figure 1.2: Historical increase in the B·L product with new technologies [3].

Optical fibre communication technologies are the driving force behind this expansion. Figure 1.2 depicts how the product of bit rate and signal repeating distance (B.L product) has increased by a factor of  $10^{18}$  as new technologies have emerged [3]. The change in slope that occurred around 1980, when optical fibres were first introduced, is evident. Optical fibre cable is lighter and thinner than electrical wiring, has higher bandwidth, lower loss, and is resistant to electromagnetic interference and crosstalk. With less than 0.2 dB/km attenuation around the emission wavelength of 1550 nm, it allows for data transmission up to terabits per second over thousands of kilometres [4].

# 1.1 Fibre Optical Communication

With the advent of multimedia technologies mentioned above, the communications sector has increasingly emphasised high-speed data transfer. There are several hurdles to high-speed electronic data communications, including low bandwidth of metallic mediums, cross-talk generated by magnetic induction, and susceptibility to static and Radio Frequency (RF) interference. Data transfer with glass and plastic Fibre optic cables is an alternative to traditional metallic or coaxial cable facilities. Fibre optics provide a high bandwidth medium with none of the limitations associated with electronic data transfer [5]. GTE (General Telephone and Electronics) and AT&T (American Telephone & Telegraph) introduced the first Fibre optic telephone system in 1977. Since then, the rising volume and speed of data transmission

across optical Fibres have transformed how people communicate and conduct business [6]. Optical-Fibre cables now carry more than 80% of the world's long-distance voice and data traffic.

In July 2021, researchers broke the internet transmission speed record [7]. World is One News, WION, reported [8]:

National Institute of Information and Communications Technology (NICT) researchers from Japan have broken a world record for the fastest internet speed, measuring 319 Terabytes per second for a 3,001-kilometer long-distance data transfer. The previous record was set by University College London researchers, who obtained 178 Terabytes per second. The attained 319 Terabytes per second speed is a high-speed internet connection. According to the researchers, the technology can be used to upgrade existing data transmission models and enable the speeds claimed by 5G, which is not yet accessible everywhere.

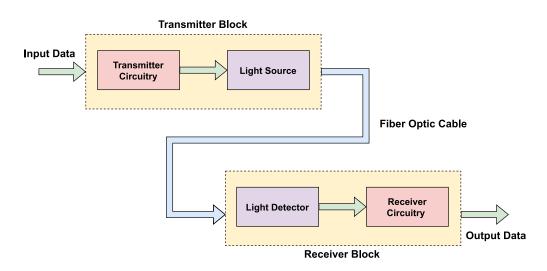

The primary goal of an optical communication network is to transmit light pulses from a transmitter to a receiver via an optical Fibre. As illustrated in Figure 1.3, a basic optical communication system consists of three major components: a transmitter block, an optical Fibre, and a receiver block [9].

- The transmitter generates the optical signal by converting the electrical signal to optical information through light pulses. The transmitter comprises an optical emitter and the current drive circuitry that goes with it. The most common optical emitters are light-emitting diodes (LEDs) and laser diodes.

- Optical Fibre delivers optical data over long distances.

- The light pulses received from the optical Fibre are converted back to electrical current pulses by the receiver. The receiver mainly comprises an optical detector and the corresponding amplification circuitry. The receiver employs a photodiode (PD) as an optical detector to convert incoming light pulses to current.

Figure 1.3: Basic blocks of Fibre Optic Communication System

# 1.2 Optical Transceivers Overview

Like any other communication system, a Fibre-optic transceiver consists of a transmitter, a transport medium, and a receiver. The foundational block diagram of an optical transceiver is shown in Figure 1.3. Because the transmission medium is an optical Fibre rather than a copper wire (used in wired communications), the digital signal should switch from electrical to optical and vice-versa. Optical transmitters (Tx) and receivers (Rx) are required to perform this task. An optical transmitter transforms an electrical analogue or digital signal into an optical signal. Data is serialized in the optical transmitter before being transmitted through the optical channel to achieve high-speed data rates with a small number of channels. A lightemitting diode or a solid-state laser diode can generate the optical signal. Optical transmitters' most common operational wavelengths are 850, 1300, or 1550 nm. One or more glass Fibres act as optical signal waveguides in the Fibre optic cable. Depending on the absorbed light intensity, the optical receiver turns the optical signal back into a replica of the original electrical signal. The optical signal detector is either a PIN-type photodiode or an avalanche-type photodiode. LEDs and PDs are often employed on separate modules due to integration issues with the back-end circuitry of the transmitter and receiver sides. The receiver is the most complex of the three components of an optical communications system to design. Even though an optical receiver comprises several functional blocks, our focus in this study is on the receiver's front-end design, which includes the TIA.

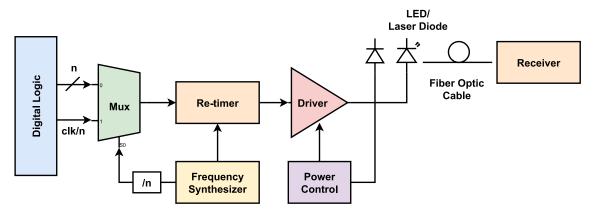

# 1.2.1 Optical Transmitters

The block diagram of a typical optical transmitter is shown in Figure 1.4. The multiplexer (MUX) on the transmitter side combines the N-bit parallel data from the digital logic component at a lower data rate into a serial data stream operating at a higher data rate. The parallel data is picked using MUX and retimed using a re-timer circuit and a bit-rate clock generated by a frequency synthesizer. This serial data is amplified to the precise swing required to drive an optical modulator with a high enough extinction ratio. The extinction ratio is the ratio of logical "1" optical power to logical "0" optical power that determines the optical link's maximum signal-to-noise ratio (SNR). An envelope similar to electrical serial data is used to modulate the optical carrier. A laser driver or modulator driver uses this high-speed serial data stream to control the associated optoelectronic device (typically a laser diode). The laser driver modulates the current of a laser diode (LD), and the power control circuit adjusts the laser's light intensity [10] [11].

For a better understanding, consider the Optical Carrier 768 (OC-768) transport system. A 16:1 multiplexer (MUX) in an OC-768 optical transport system combines sixteen parallel 2.5 Gb/s electrical signals to a 40 Gb/s serial data, which is retimed by a frequency/clock synthesizer. The data rate of the OC-768 system is 40 Gb/s, while the IEEE 802.3ba Ethernet standard operates at around 40 Gb/s, which combines four parallel 10 Gb/s signals to a 40 Gb/s serial data [12] [13]. The laser diode's light signal stream is attached to optical Fibres for transmission. Before the light signal reaches the electrical receiver, it is usually amplified by an expensive Erbium-Doped Fibre-optical Amplifier (EDFA) to account for transmission loss in long-distance optical transmission systems. The optical wavelength typically employed for such long-distance transmission is 1550 nm, which has low attenuation and good efficiency for EDFA. However, EDFA is absent in cost-sensitive shortreach optical communication systems, and low-cost 850 nm optoelectronic devices are extensively used.

Figure 1.4: Front-end diagram of a typical optical Transmitter

Figure 1.5: Front-end diagram of a typical optical receiver

### 1.2.2 Optical Receivers

The envelope information received at the optical Fibre's output end should be demodulated back into the original electrical signal and then to digital values by the receiver. Figure 1.5 depicts a typical optical receiver system block diagram. The optical signal attenuates as it travels from one end to the other due to long or lowquality optical Fibre, and a large portion of the optical power is lost. As a result, auxiliary building blocks must be provided before transforming the signal into digital logic to improve performance [14].

In a typical optical receiver, A photodetector or photodiode (PD) converts the incoming optical signal to a small output current proportionate to the input optical power based on the diode responsivity. The ratio of output current produced for a given input power is defined as responsivity. The responsivity of many photodiodes ranges between 0.8 A/W and 1 A/W.

As the first building block after the photodiode, the transimpedance amplifier (TIA) amplifies electrical current with adequate bandwidth, transforming it to volt-

age with as little noise as possible. The transimpedance amplifier should have lownoise and wide-band capabilities to amplify the small current to voltage with a high signal-to-noise ratio (SNR) and with the least amount of intersymbol interference (ISI) [15]. As a result, TIA is, without a doubt, the most significant building block of the optical receiver. This block's design requires numerous noise, bandwidth, gain, and stability trade-offs. The TIA is distinguished by its specification of a low input impedance necessary to absorb current from the photodiode. It should also have a large transimpedance, determined by converting the input current to an output voltage. In most cases, a single TIA stage is insufficient to amplify the input current to detectable logic levels (approximately 500 mVp-p).

Depending on the complexity of the modulation system, the TIA is frequently followed by either a limiting amplifier or a linear amplifier. The voltage signal from the TIA's output is enhanced further by a limiting amplifier (LA) and/or an automatic gain control (AGC) amplifier. The limiting amplifier and automatic gain control amplifier are collectively known as post amplifiers. For the signal to be delivered to the clock and data recovery (CDR) circuit, a limiting amplifier should have a high gain and a large output voltage swing [16]. The TIA and limiting amplifier make up what is generally called the analogue front end of the optical receiver.

A decision circuit removes noise from the received signal after it has been amplified to detectable logic levels. The decision circuit recovers a digital value from the received analogue signal. When the signal swing is large, the decision circuit probabilistically recovers the correct digital value. The decision circuit is timed by a CDR, which samples the serial digital data and recovers a clock signal from the incoming serial data via retiming [17]. The clock controlling the decision flip-flop must have a well-defined phase connection with the received data for the signal to be sampled at the optimal point during the bit period.

In the receiver (Rx), the demultiplexer (DMUX) is required to reconstruct the received serial data stream to the original parallel channels. As a result, a DMUX converts the incoming high-speed serial data stream into an N-bit bus capable of supporting electronic interconnects and digital processing. After recovering the electrical bus, digital signal processing blocks decode the bits, run error checks, and extract the payload data from the framing information [14].

# 1.3 Goal and Approach of this Thesis

As stated in the above section, TIA is, without a doubt, the most crucial building block of the optical receiver. This block's design necessitates noise, bandwidth, gain, and stability trade-offs. This thesis focuses on developing a transimpedance amplifier for the next generation of optical receivers using several nodes of IHP's SiGe: G2 BiCMOS technology. This thesis seeks to reveal the complications and challenges experienced when constructing differential TIA with high gain, wide bandwidth, and low noise.

The photodiode's peak-to-peak output current is 11.25  $\mu$ A, as illustrated in Figure 1.6. Because the TIA output voltage signal amplitude required for data recovery is several hundred millivolts, a high transimpedance gain of 60 dB $\Omega$  is aimed. Because of the TIA design's stringent noise and bandwidth constraints, the remaining gain must be performed at the post-amplifier. This thesis also includes a thorough

examination of the noise characteristics of TIAs. Because TIA is the first block in retrieving noisy data, the goal is to keep the noise in this block as low as feasible. The goal is to create a TIA with a differential input referred noise less than 20 pA/SqrtHz. Broad bandwidth is another trade-off in TIA implementation. A bandwidth of 40 GHz is desired. Another approach to eliminating common-mode noise and achieving wide bandwidth is using a differential topology.

Figure 1.6: Required specifications for TIA design.

Based on this goal, the following are the detailed contributions of this thesis:

- State-of-the-art research will be conducted to assess the performance of various topologies.

- A theoretical examination is to be done of all topologies in terms of transimpedance gain and input-referred noise.

- Schematic design of the best-performing topologies based on the theoretical study.

- After the theoretical and schematic study, develop the layout of one of the best-performing topologies.

- The selected TIA's performance will be compared to the state-of-the-art.

# 1.4 Thesis Structure

This project investigates the realization of a transimpedance amplifier designed in IHP SiGeG2-BiCMOS technology using cadence virtuoso software. As seen above, this chapter explains TIAs importance and which objectives are pursued with the design of a TIA. The flow chart shown in figure 1.7 gives a brief idea of how each chapter helps select the required topology for designing the TIA.

**Chapter 2** discusses the four state-of-the-art topologies possible for TIA design (i.e., common base (CB), common emitter (CE), regulated cascode (RGC), and

Figure 1.7: Thesis Structure

darlington pair (DP)). This chapter also explains why SiGe-HBT-BiCMOS process technology is advantageous over others on the market. The presented literature review allows putting the contributions of this thesis work into a broader context.

**Chapter 3** explains the figure of merits that are considered when designing the TIA. The terminology from this chapter can be encountered throughout the thesis.

**Chapter 4** details the basic working of the decided four topologies and their performance compared to each other according to the calculations. It will be clear why common base topology won't be investigated further after reading this chapter.

**Chapter 5** describes the schematic design of the TIA in SiGe BiCMOS technology using cadence virtuoso. The schematic design is presented for three topologies (i.e., CE, RGC, DP), followed by their simulation results. Hence after this chapter, why darlington pair topology is selected for layout design can be understood.

**Chapter 6** shows the layout of the darlington pair TIA with resistive feedback, followed by its post-layout improvement and outcomes. The findings of the layout are then compared to those of the schematic. The TIA's performance metrics, including transimpedance gain, 3-dB bandwidth, and input-referred noise, are assessed and contrasted for both the schematic and the layout.

**Chapter 7** finally gives us the conclusion of this thesis, the comparison of the designed TIA with state-of-the-art topologies, and the future scope of the work.

# Chapter 2 Literature Review

This chapter begins with a study of the literature on several state-of-the-art topologies. The list of topologies that can meet the TIA's performance requirements will be finalized using the results of this assessment. This is followed by a description of the state-of-the-art 130 nm SiGe BiCMOS technology that was used to design TIA.

### 2.1 State-Of-The-Art

A thorough literature review was performed to establish the current state of the field. The review's main objective was to find a preferred topology for the TIA's design. This thesis aims to design a TIA with a transimpedance gain of 60 dB $\Omega$ , a bandwidth of 40 GHz, and a differential IRN of 20 pA/ $\sqrt{\text{Hz}}$ , as stated in section 1.3. Hence, the topologies that are evaluated in this section are compared with each other for the above-targeted specifications. In chapter 4, the design concepts gleaned from the literature review are thoroughly covered.

A common base TIA with low input-referred noise of 14.5 pA/ $\sqrt{\text{Hz}}$  and a maximum gain of 71 dB $\Omega$  has been proposed by Zhen Zhang [18]. A bandwidth of 31 GHz has been attained using this topology. The proposed TIA was manufactured using SiGe BiCMOS technology at 130 nm. A modified variable-gain amplifier with automatic gain control is used to achieve a significant gain. The circuit now uses more space and power as a result.

A differential common emitter TIA has been implemented by García López [19] in a 130 nm SiGe:C BiCMOS technology with an  $f_t/f_{max} = 300/500$ GHz. This common emitter topology has a transimpedance gain of 62.5 dB $\Omega$ , a bandwidth of 60 GHz, and an IRN of 5.46 pA/ $\sqrt{\text{Hz}}$ . A resistive feedback resistor is used to increase the gain and bandwidth. Because of the low input impedance that this resistive feedback resistor achieved, the TIA's performance was enhanced. The thermal noise of this additional resistor causes a decline in the TIA's noise performance.

Joseph S. Weiner [20] used the same common emitter topology and resistive feedback to implement a TIA. Here, a fully differential SiGe TIA suitable for differential phase-shift keying applications has been described. This TIA has an input-referred current noise of less than 30 pA/ $\sqrt{\text{Hz}}$ , a 50 GHz 3-dB bandwidth, and a transimpedance gain of 49 dB $\Omega$ . The additional emitter follower circuit, which serves as a buffer, is then connected to the differential output stage. The bandwidth has improved as a result of this connection. As the bandwidth increased, the gain decreased, and the noise increased.

To design the TIA, Kentaro Honda [21] used the common emitter topology with resistive feedback. In this implementation, a level-shift circuit is positioned between the TIA and a post-amplifier stage which lessens the overall system's trade-off between bandwidth and noise. IRN is decreased by 70%. The designed TIA was produced using SiGe BiCMOS technology at 130 nm. The TIA has achieved input-referred noise of 14.8 pA/ $\sqrt{\text{Hz}}$ , a 3-dB bandwidth of 38.4 GHz, and a transimpedance gain of 72 dB $\Omega$ .

To illustrate the TIA, Garca López [22] uses regulated cascode topology in 250 nm SiGe:C BiCMOS technology with  $f_t/f_{max} = 110/180$ GHz. The results show an input-referred noise of 13.1 pA/ $\sqrt{\text{Hz}}$ , a 3-dB bandwidth of 32 GHz, and a transimpedance gain of 52.5 dB $\Omega$ . Low input impedance from a common emitter topology and a resistive feedback resistor, as demonstrated in the authors' earlier paper [19], reduces the impact of photodiode capacitance on bandwidth. The additional resistor's noise trade-off was present. Here, a cascode configuration is used to reduce this trade-off and increase bandwidth even without the use of a resistive feedback resistor. As a result, the circuit's noise won't impact; however, the voltage supply is increased to make room for the cascode topology's stacked transistors.

In 130 nm SiGe BiCMOS technology, S. Bashiri Amid [23] implemented a broadband differential TIA. The large parasitic capacitor of the photodiode has been lessened by using a regulated cascode configuration. The TIA has a measured bandwidth of 28 GHz and a 53.6 dB $\Omega$  differential transimpedance gain. An Integrated IRN of 36.5 pA/ $\sqrt{\text{Hz}}$  was measured. Three stages of buffer circuits follow the designed TIA for better performance. The additional buffer circuits cause the chip's overall power consumption to increase to 110 mW.

Using IBM8HP 130 nm SiGe BiCMOS technology and a 240/200 GHz f<sub>t</sub>/f<sub>max</sub>, Ran Ding [24] has demonstrated a power-efficient, low-noise, and broadband TIA. The paper employs a resistive feedback topology with a darlington pair. The circuit uses only 89 mW of DC power and has a transimpedance gain of 55 dB $\Omega$ , an 86 GHz bandwidth, and an input-referred noise of 20.4 pA/ $\sqrt{\text{Hz}}$ . The designed circuit consists of three cascaded stages: an input transimpedance stage called a shuntfeedback darlington amplifier, a buffering emitter follower, and an output stage called a cascode transadmittance stage.

For the single-ended TIA design, André F. Ponchet [25] used the darlington pair topology with resistive feedback. The TIA has a transimpedance gain of 50.5 dB $\Omega$ , a bandwidth of 42 GHz, and an input-referred noise of 12 pA/ $\sqrt{\text{Hz}}$ . Darlington pair circuits in two stages are used to achieve these TIA performances.

Using cascaded stagger-tuned stages that are equalized for high bandwidth and low gain ripple, Joohwa Kim [26] developed a broadband amplifier. A constructive wave amplifier and a darlington feedback amplifier illustrate the staggered stages. The designed amplifier is implemented in a 120 nm SiGe BiCMOS process and, with the entire circuit, achieves a 3-dB bandwidth of 102 GHz. A transimpedance gain of 47 dB $\Omega$ , a 3-dB bandwidth of 53 GHz, and input-referred noise of 14.8 pA/ $\sqrt{\text{Hz}}$  are all achieved by the TIA component in the designed amplifier.

We have seen four different topologies for implementing the necessary TIA. They consist of a common base, a common emitter with resistive feedback, a regulated cascode, and a darlington pair with resistive feedback. A concise table 2.1 compares the findings from the state-of-the-art papers mentioned. These implementations

| Reference                    | [18]                    | [19]                      | [20]           | [21]                    | [22]                    | [23]                    | [24]                    | [25]                    | [26]                    |

|------------------------------|-------------------------|---------------------------|----------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| Technology                   | 130nm<br>SiGe<br>BiCMOS | 130nm<br>SiGe:C<br>BiCMOS | SiGe<br>BiCMOS | 130nm<br>SiGe<br>BiCMOS | 250nm<br>SiGe<br>BiCMOS | 130nm<br>SiGe<br>BiCMOS | 130nm<br>SiGe<br>BiCMOS | 130nm<br>SiGe<br>BiCMOS | 120nm<br>SiGe<br>BiCMOS |

| Topology                     | CB                      | CE RSF                    | CE RSF         | CE RSF                  | RGC<br>RSF              | RGC<br>RSF              | DP RSF                  | 2 stage<br>DP RSF       | DP RSF                  |

| Input-Output                 | Pseudo-<br>Diff         | Diff-Diff                 | Diff-Diff      | SE-SE                   | Diff-Diff               | Diff-Diff               | SE-SE                   | SE-SE                   | SE-SE                   |

| $\mathbf{Frequency} \ (GHz)$ | 30                      | 55                        | 40             | 30                      | 50                      | 30                      | 50                      | I                       | 40                      |

| Transimp. Gain $(dB\Omega)$  | 71                      | 62.5                      | 49             | 72                      | 52.5                    | 53.6                    | 55                      | 50.5                    | 47                      |

| <b>Bandwidth</b> (GHz)       | 31                      | 60                        | 50             | 38.4                    | 32                      | 28                      | 86                      | 42                      | 53                      |

| <b>IRN</b> $(pA/\sqrt{Hz})$  | 14.5                    | 5.46                      | 30             | 14.8                    | 13.1                    | 36.5                    | 20.4                    | 12                      | 53.9                    |

| <b>Output Matching</b> (dBm) | -20                     | -10                       | -12            | I                       | -10                     | -15                     | -19                     | -25                     | -8                      |

| Peaking/Buffers              | yes                     | yes                       | yes            | yes                     | yes                     | yes                     | yes                     | no                      | no                      |

| DC power cons. (mW)          | 300                     | 85                        | 200            | 261                     | 70                      | 110                     | 89                      | 45                      | 73                      |

| ft/fmax (GHz)                | I                       | 300/500                   | 170/140        | I                       | 95/140                  | 160/-                   | 200/240                 | I                       | 200/-                   |

| Chip size $(mm^2)$           | 0.54                    | 0.3                       | 0.92           | 0.2                     | 0.32                    | 0.56                    | 0.28                    | 0.23                    | 0.29                    |

Table 2.1: Comparison of State-of-the-Art TIA Circuits

have used extra circuitry, such as peaking or buffering circuits, for increasing gain, bandwidth, and noise immunity. There is a noticeable increase in the amount of space or power consumed due to additional circuits. Therefore, our goal is to choose a topology that can deliver the TIA performance we need without the addition of a second circuit. In chapter 4, these four topologies are covered in more detail. The targeted TIA in this thesis should be implemented in 130 nm SiGe HBT BiCMOS technology; the next section will concentrate on this technology.

# 2.2 130 nm SiGe HBT BiCMOS Technology

To encode the optical carrier reliably in a transceiver, drivers capable of high-speed broadband operation while generating large output swings are required on the Tx side. On the Rx side, low-noise, high-speed devices with wide bandwidth are preferred. The fibre communication system's massive data transfer potential is virtually unfulfilled because establishing a broad bandwidth is constrained by the speed of front-end circuits. As a result, their design is the most crucial aspect of optical transceiver design. The fundamental goal of this thesis research is to investigate, design, and build a front-end transimpedance amplifier of an optical receiver employing cutting-edge SiGe bipolar technology. This section explains the semiconductor technologies used in optoelectronic applications and why SiGe HBT BiCMOS is the best option among them.

Commercial optical communication products are often implemented in III-V compound semiconductor technologies such as gallium arsenide (GaAs) [27] and indium phosphide (InP)[28], which provide extremely high performance but are not appropriate for cost-sensitive mass-market applications. For lower-cost silicon implementations, two key alternatives remain: CMOS and SiGe. Because of its scaling techniques, CMOS has been employed for many applications over the years. By reducing the gate length, the current gain frequency is continuously increased. These applications operate at frequencies in the tens of gigahertz range [29]. Technology is currently heading into the terahertz (THz) realm, where many new applications demand faster CMOS transistors. Although CMOS is commonly employed for lowfrequency applications, SiGe technology has long been regarded as the gold standard for sub-Terahertz and mm-wave applications. CMOS has cost and power dissipation advantages. Still, at a comparable lithography node, it has lower breakdown voltages and worse noise characteristics than SiGe HBTs, which dramatically penalizes circuit performance [30]. As shown in Figure 2.1 [31], the TIA reported in this study is implemented in 130nm IHP SiGe BiCMOS, which provides a good trade-off between high-frequency device performance and manufacturing costs.

Compared to RF CMOS, which achieves a unity gain f<sub>T</sub> of around 200GHz in the 65nm node, SiGe HBT BiCMOS reaches the same value in the 250nm node. As a result, the fabrication costs are reduced for the same performance. SiGe BiCMOS offers more than double the performance of CMOS at the same price [32]. The 130nm SiGe HBT BiCMOS technologies used in the design of this TIA have an available back-end line stack of eight metal layers, with five thin and three thick metal stacks. Four thin metal layers and two large metal layers are based on 130nm design criteria, and the final two top metal layers, with thicknesses of 2.8  $\mu$ m and 0.6  $\mu$ m, are suited for constructing RF passive components.

Figure 2.1: Comparison between BiCMOS and CMOS technologies with respect to RF performance vs cost [31].

### Operation

A heterojunction bipolar transistor (HBT) is a high-performance silicon technology than that of conventional silicon bipolar and silicon CMOS. HBT is formed by adding Ge composition in the base region of a bipolar junction transistor (BJT). While maintaining the properties of the BJT, incorporating Ge into the base of the device introduced several other benefits by changing the base bandgap of SiGe HBTs [33]. The bandgap is reduced due to compressive strain in the material when Ge is added to the silicon crystal lattice (the Ge atom requires a larger atomic separation than the Si atom). In SiGe HBT technology, the Ge content is inconsistent throughout the base. Instead, it increases as we move deeper into the collector from the emitter, thus reducing the bandgap in the direction of electron flow, as shown in Figure 2.2 bottom. When the electrons are injected from the emitter, they experience a reduced barrier to injection because of the smaller Ge content at this junction. Then the electrons experience an accelerating field from the increasing Ge content towards the collector, as shown in Figure 2.2 top, increasing the transportation speed of the electrons in the device, thus, higher operating frequency. Higher current gain can be achieved by increasing the base doping concentration and reducing the emitter doping concentration. Thus, the base resistance, maximum oscillation frequency, noise figure, base-width modulation effect, and emitter bandgap narrowing effect are greatly improved [34]. Compared with an identically constructed Si BJT, a higher gain, lower RF noise, and low 1/f noise can be achieved with SiGe HBT.

Figure 2.2: Ge concentration (bottom) and band structure (top) of a SiGe heterojunction bipolar transistor.

#### **Comparison of Different SiGe Process Foundries**

In the last decades, the transit frequency has continuously increased, with special attention paid to the f<sub>max</sub>. For example, IHP has developed its 2nd generation 130 nm technology SG13G2 with f<sub>T</sub>/f<sub>max</sub> = 300/450 GHz from its predecessor 130nm technology with f<sub>T</sub>/f<sub>max</sub> = 250/340 GHz. Table 2.2 shows the Peak transit frequencies for different high-speed SiGe HBT technologies.

In this project work, IHP SG13G2 BiCMOS technology is used for designing the TIA. As shown in Table 2.2, it offers a much higher bipolar performance of  $f_T/f_{max} = 300/450$  GHz when compared with other technologies. It has the state-of-the-art SiGe BiCMOS transistors that produce an ultra-fast, low-noise, low-power consumption amplifiers compared to its competitors.

| Company  | Process | CMOS Node (nm) | $f_{T}$ (GHz) | f <sub>max</sub> (GHz) |

|----------|---------|----------------|---------------|------------------------|

| IBM [35] | 8HP     | 130            | 200           | 270                    |

| STM [36] | B9MW    | 130            | 230           | 290                    |

| IHP [37] | SG13S   | 130            | 250           | 340                    |

| IFX [38] | B11HFC  | 130            | 250           | 370                    |

| IHP [39] | SG13G2  | 130            | 300           | 450                    |

Table 2.2: Peak transit frequencies for different high-speed SiGe HBT technologies.

# Chapter 3

# **Design** Considerations