# Device Design and Process Integration of SiC Trench MOSFETs

\*<u>Minwho Lim</u>, Oleg Rusch, Tobias Erlbacher and Anton Bauer Fraunhofer Institute for Integrated Systems and Device Technology **IISE**

The 5<sup>th</sup> International Symposium on SiC Materials and Devices 2021 November 25, 2021, Lotte Hotel Busan, Korea

Semiconductor Device

5<sup>th</sup> International Symposium on SiC Materials and Devices 2021

- Motivation

- Additional shielded TrenchMOS design

- Exploiting benefits of trench-first process

- Design optimization of Double-TrenchMOS

- Initial design proposal

- Process flow modeled by using process simulation

- Static electrical characteristics by using device simulation

- Process Integration

- Edge termination verified simulation

- Gate oxide reliability and interface quality

### Conclusion

Semiconductor Device

### Motivation

- Additional shielded TrenchMOS design

- Exploiting benefits of trench-first process

- Design optimization of Double-TrenchMOS

- Initial design proposal

- Process flow modeled by using process simulation

- Static electrical characteristics by using device simulation

- **Process Integration**

- Edge termination verified simulation

- Gate oxide reliability and interface quality

### Conclusion

Semiconductor Device

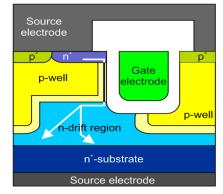

### State of the Art Additional shielded TrenchMOS Design

#### Trench structure compared to planar structure

- © Higher cell density w/o JFET region

- Higher mobility due to vertical channel

- $\rightarrow$  Reduction of resistance

- ightarrow Saving chip area and chip cost

•  $\rho_{DS,on} = 2.8 \text{ m}\Omega \text{cm}^2$

Semiconductor Device

5<sup>th</sup> International Symposium on SiC Materials and Devices 2021

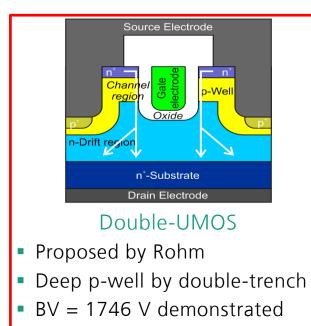

Single channel-UMOS

- Proposed by Infineon

- Deep p-well by single channel

- BV = 1366 V demonstrated

- $\rho_{\text{DS,on}} = 3.2 \text{ m}\Omega\text{cm}^2$

- <sup>(3)</sup> Needed stable technology for trench etching

- 😕 Gate oxide reliability has to be improved

- ightarrow Additional shielding required

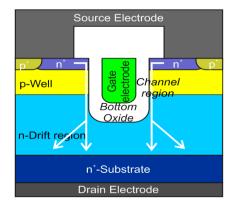

#### Thick bottom oxide-UMOS

- Proposed by Bosch

- Thick bottom oxide

- 1.5 mΩcm<sup>2</sup> at 600 V

- 2.7 mΩcm<sup>2</sup> at 1200 V

# **Exploting Benefits of Trench-First Process**

Stable technology of critical fabrication step

### "Implantation-First" process

- A maximal alignment accuracy is allowed

- Difficulty to control the etching behavior

- Undesirable RIE-rate for ion-implanted silicon carbide

- Optimal etching process needed for every implantation parameters

- Obstacle by passivating layer and persistent Si + O layers

### "Trench-First" process

- Stable SiC-trench etching

- High temperature annealing

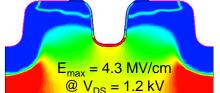

- → Reshaping trench formation to minimize dielectric breakdown field concentration

- → H<sub>2</sub>-etching is favorable for surface conditioning [1].

- Implantation mask is required?

- → Self-aligned process proposed!

Semiconductor Device

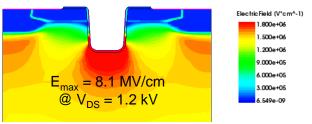

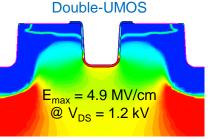

#### **Conventional UMOS**

#### Reshaped Double-UMOS

### Motivation

- Additional shielded TrenchMOS design

- Exploiting benefits of trench-first process

### Design optimization of Double-TrenchMOS

- Initial design proposal

- Process flow modeled by using process simulation

- Static electrical characteristics by using device simulation

### **Process Integration**

- Edge termination verified simulation

- Gate oxide reliability and interface quality

### Conclusion

Semiconductor Device

Design proposal

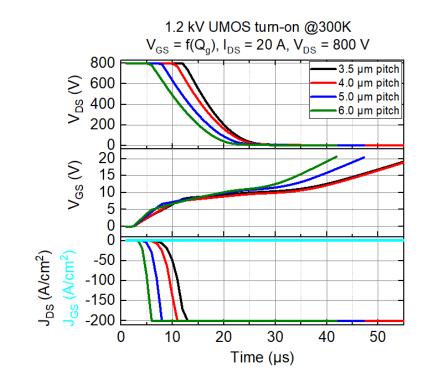

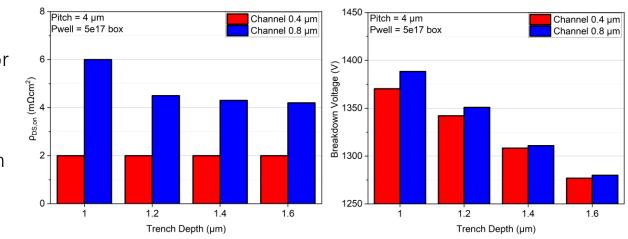

#### Technology variation

- Performance vs. Manufacturability

- Performance vs. Shielding for gate oxide

- Pitch: ... / 3.5 μm / 4.0 μm / 5.0 μm / ...

### TCAD simulation

- Charge compensation

- D<sub>it</sub> from planar devices

- Smaller cell pitch

- $\rightarrow$  Lower R<sub>DS,on</sub>, higher BV

Semiconductor Device

5<sup>th</sup> International Symposium on SiC Materials and Devices 2021

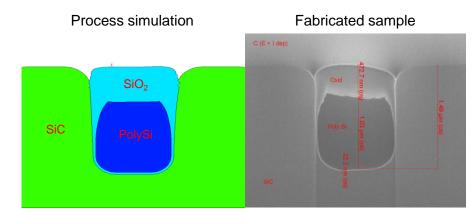

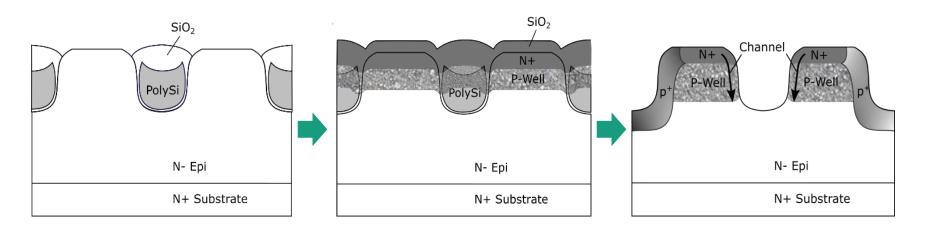

Process flow of fabricated devices based on modeling by using process simulation

#### Self-aligned n+-source and p-well implantation

- Deposited and planarized Poly

- Low temperature oxidizing Poly

- Independent on the resolution of lithography system

- Channel length can be controlled by determination of oxide thickness

- Formation of oxide-cap can be surely predicted by calibrated process simulation

Semiconductor Device

5<sup>th</sup> International Symposium on SiC Materials and Devices 2021

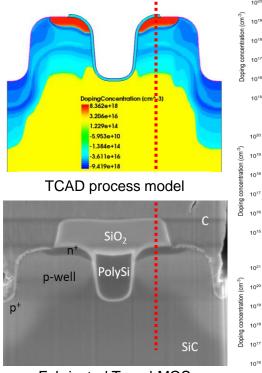

Process flow of fabricated devices based on modeling by using process simulation

SIMS (N)

# Ion-Implantation from MC process simulation calibrated by

- SEM dopant contrast quantitatively

- SIMS measurement qualitatively

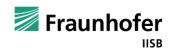

#### Fabricated TrenchMOS

200

400

Depth (nm)

600

800

of doping concentration for n

#### p-well implantation optimization

- Appropriate p-well parameter should be verified due to a trade-off

- Too lower doses prone to reach-through breakdown effect

- Too higher doses cause higher resistance and threshold voltage

Semiconductor Device

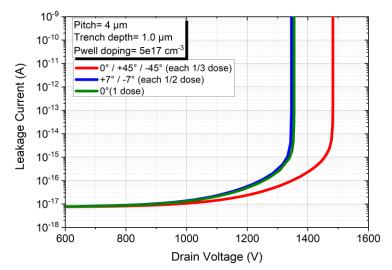

Process flow of fabricated devices based on modeling by using process simulation

### p+-shielding implantation

- Tilted implantation proposed

- Trench width : depth = 1: 1

- → +45° / -45° / 0° for symmetrical doping profile

- Too high energy or doses are to be cautiously used due to deteriorating R<sub>DS,on</sub> from increasing the effectiveness of JFET region between p-body

### Trench depth

- Deeper trench is not absolutely beneficial for BV with limited max. implant energy

- Optimized channel length for trench depth accordingly

Semiconductor Device

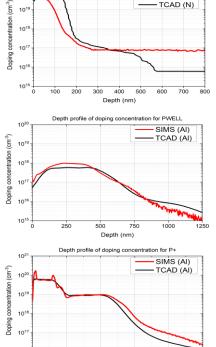

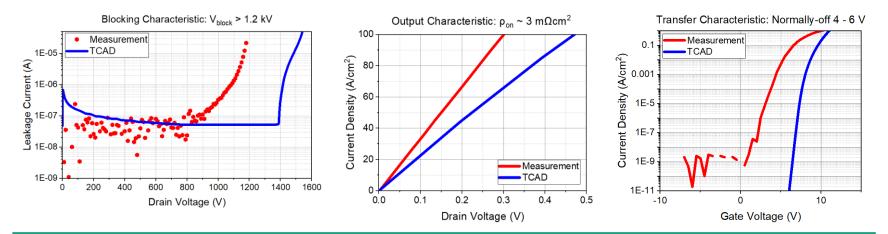

Static electrical characteristic

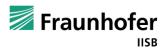

### Achieved ~1.2 kV and > 50A devices $\rightarrow$ Room for improvement

- Blocking capability

- Short channel effect: Possibility for higher blocking voltage (~1.6 kV) with optimized pwell implantation parameters

- Tilted p<sup>+</sup>-shielding implantation

- Output- and transfer characteristic

- o Design optimization: Short circuit causing increased leakage current

- o Misalignment field oxide and shallow n+-source regioin should undergo improvment

- Gate oxide optimization for higher mobility, dielectric breakdown field strength and improved threshold voltage shift

Semiconductor Device

5<sup>th</sup> International Symposium on SiC Materials and Devices 2021

- Motivation

- Additional shielded TrenchMOS design

- Exploiting benefits of trench-first process

- Design optimization of Double-TrenchMOS

- Initial design proposal

- Process flow modeled by using process simulation

- Static- and dynamic electrical characteristics by using device simulation

- Process Integration

- Edge termination verified simulation

- Gate oxide reliability and interface quality

### Conclusion

Semiconductor Device

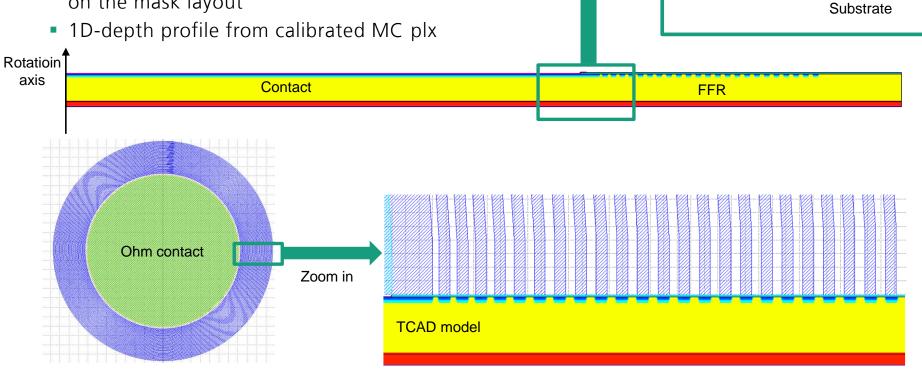

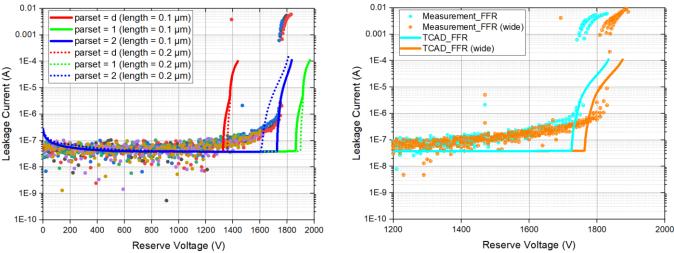

### **Process Integration**

Edge Termination verified by TCAD simulation

#### Floating Field Ring

- Device simulation of breakdown behavior

- Comparison with measured data for 1.2 kV devices

- Rotationally symmetric 2D-simulation setup based on the mask layout

Semiconductor Device

5<sup>th</sup> International Symposium on SiC Materials and Devices 2021

Epi

### **Process Integration**

Edge Termination verified by TCAD simulation

#### Floating Field Ring

- Breakdown behavior depending on lateral scattering (parameter "length")

- Avalanche model dependency:

- o d (default): Van Overstareten

- o parset = 1: Application Library

- o parset = 2: Material DB

- Optimal ring distance for increasing blocking capability

- Model calibration for JTE, Trench-FFR and SJ-FFR for HV (> 3.3kV) devices

length = 0.1 μm Deprecentent 500e+19 1.054+17 2.178e+14 -2.509+10 -2.554+14 -1.359+10

Semiconductor Device

5<sup>th</sup> International Symposium on SiC Materials and Devices 2021

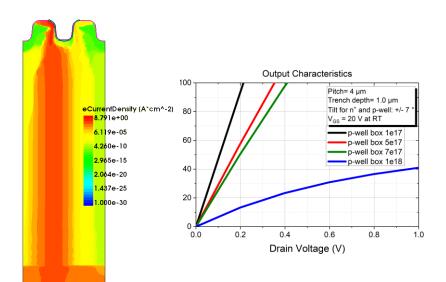

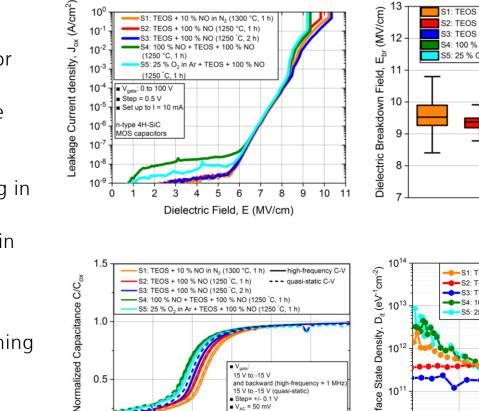

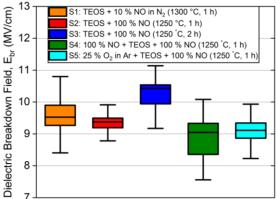

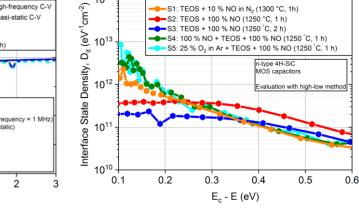

### **Process Integration** Gate Oxide Reliability and Interface State Density

10

10<sup>-1</sup>

10<sup>-2</sup>

10-3

10-4

10-5

0.0

-3

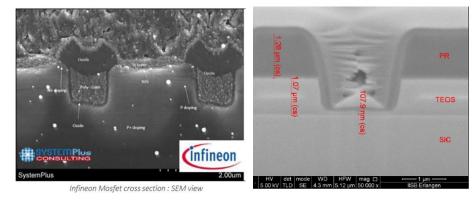

#### TEOS as precursor

- Planar MOS capacitors

- TEOS gate oxide suited for Trench Gate devices

- Conformal trench oxide with high gate oxide integrity

- Post-deposition-annealing in NO in different ambient

- Pre-deposition oxidation in NO or  $O_2$  deleterious for dielectric strength and surface quality

- High temperature H<sub>2</sub>-etching is favorable for surface conditioning [2]

- Connected with trench  $\bigcirc$ reshaping

n-type 4H-SiC MOS capacitors

0

Gate Voltage (V)

TEOS + 10 % NO in N2 (1300 °C, 1 h)

TEOS + 100 % NO (1250 °C, 1 h)

TEOS + 100 % NO (1250 °C, 2 h)

100 % NO + TEOS + 100 % NO

S5: 25 % O2 in Ar + TEOS + 100 % NO

(1250 °C, 1 h)

(1250 °C, 1 h

■ V<sub>gate</sub>: 0 to 100 \ Step = 0.5 V

Set up to I = 10 mA

Minwho Lim et al., ICSCRM 2019

5<sup>th</sup> International Symposium on SiC Materials and Devices 2021

-1

-2

### Conclusion

- Trench-First process facilitates feasible devices enabling

- Self-aligned process controlled by oxidation parameters

- Various customized ion implantation with stable trench formation

- Room for design improvement depending on foundry (narrow cell, deeper trench etc.)

- Process integration

- TCAD modeling matching actual design could verify the further advanced edge termination for high voltage devices

- Gate oxide can be further optimized based on deposited homogene oxide type

# Thank you for your attention!

#### Acknowledgement

This work was supported by GRDC Program through the National Research Foundation (NRF) funded by the MSIT of Korea (NRF-2017K1A4A3013716).

#### Fraunhofer IISB

Schottkystraße 10 91058 Erlangen Germany

Minwho Lim Department "Semiconductor Devices" Group "Device Development" Tel: +49 (0) 9131 761-495 minwho.lim@iisb.fraunhofer.de www.iisb.fraunhofer.de

Semiconductor Device