## Packaging Technologies in Power Electronic Modules @Fraunhofer IISB

## Content

#### **Part One**

Some Words on Fraunhofer Institutes - from the general to the specific -

**Part Two**

Packaging Technologies in Power Electronic Modules

#### FRAUNHOFER GESELLSCHAFT

## **JOSEPH VON FRAUNHOFER** (1787 – 1826)

00 000 0

The **Fraunhofer-Gesellschaft** is a recognized non-profit organization that takes its name from '**Joseph von Fraunhofer**' (1787–1826), the illustrious Munich researcher, inventor and entrepreneur.

- Researcher discovery of the 'Fraunhofer lines' in the solar spectrum

- Inventor new processing method for lenses

- Entrepreneur director and partner in a glassworks

- Fraunhofer foundation in 1949

- → from military to recent industrial research and engineering (today's staff 24,500)

#### FRAUNHOFER GESELLSCHAFT

## **INSTITUTES AND RESEARCH ESTABLISHMENTS** IN GERMANY

#### Fraunhofer Research Institutes

- Legal status: Non-profit association (e.V.)

- Mission: Application-oriented R&D

- 72 institutes with approx. 2.1 billion euros budget

- Through contract research 1.9 billion euros

- About 70 pct. of the Fraunhofer-Gesellschaft's contract research revenue comes from publicly financed research projects

#### FRAUNHOFER GESELLSCHAFT $\rightarrow$ FRAUNHOFER IISB

## POWER ELECTRONIC SYSTEMS

From Material to Power Electronic Applications

SIMULATION MATERIALS TECHNOLOGY AND MANUFACTURING DEVICES AND RELIABILITY VEHICLE ELECTRONICS ENERGY ELECTRONICS

#### FRAUNHOFER IISB → DEPARTEMENT

## **DEVICES AND RELIABILITY**

IISB

Departement DEVICES AND RELIABILITY © Fraunhofer IISB

#### DEPARTMENT → GROUP

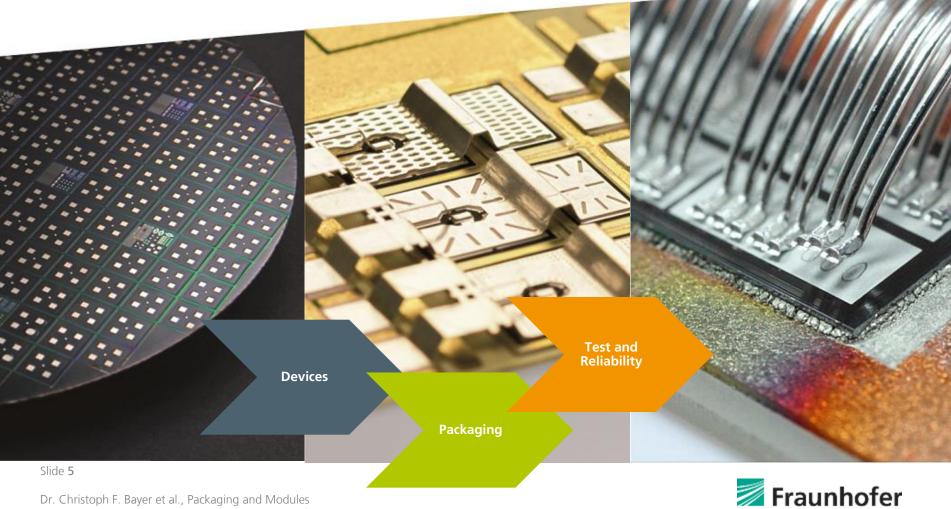

## **PACKAGING AND MODULES**

New Concepts and Materials for Packaging

High Performance Joining Technologies, Sintering

Thermal, Electrical, and Mechanical Characterization

Lifetime Characterization, Statistical Analysis

Analysis of Failure Mechanism

Lifetime Modeling

Slide 6

## Packaging Technologies in Power Electronic Modules

Packaging and interconnection technologies for power electronics

- Comparison and evaluation of packaging methods

- Packaging concepts

- Interconnection technologies

- Packaging at Fraunhofer IISB

- Thermal design and insulation coordination

- Simulation process and theoretical consideration

- Test procedure and analysis

- General

- AQG 324 (LV 324)

- Test setups and parameters

- Summary

Slide 7

## Packaging Technologies in Power Electronic Modules

#### Packaging and interconnection technologies for power electronics

- Comparison and evaluation of packaging methods

- Packaging concepts

- Interconnection technologies

- Packaging at Fraunhofer IISB

- Thermal design and insulation coordination

- Simulation process and theoretical consideration

- Test procedure and analysis

- General

- AQG 324 (LV 324)

- Test setups and parameters

- Summary

Slide **8**

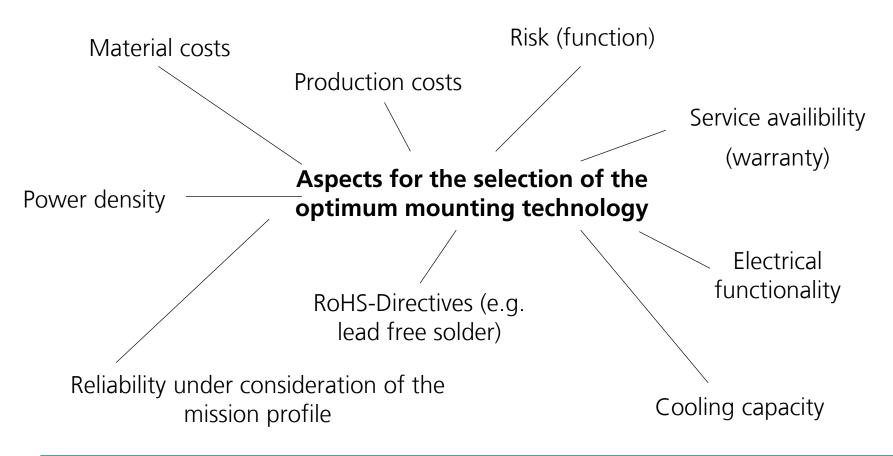

### **Basics and materials**

## What should be considered?

Dr. Christoph F. Bayer et al., Packaging and Modules Departement DEVICES AND RELIABILITY © Fraunhofer IISB

#### **Basics and materials**

| Material costs                                          | Production/process costs                                                   | Risk costs                                                                     |

|---------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| <b>Semiconductor</b><br>(Diode, MOSFET, IGBT, etc.)     |                                                                            |                                                                                |

| <b>Die attach</b><br>(Solder, Sinterpaste, etc.)        | <b>Machinery and equipment</b><br>(stencils, soldering adapters,           | <b>Failure</b><br>(malfunction after assembly,<br>damage during assembly, pre- |

| Substrate/ circuit carriers<br>(PCB, DCB, IMS, etc.)    | bonding tool, etc.)                                                        | damaged components due to delivery, etc.)                                      |

|                                                         | Employee                                                                   |                                                                                |

| <b>Bonding wires</b><br>(thin/thick wire, Cu, Al, etc.) | (preliminary tests, main tests,<br>optimization, quality control,<br>etc.) | <b>Reserve</b><br>(backup stock of<br>semiconductors, die attach,              |

| <b>Heat sink, base plate</b> (Al, Cu, Graphite, etc.)   |                                                                            | tools, etc.)                                                                   |

| Housing                                                 |                                                                            |                                                                                |

**Basics and materials**

#### **Basics and materials**

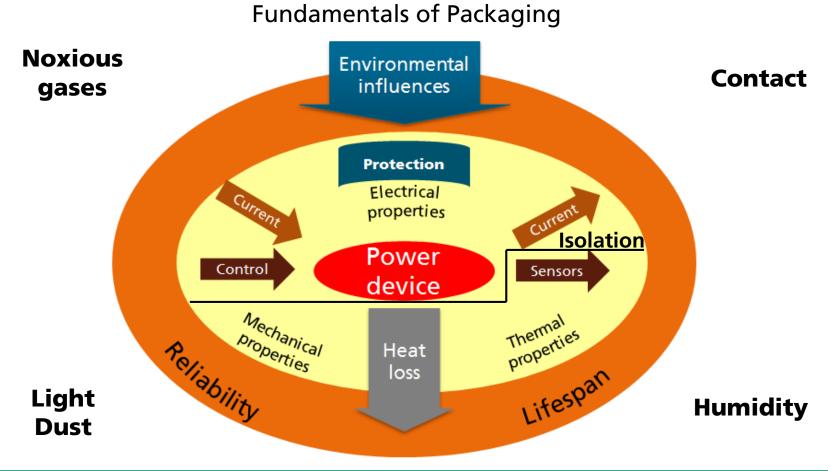

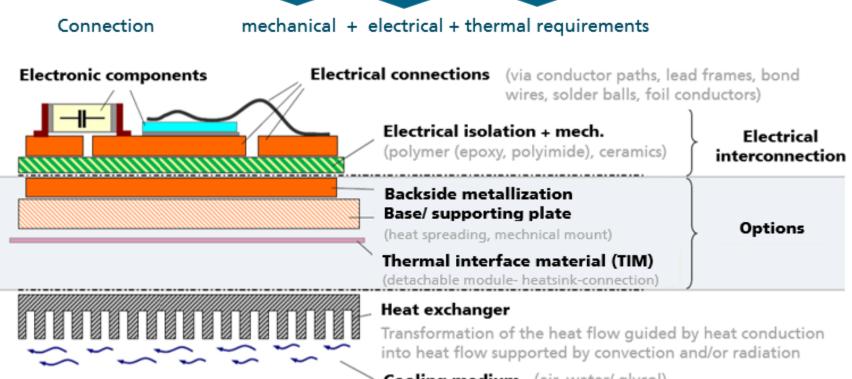

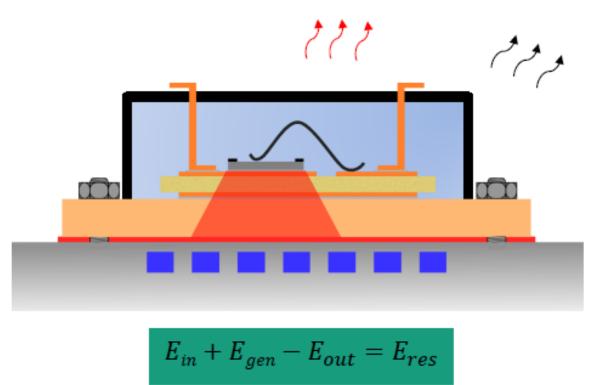

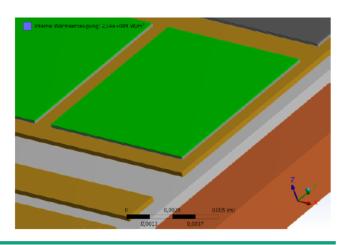

Packaging technology: fixation, contact and cooling of the components

Cooling medium (air, water/glycol)

## **Basics and materials**

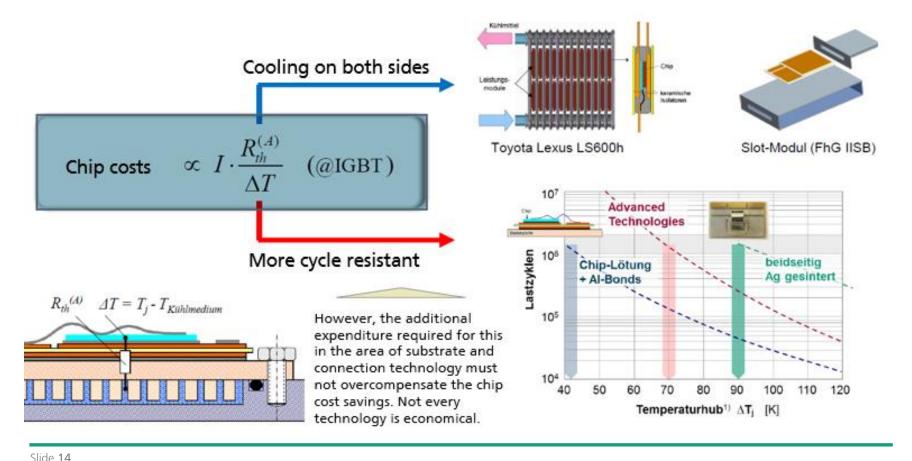

Cost reduction through better cooling and/or higher chip temperatures

## Packaging Technologies in Power Electronic Modules

Packaging and interconnection technologies for power electronics

- Comparison and evaluation of packaging methods

- Packaging concepts

- Interconnection technologies

- Packaging at Fraunhofer IISB

- Thermal design and insulation coordination

- Simulation process and theoretical consideration

- Test procedure and analysis

- General

- AQG 324 (LV 324)

- Test setups and parameters

- Summary

Slide 15

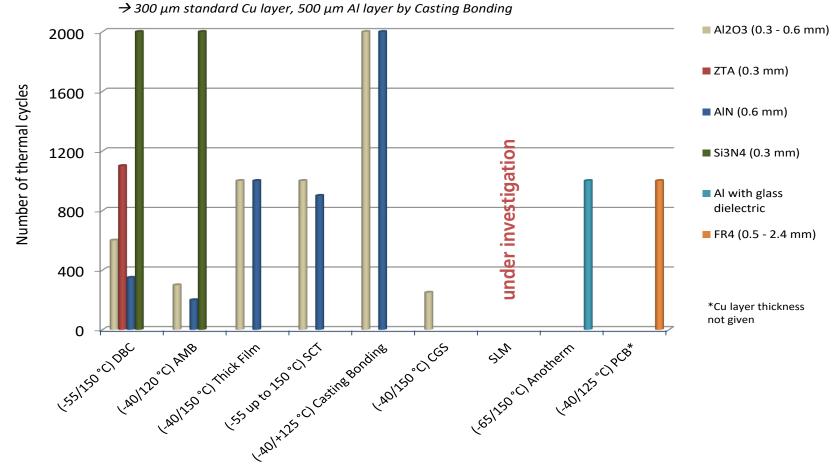

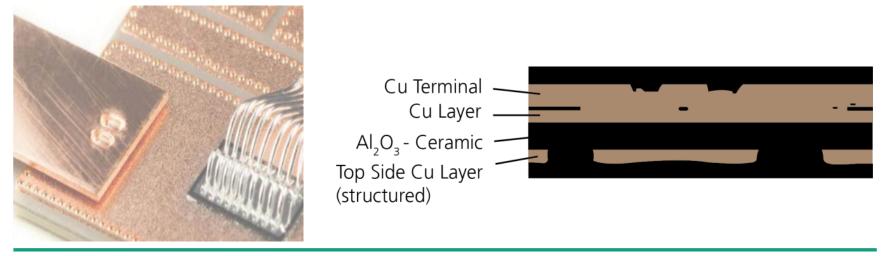

### Substrate technologies - Inorganic

- Direct Copper Bonded (DCB)

- Composite of ceramic and metal

- Very often used for PE applications

- Ceramic  $\rightarrow$  Al<sub>2</sub>O<sub>3</sub> / ZTA / AlN / Si3N4

- Metallization  $\rightarrow$  Cu / Al

| Ization → Cu / AI                            | Al <sub>2</sub> O <sub>3</sub> | ZTA       | AIN       | Si <sub>3</sub> N <sub>4</sub> |

|----------------------------------------------|--------------------------------|-----------|-----------|--------------------------------|

| K1C in MPa⋅m <sup>1/2</sup>                  | 4 - 5.5                        | 4.4 - 5   | 2.7       | 5 – 8.5                        |

| Elastic modulus<br>in GPa                    | 400                            | 380       | 310       | 290 - 330                      |

| Flexural strength<br>in MPa                  | 230 - 580                      | 400 - 480 | 200 - 360 | 700 - 1100                     |

| Thermal conductivity<br>in W/mk              | 15 - 30                        | 15        | 180 - 220 | 15 - 85                        |

| CTE in 10⁻⁵K⁻¹<br>(30 - 1000 °C)             | 6 - 8                          | 9 - 11    | 4.5 - 5.6 | 2.5 - 3.5                      |

| Dielectric strength<br>in kVmm <sup>-1</sup> | 15 - 17                        |           | > 20      | 20                             |

### Substrate technologies - Inorganic

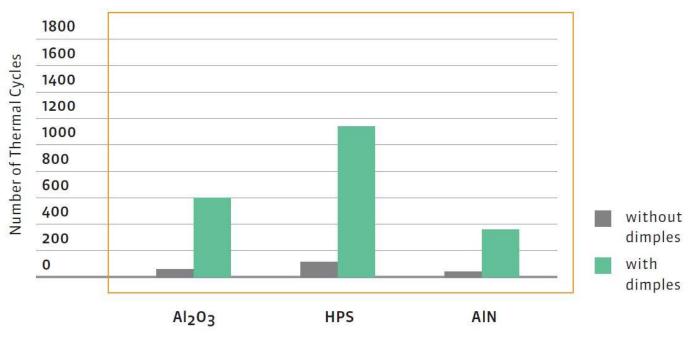

- Direct Copper Bonded (DCB)

- DCBs with dimples  $\rightarrow$  up to 10 times longer service life

- Test condition from -50 °C to +150 °C

Lifetime

CURAMIK ELECTRONICS GMBH: DBC technology : Design Rules Version 12/2014, 2014

### Substrate technologies - Inorganic

- Active Metal Brazing (AMB)

- Composite of ceramic and metal with active solder

- Alternative to DCB

- Ceramic  $\rightarrow$  Al<sub>2</sub>O<sub>3</sub> / AlN / Si3N4

- Metallization → Cu

|                                            | Cu thickness<br>in mm | Cycles<br>from<br>-40 to 125 °C |

|--------------------------------------------|-----------------------|---------------------------------|

|                                            | 0.2                   | > 3000                          |

| Si₃N₄                                      | 0.3                   | > 3000                          |

| (0.32t)                                    | 0.4                   | > 3000                          |

|                                            | 0.5                   | > 3000                          |

| AIN<br>(0.635t)                            | 0.2                   | 300                             |

|                                            | 0.3                   | 200                             |

|                                            | 0.4                   | Crack at AMB<br>Process         |

|                                            | 0.5                   | Crack at AMB<br>Process         |

|                                            | 0.2                   | 500                             |

| Al <sub>2</sub> O <sub>3</sub><br>(0.635t) | 0.3                   | 300                             |

|                                            | 0.4                   | 200                             |

|                                            | 0.5                   | 100                             |

KYOCERA: AMB Cu-Bonded Ceramic Substrates for Power Modules, 2014

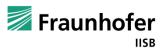

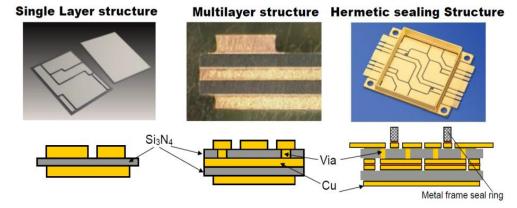

## Substrate technologies - Inorganic

- Thick Film Technology (TFT)

- Copper paste metallization

- Steps in metallization possible for signal and power

- Ceramic  $\rightarrow$  Al<sub>2</sub>O<sub>3</sub> / ZTA / AlN

GUNDEL, Paul et al.: Thick Printed Copper as Highly Reliable Substrate Technology for Power Electronics. In: PCIM Europe 2015

Dr. Christoph F. Bayer et al., Packaging and Modules Departement DEVICES AND RELIABILITY © Fraunhofer IISB

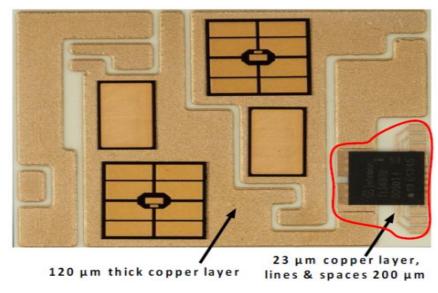

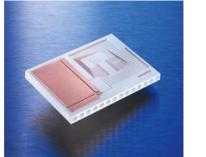

## Substrate technologies - Inorganic

- Structured Copper Technology (SCT)

- Copper paste metallization

- Ceramics as substrate **and** heat sink

- Saving of the connection levels

- Ceramic  $\rightarrow$  Al<sub>2</sub>O<sub>3</sub> / AlN

CERAMTEC: Advanced Ceramic Material Properties for the Electronics Industry

Fraunhofer

### Substrate technologies - Inorganic

- Anotherm

- Copper paste metallization

- Ceramics as substrate and heat sink

- Saving of the connection levels

- Ceramic  $\rightarrow Al_2O_3 / AlN$

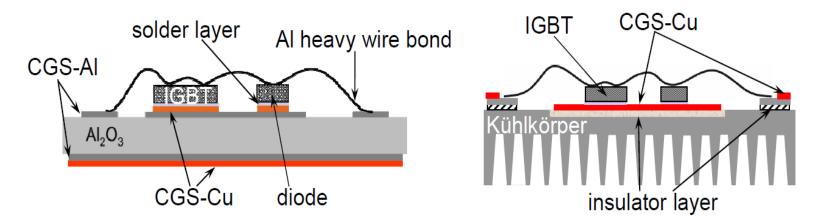

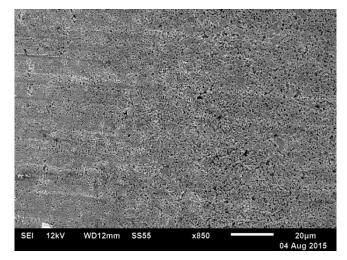

### Substrate technologies - Inorganic

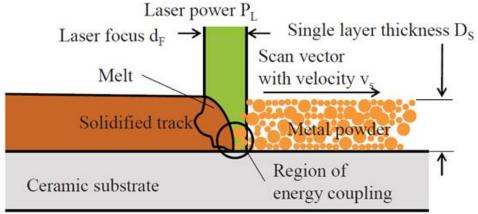

- Cold Gas Spraying (CGS)  $\rightarrow$  under development

- Apply metal powder to ceramic substrate

- Electrical conductivity ~ 80 % of DCB metallization

- $R_{th} \rightarrow \sim 13$  % higher than DBC

- Metallization  $\rightarrow$  Cu / Al

- Ceramic  $\rightarrow Al_2O_3$

WILDE, J.; WIELAGE, B.: Case Study: Cold Gas Spraying (CGS) Metallization Based Ceramic Substrates., 2010

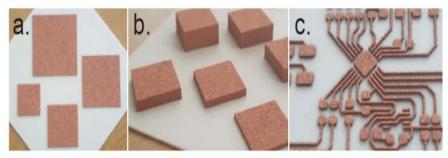

## Substrate technologies - Inorganic

- Selective Laser Melting (SLM)  $\rightarrow$  under development

- Applying metal powder to ceramic by means of laser technology

- Steps in metallization possible

- Metallization  $\rightarrow$  Cu

- Ceramic  $\rightarrow$  Al<sub>2</sub>O<sub>3</sub>

SYED-KHAJA, Aarief ; PEREZ, Philip Patino ; FRANKE, Joerg: Production and Characterization of High-temperature Substrates through Selective Laser Melting (SLM) for Power Electronics. 2016

## Substrate technologies - Organic

- Printed Circuit Board (PCB)

- Organic materials  $\rightarrow$  FR4, Polyimide, Epoxide, Teflon, etc.

- Metallization  $\rightarrow$  Cu

- Less expensive than ceramic substrates

|                                                 | Standard<br>FR4 | Polyimide               | ВТ-Ероху   | СЕ-Ероху          | Teflon<br>(PTFE)  |

|-------------------------------------------------|-----------------|-------------------------|------------|-------------------|-------------------|

| Glass transition temperature in °C              | 125 – 140       | 25 – 140 220 – 260 ~ 20 |            | ~ 250             | 200 – 230         |

| CTE in ppm/K                                    | < 70            | < 55                    | < 40       | < 25              | < 70              |

| Dielectric constant<br>1 MHz<br>1 GHz<br>10 GHz | 4.7<br>4.3<br>- | 4.0<br>3.8<br>3.8       | 4.4<br>4.1 | 3.9<br>3.7<br>3.5 | 2.6<br>2.4<br>2.2 |

| Dielectric strength in kV/mm                    | 50              | 45                      | 70         | 65                | 45                |

| Copper adhesion in N/mm                         | 1.5             | 1.0                     | 1.6        | 1.6               | 1.3               |

| Cost comparison<br>with standard FR4            | 1.0             | ~ 3 – 5                 | ~ 2.5      | ~ 2.5             | ~ 4 - 8           |

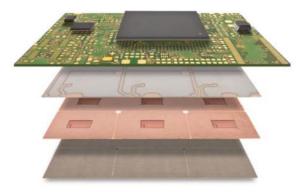

## Substrate technologies - Organic

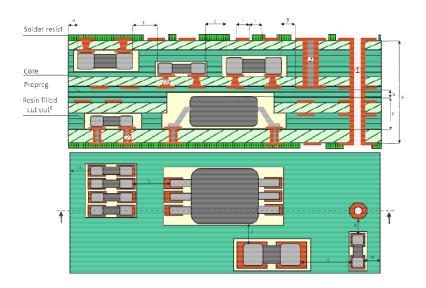

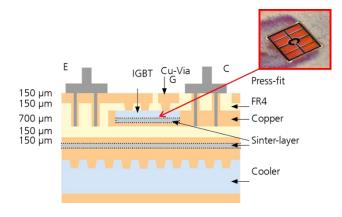

- Printed Circuit Board (PCB) Embedding

- Semiconductor embedded in multilayer PCBs with vias

- Metallization  $\rightarrow$  Cu

- Flexible 3-D designs

Smart p<sup>2</sup> Pack layup SCHWEIZER ELECTRONIC: PCBs - Products and Solutions, 2015

ILFA Feinstleiter Technologie: Embedding Datasheet., 2020

### Substrate technologies - Organic

#### High temperature PCB

- For applications at 175 °C or higher

- PCB material temperature resistant up to ~ 220 °C

| *Differential scanning calorimetry<br>**Dynamic mechanical analysis | Isola B | Benzo       |

|---------------------------------------------------------------------|---------|-------------|

| Resin manufacturer                                                  | Isola   | Huntsman    |

| Polymer basis                                                       | Ероху   | Benzoxazine |

| Halogen-free                                                        | yes     | yes         |

| T <sub>g</sub> (DSC)* in °C                                         | ~ 175   | ~ 200       |

| T <sub>g</sub> (DMA)** in °C                                        | ~ 195   | ~ 220       |

| CTE-z (below T <sub>g</sub> )<br>in ppm/K                           | 40      | 38          |

| Soldering bath at 288 °C<br>(with Cu) in min                        | > 10    | > 10        |

| Thermal conductivity<br>in W/mK                                     | 0.7     | 0.7         |

| Copper adhesion<br>(35 µm/HTG) in N/mm                              | ≥ 1.4   | ≥ 1.4       |

TROEGER, K. et al.: Tailored Benzoxazines as Novel Resin Systems for Printed Circuit Boards in High Temperature E-mobility Applications, 2014

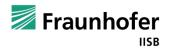

### Substrate technologies - Organic

- Flexible printed circuit boards

- Suitable for compact, complex, space/weight minimizing superstructures

- Base film  $\rightarrow$  Polyimid, PET, PEN

- Metallization  $\rightarrow$  Cu / Ag / Au

https://ats.net/de/produkte-technologien/produkt-portfolio/flexible-starr-flexible-leiterplatten/flexible-leiterplatten/

Dr. Christoph F. Bayer et al., Packaging and Modules Departement DEVICES AND RELIABILITY © Fraunhofer IISB

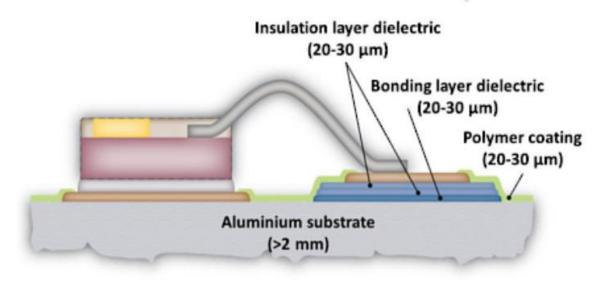

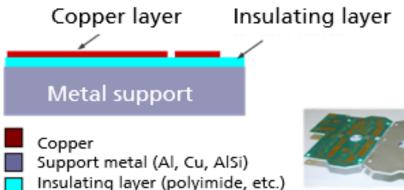

## Substrate technologies - Organic

- Insulated Metal Substrate (IMS)

- Organic materials  $\rightarrow$  see PCB

- Less expensive than ceramic substrates

- Base material Al / Cu / stainless steel

Bildquelle: aurel s.p.a.

Bildquelle: Schweizer AG

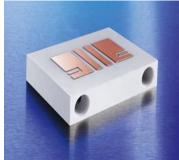

### Substrate technologies - Metallic

#### Copper leadframe

- Cost-effective (Cu as carrier material)

- No substrate-internal CTE mismatch (substrate made of Cu only) → good for substrate lifetime

- But high CTE mismatch to bare dies

- Very high flexibility in terms of design

https://www.zestron.com/de/anwendungen/leistungselektronik/reinigung-von-leadframes.html

## **Comparison and Evaluation of packaging methods**

### Substrate Technologies - Summary

|                                         | Special features                                                                           | Service life or TWB<br>strength                                                                        | Current carrying<br>capacity                               | Steps in<br>metallization                                                | Thermal conductivity<br>in W/mK    | Dielectric strength in<br>kV/mm    | Temperature<br>resistance                     |      |

|-----------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------|------------------------------------|-----------------------------------------------|------|

| LTCC                                    | Good electrical<br>conductivity; through-<br>connection possible;<br>expensive             | Adapted to Si                                                                                          | Medium, max. layer<br>thickness 0.2 mm                     | Not possible, but not<br>absolutely necessary,<br>due to layer structure | absolutely necessary,              | 2.8 – 5                            | 20 - 40                                       | Good |

| нтсс                                    | Mechanical stability;<br>through-connection<br>possible                                    | Adapted to overall structure                                                                           | Bad, because electrical conductivity is poor               |                                                                          |                                    |                                    | 13 – 25<br>(Al2O3)<br>140 – 200<br>(AlN)      | > 22 |

| DCB/ AMB Al <sub>2</sub> O <sub>3</sub> |                                                                                            | medium                                                                                                 |                                                            | Possible, but step                                                       | 15 - 30                            | 15 – 17                            |                                               |      |

| DCB/ AMB AIN                            | Different metallizations<br>possible; distance<br>between conductor                        | Poor passive TC, thick<br>AIN necessary                                                                | Good                                                       | height limited                                                           | height limited                     | 180 – 220                          | > 20                                          | Good |

| DCB/ AMB Si <sub>3</sub> N <sub>4</sub> | tracks is larger than on printed circuit boards                                            | Very good passive TW                                                                                   | Very good, thick<br>copper layers                          | Possible, due to<br>experience based large<br>tolerances                 | 15 - 85                            | ~ 20                               | Good                                          |      |

| SCT/ Thick-film                         | Different ceramics & metallization possible                                                | Passive TW very good,<br>possibly CTE smaller<br>compared to A <sub>I2</sub> O <sub>3</sub><br>DCB/AMB | Cu-paste, electrical<br>conductivity 50% of<br>bulk copper | possible                                                                 | 20 – 30                            | 10 – 20                            | Good                                          |      |

| Copper lead-frame                       | No CTE mismatch, low<br>cost                                                               | High CTE                                                                                               | Good, depending on<br>the thickness                        | possible                                                                 | 30 – 380                           |                                    | Good                                          |      |

| Flex printed circuit<br>board           | Flexible design possible<br>Through-connection<br>possible                                 | Not suitable for high<br>temperature, high CTE                                                         | Good                                                       | Not possible, but not<br>absolutely necessary,<br>due to layer structure | 1.3 – 2.2 depending<br>on material | 120 – 150 depending<br>on material | Up to approx. 210 °C<br>depending on material |      |

| IMS                                     | Mechanical stability,<br>Structure is like printed<br>circuit board; Rth<br>worse than DCB | Not suitable for high<br>temperature, high CTE                                                         | Good                                                       | Not known                                                                | 0.4 - 12                           | 60<br>depending on<br>dielectrics  | Not known                                     |      |

## Comparison and evaluation of packaging methods Substrate technologies - comparison of thermal stability

## Packaging Technologies in Power Electronic Modules

Packaging and interconnection technologies for power electronics

Comparison and evaluation of packaging methods

#### Packaging concepts

- Interconnection technologies

- Packaging at Fraunhofer IISB

- Thermal design and insulation coordination

- Simulation process and theoretical consideration

- Test procedure and analysis

- General

- AQG 324 (LV 324)

- Test setups and parameters

- Summary

Slide 33

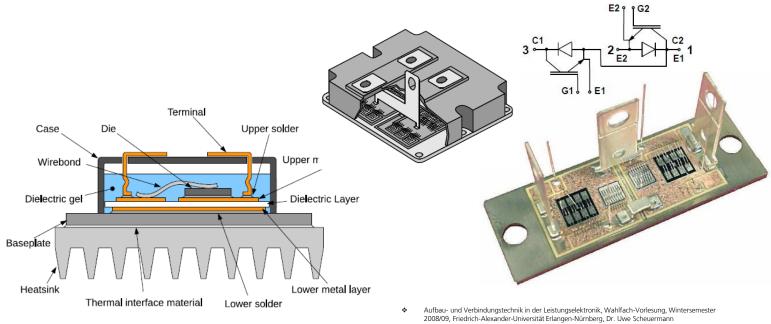

## Packaging and interconnection technologies for power electronics Packaging concepts

Slide 34

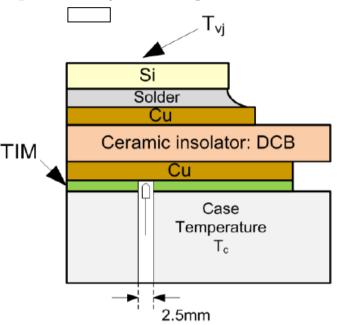

### Packaging concepts

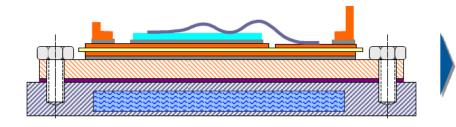

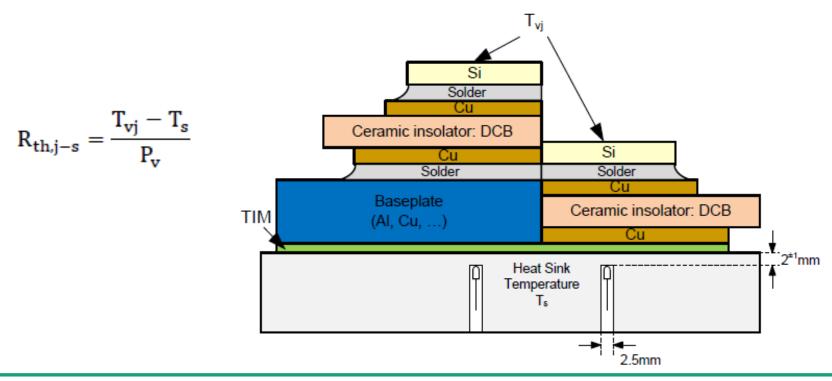

#### Single-sided cooled power modules - basic concepts

#### Indirect cooling

- Module (with or without base plate) on heat sink

- The mechanical separation point also represents a significant thermal barrier with thermal interface material (TIM)

- CTE's of a wide range of materials must be matched

- Error prone (TIM) and expensive assembly

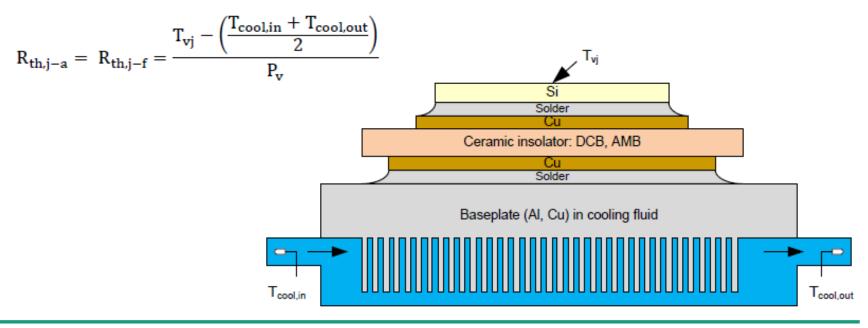

#### **Directly cooled base plate**

- Low thermal resistance

- CTE's of a variety of materials are have to be • matched to each other

- Seal required

#### **Directly cooled substrate**

- Smallest number of interfaces and materials

- Low thermal resistance e.g. by means of turbulence bodies in the cooling oil channel (see ShowerPower<sup>™</sup>)

- Low heat capacity in case of coolant flow disturbances (e.g. air bubbles)

- Seal required

Packaging concepts – assembly standard

Standard assembly

Packaging for Power Electronics, Laboratoire Ampère, Lyon, France, 2015, Cyril BUTTAY

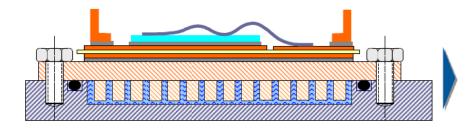

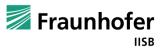

## Packaging concepts

#### Double-sided cooled power modules - Basic concepts

### Packaging concepts

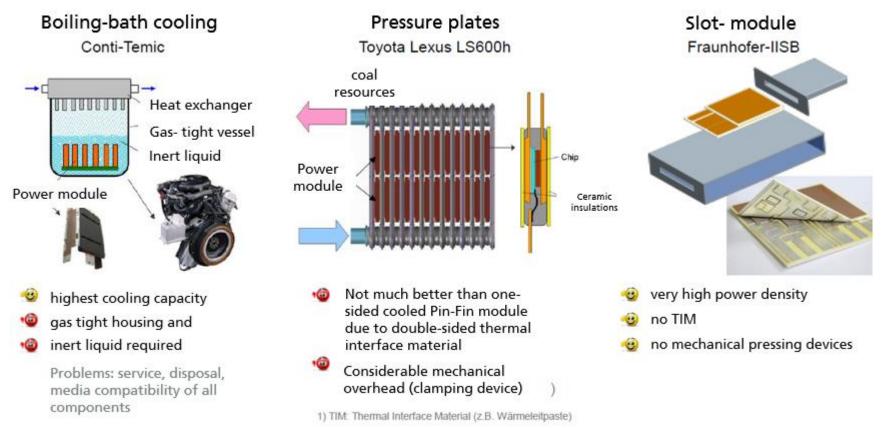

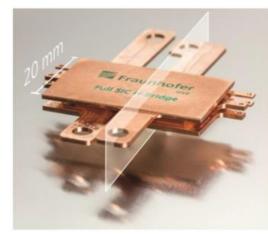

#### **Double-Sided Ceramic Substrate Technology**

- Sandwich concept, chips connected on both sides with DCBs and base plate

- Requires extra insulation layer on the heat sink

- Challenge regarding layout design and production process

- Better power distribution

- High thermal conductivity,  $R_{th}$  up to -50 %

- Low inductive, short switching times

- Reduction of volume and weight

- Stackable cooling concept

- Highest integration and power density

### Packaging concepts

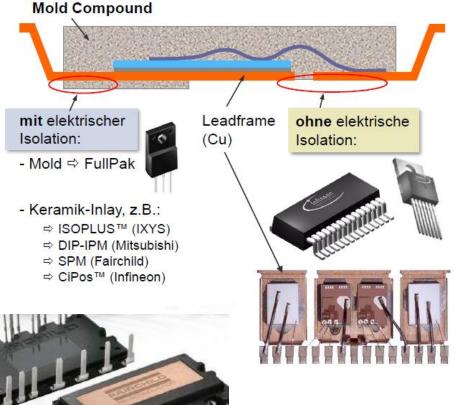

- Leadframe-Molded Module

- Overmoulded stamped grid structure as circuit carrier

- Mold mass or ceramic inlay as electrical insulation

- Very cost-effective, high volume production

- High protective effect (dirt, mechanical stress, etc.)

Infineon, Fairchild, STM

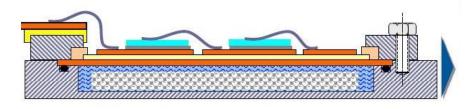

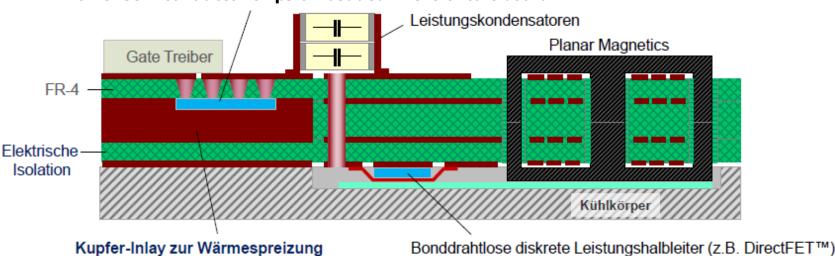

#### Packaging concepts

- Embedding Technology

- Chips embedded in insulating substrates

- Miniaturization  $\rightarrow$  Elimination of bonding wires and housings

- Low inductive designs  $\rightarrow$  short current paths, electrical vias, 3D integration

- Double-sided cooling, thermal vias  $\rightarrow$  up to 60 % R<sub>th</sub> improvement for double-sided liquid-cooled embedded packages

#### Power semiconductor chips embedded in the circuit board

#### Slide 40

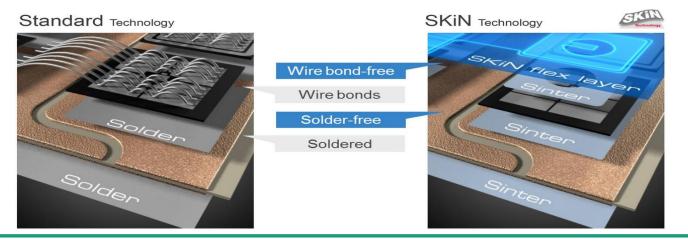

#### Packaging concepts

- SKiN Module (SEMIKRON International GmbH)

- Use of flexible conductor foils

- R<sub>th</sub> reduction compared to classic power modules

- Elimination of solder layers and bonding wires

- Increased service life by factor ~200 compared to classic power modules

- Lifetime increase by factor ~40 compared to state-of-the-art industrial power modules

- Reduction of volume and weight (to ~ 40 % of classic power modules)

#### Packaging concepts

#### Further packaging concepts and products

- Toshiba TPW1R306PL; 5.0 mm × 6.0 mm × 0.73 mm; MOSFET; 60 V 260 A; 2015/2017 http://www.powerelectronicsworld.net/article/0/101041-toshiba-addsdouble-sided-cooling-to-60-v-power-mosfets.html

- Infineon HybridPACK<sup>™</sup> DSC; 42 mm x 42.4 mm x 4.77 mm; IGBT; 700 V 200/400 A; 15 nH; 0.1 K/W (0.12 K/W HybridPACK 1); PCIM 2016 http://www.infineon.com/cms/de/about-infineon/press/marketnews/2016/INFATV201605-056.html

- International Rectifier/Infineon COOLiR<sup>2</sup>Module™; 50 mm x 45 mm x 7 mm; IGBT; 680 V 300 A; <15 nH; down to 50 % R<sub>th</sub>; Bodo's Power Systems 2012

http://www.powerguru.org/coolir2%E2%84%A2-high-powersemiconductor-platform/

- Hitachi DCPM Double-sided-cooling Full-SiC Power Module; Tokyo Motor Show 2015 http://www.hitachi.com/New/cnews/month/2015/09/150928a.html

- Fuji LS600h Lexus power module; 47.9 mm x 38.1 mm x 5.3 mm; vol. 54 no 2 fuji electric review 2008 or Oak Ridge National Laboratory 2009

### Packaging Technologies in Power Electronic Modules

Packaging and interconnection technologies for power electronics

- Comparison and evaluation of packaging methods

- Packaging concepts

- Interconnection technologies

- Packaging at Fraunhofer IISB

- Thermal design and insulation coordination

- Simulation process and theoretical consideration

- Test procedure and analysis

- General

- AQG 324 (LV 324)

- Test setups and parameters

- Summary

Slide 43

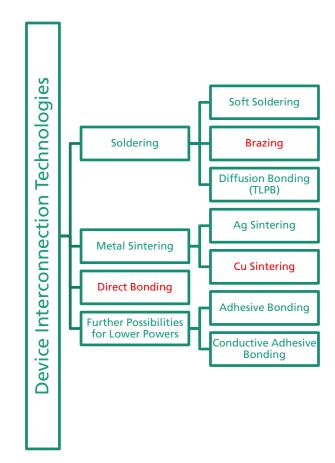

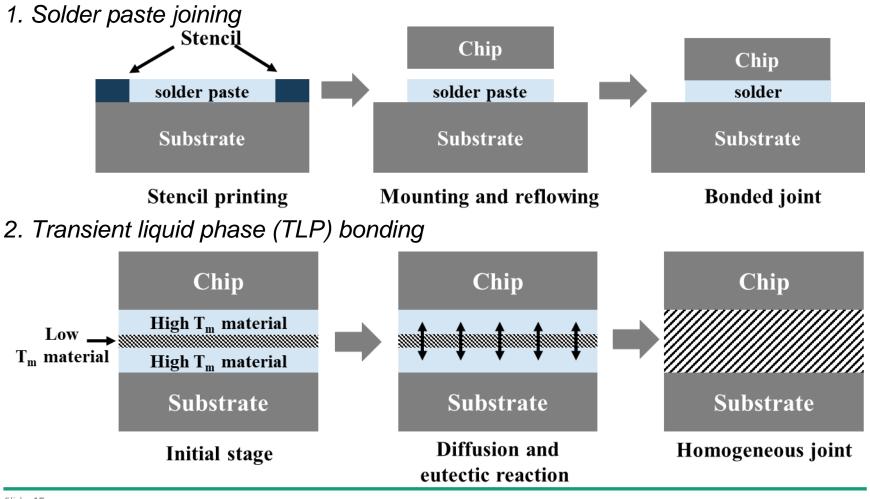

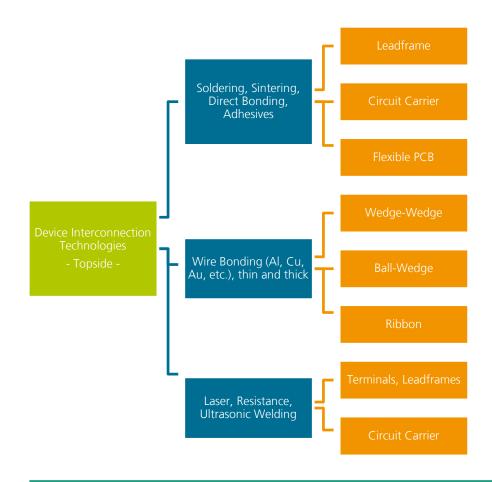

#### Interconnection technologies

- Besides everlasting interest in further integration, minimization, modularization, high temperature and high voltage capability, new materials such as wide bandgap semiconductors come up and find their way into recent application. Thus it appears that SiC semiconductor devices are now used in power electronics mainly for switching high electrical currents (up to several 100 A) and high voltages (≥ 1 kV) in automotive drives, energy transmission and traction applications.

- Possible device interconnection technologies in power electronics packaging (red: research topics)

#### Interconnection technologies

#### Interconnection technologies

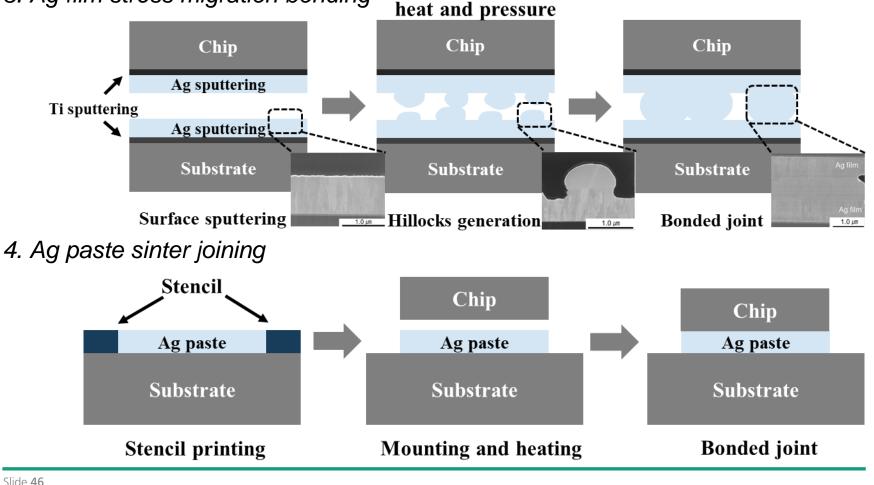

3. Ag film stress migration bonding

#### Interconnection technologies

#### A comparison of different bonding materials

| Series                         | Processing<br>Temperature<br>in ºC | Maximal<br>Temperature<br>in ºC | Electrical<br>Resistivity<br>in mΩ·cm | Thermal<br>Conductivity<br>in W/m⋅K | Bonding quality |

|--------------------------------|------------------------------------|---------------------------------|---------------------------------------|-------------------------------------|-----------------|

| Ag paste                       | 200~250                            | Up to 900                       | ≤ 0.005                               | ≥ 200                               | High            |

| Conductive<br>adhesive         | 120~175                            | 250                             | ~7 <sup>[1]</sup>                     | ~ 3 – 10                            | Low             |

| High-<br>temperature<br>solder | 50 ⁰C above<br>Tm                  | 50 °C below<br>Tm               | ~15 <sup>[2]</sup>                    | ≤ 100                               | High            |

|                                | Before sinterin                    | ng Below<br>250 °C              |                                       | After sintering                     |                 |

nm x5 00k SE(U)

Ag particles and solvent

Micron-porous Ag structure

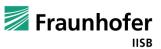

#### Interconnection technologies

- Overview of soldering technology for power modules

- Selection of solder materials for power electronics applications

| Solder<br>composition  | T <sub>Liquidus</sub> in °C | Electrical<br>Conductivity<br>in m/Ωmm <sup>2</sup> | Thermal<br>Conductivity<br>in W/mK | CTE in<br>ppm/K |

|------------------------|-----------------------------|-----------------------------------------------------|------------------------------------|-----------------|

| BiPb(32)Sn(15.5)       | 95                          | 1.5                                                 |                                    | 16.6            |

| BiSn(43)               | 139                         |                                                     | 19                                 |                 |

| InPb(50)               | 215                         | 3.3                                                 | 22                                 | 24.4            |

| SnPb(37)               | 183                         | 7.4                                                 | 70                                 | 24.3            |

| SnAg(3.5)Cu(0.9)       | 217                         |                                                     | 60                                 |                 |

| SnCu(1)                | 227                         | 8.8                                                 | 60                                 |                 |

| Sn(96.5)Ag(3.0)Cu(0.5) | 217/221                     |                                                     |                                    |                 |

| Sn(96.5)Ag(3.5)        | 221                         |                                                     |                                    |                 |

| Sn(95)Ag(5)            | 221/245                     |                                                     |                                    |                 |

| Sn(99.3)Cu(0.7)        | 227                         |                                                     |                                    |                 |

| Sn(97)Cu(3)            | 227/300                     |                                                     |                                    |                 |

| Sn(100)                | 232                         |                                                     |                                    |                 |

| Pbln(19)               | 276                         |                                                     |                                    |                 |

| PbSn(5)Ag(2.5)         | 280                         | < 5                                                 | 44                                 | 29              |

| PbSn(5)                | 315                         | < 5                                                 | 45                                 | 29              |

| PbSn(2)                | 325                         | 4.9                                                 |                                    |                 |

| Pb(100)                | 327                         |                                                     | 37                                 | 29.3            |

| AuSn(20)               | 280                         | < 5                                                 | 46                                 | 16              |

| AuGe(12)               | 356                         | 7                                                   | 34                                 | 13.4            |

| AuSi(3)                | 363                         | 25                                                  | 26                                 |                 |

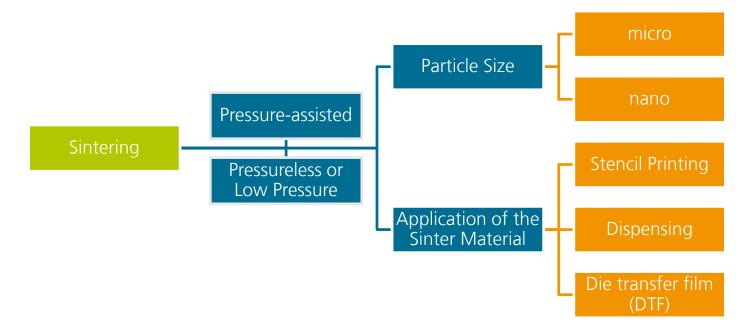

#### Interconnection technologies

Variety of metal sintering technology for die attach, e.g. mainly silver but also copper or copper-silver sinter paste

#### Interconnection technologies

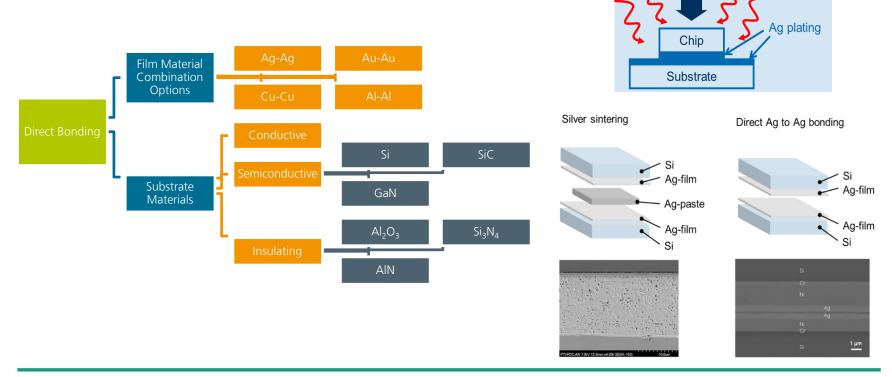

Direct bonding examples in power electronics – substrate materials rank as carriers of the needed metallization

Pressure

#### Slide 50

Dr. Christoph F. Bayer et al., Packaging and Modules Departement DEVICES AND RELIABILITY © Fraunhofer IISB Heat

#### Interconnection technologies

Dr. Christoph F. Bayer et al., Packaging and Modules Departement DEVICES AND RELIABILITY © Fraunhofer IISB

### Packaging Technologies in Power Electronic Modules

Packaging and interconnection technologies for power electronics

- Comparison and evaluation of packaging methods

- Packaging concepts

- Interconnection technologies

- Packaging at Fraunhofer IISB

- Thermal design and insulation coordination

- Simulation process and theoretical consideration

- Test procedure and analysis

- General

- AQG 324 (LV 324)

- Test setups and parameters

- Summary

Slide 52

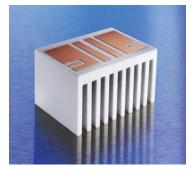

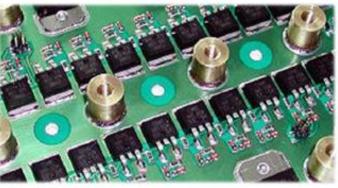

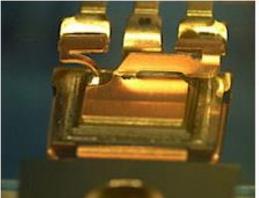

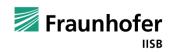

#### Packaging at Fraunhofer IISB

- Fraunhofer IISB concepts from public projects

- Project EMILE (Full SiC Busbar Power Module)

- Double-sided assembly concept by means of Ag-sintering

- Chips on copper bus bar in the smallest space high power density

- Very high switching speed Inductance < 1 nH</p>

- Cooling on both sides possible

- Cost-effective  $\rightarrow$  no ceramic circuit carriers, only copper

Slide 53

#### Packaging at Fraunhofer IISB

- Fraunhofer IISB concepts from public projects

- Project ULTIMO (Double-sided Power Module)

- Chips sintered on both sides in DCBs

- High power density

- Low number of different materials

- Cooling on both sides possible

Dr. Christoph F. Bayer et al., Packaging and Modules Departement DEVICES AND RELIABILITY © Fraunhofer IISB

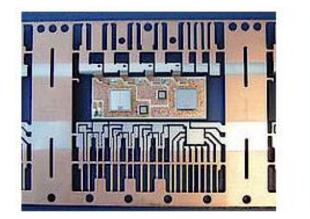

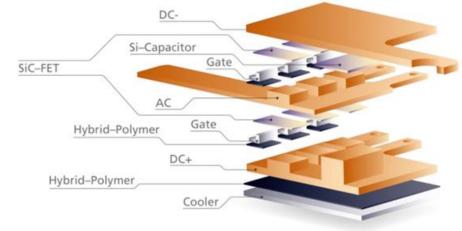

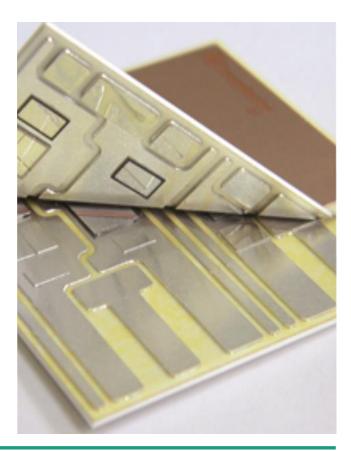

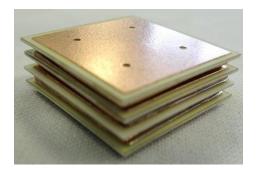

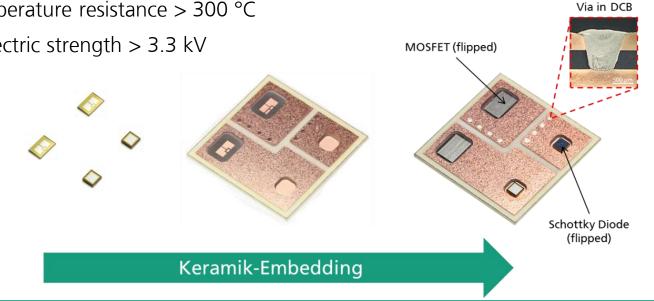

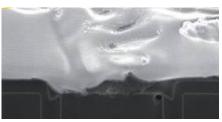

#### Packaging at Fraunhofer IISB

- Fraunhofer IISB concepts from public projects

- Projekt DiaLe (Ceramic/ DCB Embedding)

- WBG components embedded in DCBs

- Multilayer DCB stack realizable

- Flexible generation of vias in DCB

- High temperature resistance > 300 °C

- High dielectric strength > 3.3 kV

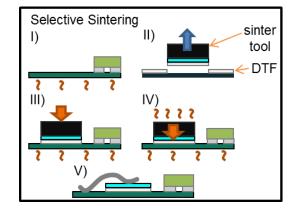

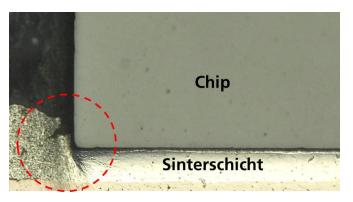

### Packaging at Fraunhofer IISB

- Selective silver sintering

- Sintering of bare dies or SMD components on PCB

- Sintering on leadframe for chip embedding

#### Slide 56

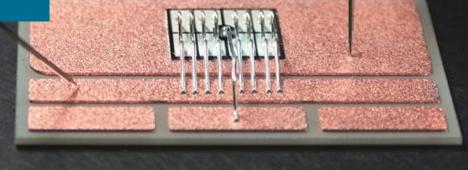

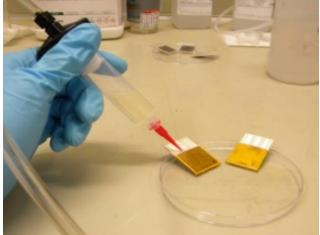

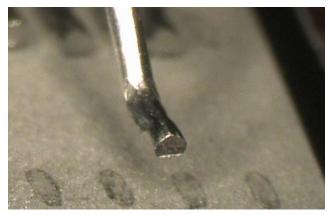

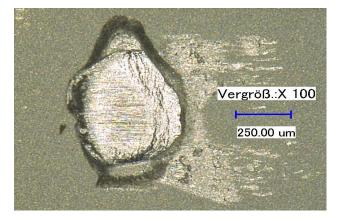

#### Packaging at Fraunhofer IISB

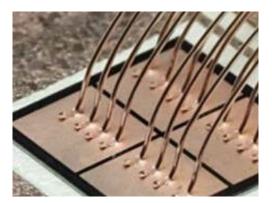

#### Chip metallization and wire bonding

- Bonding wires Al, Cu, AlCuCore, Au...

- Metallization as desired for bonding, soldering, silver sintering, etc...

Dr. Christoph F. Bayer et al., Packaging and Modules Departement DEVICES AND RELIABILITY © Fraunhofer IISB

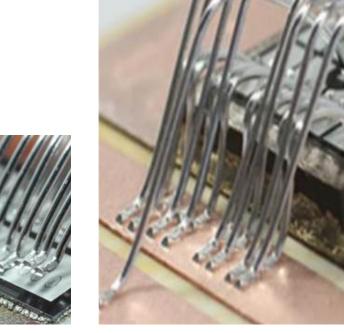

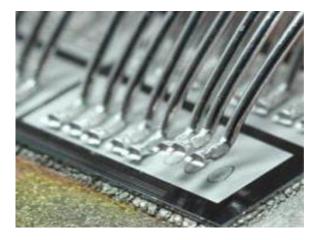

#### Packaging at Fraunhofer IISB

- Top side chip contacting

- Pressureless silver sintering with leadframe

- High current carrying capacity and reliability

#### Packaging at Fraunhofer IISB

- Resistance spot welding of copper terminals on DCB

- Cu-Cu bonding

- No intermediate / connection layer

- Low thermomechanical stress formation during the process

- High reliability

### Packaging Technologies in Power Electronic Modules

Packaging and interconnection technologies for power electronics

- Comparison and evaluation of packaging methods

- Packaging concepts

- Interconnection technologies

- Packaging at Fraunhofer IISB

- Thermal design and insulation coordination

- Simulation process and theoretical consideration

- Test procedure and analysis

- General

- AQG 324 (LV 324)

- Test setups and parameters

- Summary

Slide 60

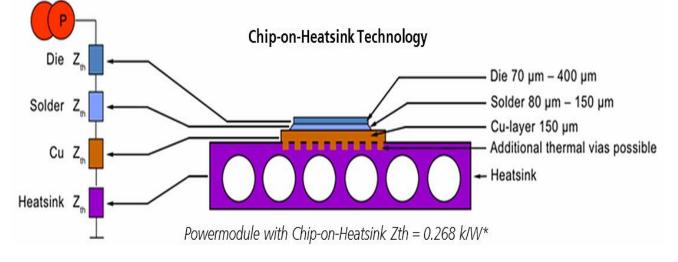

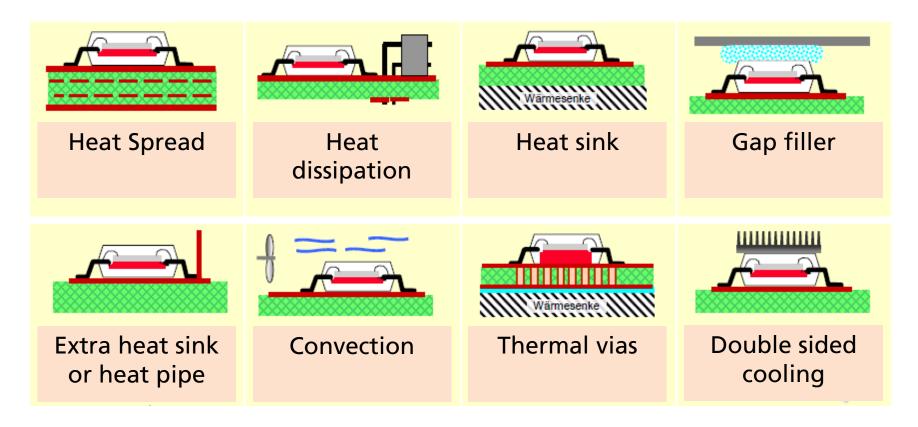

#### Thermal design

#### Thermal optimization possibilities of the assembly technology

### Insulation coordination - principles, terms and standards

- Aim of the insulation coordination

- Prevention of hazards to people and malfunctions in electrical equipment during its entire service life in the intended environment

- Sparkover of airgap

- Leakage currents on insulating material surfaces

- Breakdowns of solid insulating materials

- Procedure

- Dimensioning of insulating sections to the voltage stress, which is expected during operation

- Standards for insulation coordination for minimum values

### Insulation coordination - principles, terms and standards

#### **European Standards**

### Basic standards EN 61140 / protection against electric shock

- Field of application  $\rightarrow$  Electrical installations, systems and equipment without limitation of voltage, current, type of current and for frequencies up to 1 kHz

- Product family standards EN 60664-... / Insulation coordination for electrical equipment in low voltage systems

- Application range  $\rightarrow$  Up to 1000 V AC with rated frequencies up to 30 kHz and 1500 V DC up to an operating altitude of 2000 m above sea level

- Product standards EN 61800-... / Variable-speed electrical drives

- Field of application  $\rightarrow$  Excluded are railway drives and electric vehicle drives

### Insulation coordination - principles, terms and standards

- Air gap

- Shortest distance in air between two conductive parts

- Creepage distance

- Shortest distance along the surface of an insulating material between two conductive parts

- A creepage distance must not be smaller than the associated clearance

- The smallest possible creepage distance is at least as large as the associated clearance

#### Insulation coordination - principles, terms and standards

- Further remarks on insulation coordination

- > The determination of clearance and creepage distances requires not only knowledge of the standards but also a great deal of knowledge of circuit technology, the function and the operating conditions of the equipment

- $\succ$  With complex circuit boards or substrates, the dimensioning of the clearance and creepage distances can be a very confusing and tedious challenge

- Software support is a good facilitation for the control of clearance and creepage distances

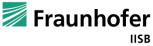

Insulation concepts

|     |                                                                         | Silikone                                           |                                                    |                                                    |                   |  |

|-----|-------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|-------------------|--|

| CC  | Potting examples                                                        | gel                                                |                                                    | Polyimide                                          | PEEK              |  |

|     | Dielectric strength in kV/mm                                            | 14 25                                              | 18 45                                              | 22 25                                              | 20                |  |

| ic  | Electric conductivity $\sigma$ in ( $\Omega$ m) <sup>-1</sup>           | 10 <sup>-13</sup> 10 <sup>-</sup><br><sup>14</sup> | 10 <sup>-13</sup> 10 <sup>-</sup><br><sup>14</sup> | 10 <sup>-12</sup> 10 <sup>-</sup><br><sup>13</sup> | 10 <sup>-14</sup> |  |

| de  | Relative permittivity $\boldsymbol{\varepsilon}_r$                      | 2,73,0                                             | 3,3 7,2                                            | 2,8 3,6                                            | 3,2               |  |

|     | CTE in 10 <sup>-6</sup> K <sup>-1</sup>                                 | 290 400                                            | 40 170                                             | 54                                                 | 50                |  |

| e   | Flexural strength in MPa                                                |                                                    | 55 125                                             | 116                                                |                   |  |

|     | Modulus of elasticity in Gpa                                            |                                                    | 1,1 5,0                                            | 3,3                                                | 3,0               |  |

| nic | Thermal conductivity $\lambda$ in W m <sup>-</sup> $^1$ K <sup>-1</sup> | 0,20 1,10                                          | 0,48 2,1                                           | 0,35                                               | 0,25              |  |

|     | Operating temperature in °C                                             | <260                                               | <240                                               | <300                                               | <260              |  |

#### Slide 66

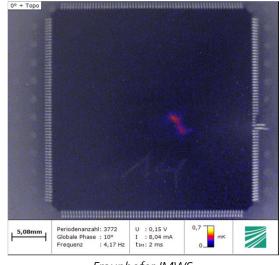

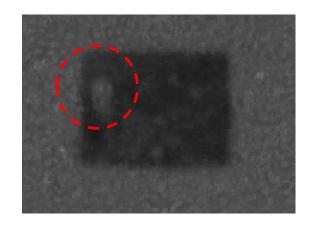

Insulation concepts – risk of corrosion

Electrochemical Migration ECM - clip (https://www.iisb.fraunhofer.de/en/research\_areas/packaging\_reliability/corrosion.html)

## Thank you for your attention!

New Concepts and Materials for Packaging

High Performance Joining Technologies, Sintering

Thermal, Electrical, and Mechanical Characterization

Lifetime Characterization, Statistical Analysis

Analysis of Failure Mechanism

Lifetime Modeling

Slide 68

### Packaging Technologies in Power Electronic Modules

Packaging and interconnection technologies for power electronics

- Comparison and evaluation of packaging methods

- Packaging concepts

- Interconnection technologies

- Packaging at Fraunhofer IISB

- Thermal design and insulation coordination

- Simulation process and theoretical consideration

- Test procedure and analysis

- General

- AQG 324 (LV 324)

- Test setups and parameters

- Summary

Slide 69

## Simulation methods and theoretical consideration *Fundamentals of simulation*

### What is simulation?

"The simulation or simulation is...

...a procedure for the analysis of systems that are too complex for theoretical or formulaic treatment. In simulation, experiments are carried out on a model to gain knowledge about the real system. The procedure of the simulator with concrete values (parameterization) is called simulation experiment. Its results can then be interpreted and transferred to the system to be simulated."

### Simulation methods and theoretical consideration Fundamentals of simulation

### Expectations

- Building understanding of the problem and the materials involved

- Extension of the understanding of the effects of physical processes and behavioral prediction

- Reduction of development time, development costs and production costs, saving of material, reduction of test series

- Early detection of weak points, failure prediction

- Quality improvement and optimization of the construction

- Flexible adaptation to subsequent constructions

- Further training

- And much more...

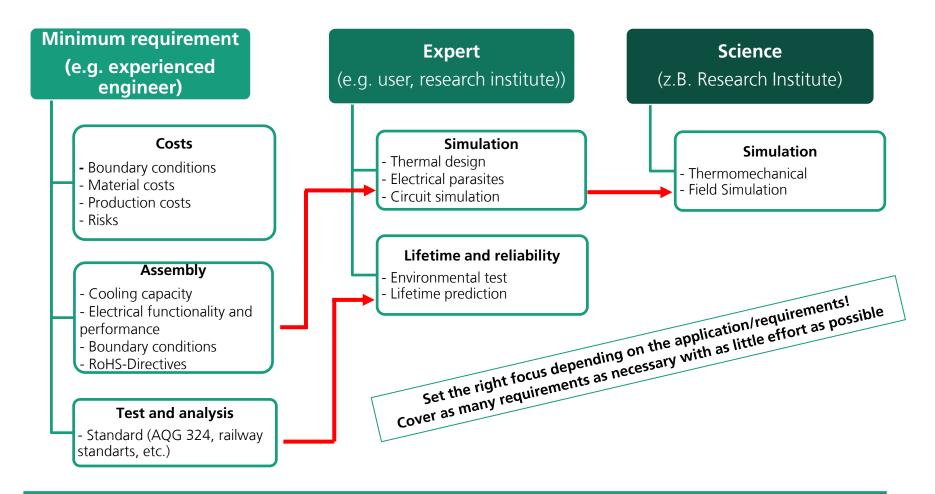

## Simulation methods and theoretical consideration *Fundamentals of simulation*

### Requirements

- Modelling understanding (experiment  $\rightarrow$  calculation model)

- FEM theory: Knowledge of the basics

- Training period for the software

- Powerful and problem specific software (ABAQUS, COMSOL, PLM, CST, ANSYS, JMAG, ISAFEM, MECHANICA, NASTRAN, PERMAS, CD-Adapco, FEMM, OpenFOAM, Keysight ADS, 6SigmaET, and many more)

- Powerful hardware (PC, Workstation, Mainframe, Cluster, Cloud)

- Expert or engineering knowledge for critical evaluation of the results

### Simulation methods and theoretical consideration Fundamentals of simulation

### Simulation possibilities

- Static and dynamic strength calculations, electrical, electromagnetic, magnetic, thermal, mechanical, thermomechanical, vibration mechanics problems

- Chemical and physical reactions, separation or combustion processes

- Vibration analysis on electrical machines, stresses and deformations (elastic and plastic, e.g. virtual crash tests using finite element methods), flow simulation

- Semiconductor devices, heat conduction processes, optical systems, fusion reactors, accelerators and nuclear reactions, doping and diffusion, electromigration

- Electrical properties, circuit simulations

- Couplings, reductions, optimizations, and much more...

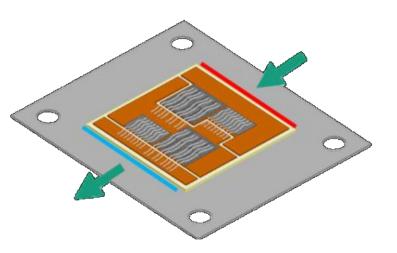

## Simulation methods and theoretical consideration *Parasites in power module*

### Physical basics

$$\Phi_j = \sum_i \frac{q_i}{4\pi\varepsilon \left| \vec{r_i} - \vec{r_j} \right|}$$

- Calculation of internal and coupling capacities in FEM

- Calculation of the charge distributions in conductors and the induced charge distributions on the surface of dielectrics

- Ratio of voltage to charge gives the capacity  $C = \frac{Q}{U}$

- Calculation of inductances and resistances

- DC: Calculation of current distribution (FEM) and vector potential (FMM) Inductance and resistance

- AC: All currents are considered as surface currents (BEM), but are corrected with a skin effect correction factor depending on frequency (magnetic field distribution, current distribution and vector potential result in inductance and resistance)

#### Physical basics

FEM versus BEM (e.g., here Ansys Maxwell versus Ansys Q3D)

| Ansys Maxwell (FEM)                                                                                                                                | Ansys Q3D (BEM)                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - Berechnung der Umgebung/ Plenum<br>benötigt<br>- Felddarstellungen in dem umgebenden<br>Material möglich<br>- Künstliche Randbedingungen möglich | <ul> <li>Berechnung der stromleitenden<br/>Volumen</li> <li>Stromdichte/ Felder nur in (DC)<br/>oder auf (AC) berechneter Geometrie</li> <li>Ziemlich schnell</li> </ul> |

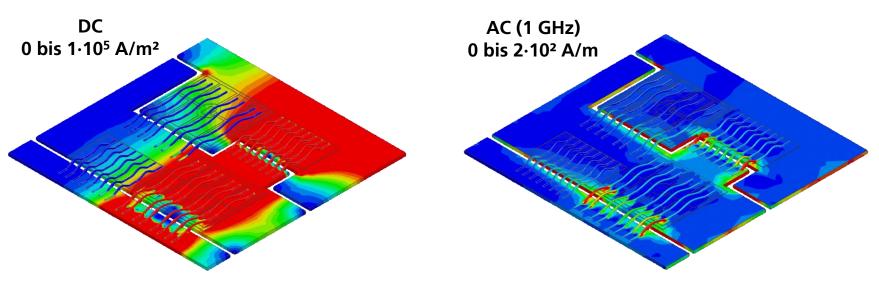

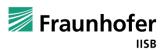

#### What can be simulated?

- Calculation of the own capacities and coupling capacities of the individual conductors → Capacity matrix

- Low-frequency (DC) and high-frequency (AC) inductors and resistors

Inductance matrix

- C, L and R are simulated for different conductor and dielectric arrangements for two-dimensional and three-dimensional problems

- Export of component properties for circuit simulations

- Creation of equivalent circuit diagrams for Maxwell Spice, Berkley Spice, HSPICE, PSPICE, Spreadsheet Format, IBIS Package Model, Ansoft Serenade, Cadence DML, etc.

Parasites in power module

- What can be simulated?

- Frequency dependent current density distribution

Slide 77

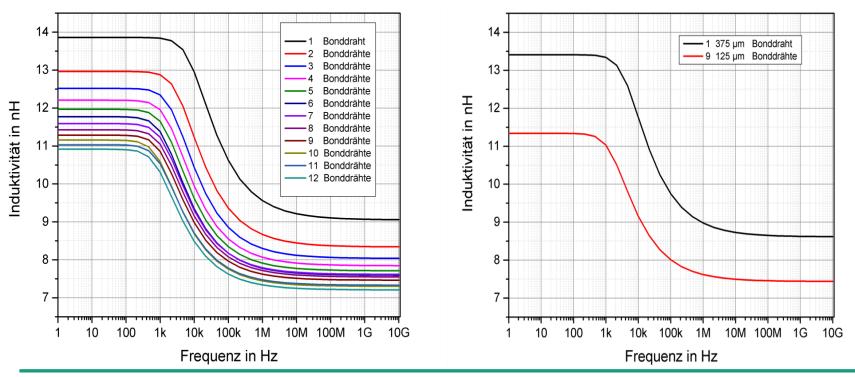

- What can be simulated?

- Frequency dependent inductance

#### What can be simulated?

Example Variation of the number and thickness of bond wires in the power module

#### What can be simulated?

- Capacity and coupling capacitances in pF

- Frequency dependence only with loss factor  $tan(\delta)$  in the dielectric

Slide 80

#### Risks, problems and inaccuracies

- Disregard of the simulation restrictions

- Explicit calculation for 'good' electrically conductive materials only for very low frequencies (DC) and very high frequencies (AC)

- Estimate skin effect for materials used

- Observe distances of conductive components (due to wave propagation HFSS)

- Inaccuracies in networking

- Self-generated short circuits due to 'surface-penetrating' crosslinking

- Insufficient networking or poor aspect ratio

- Checking the current density distribution

#### Physical basics

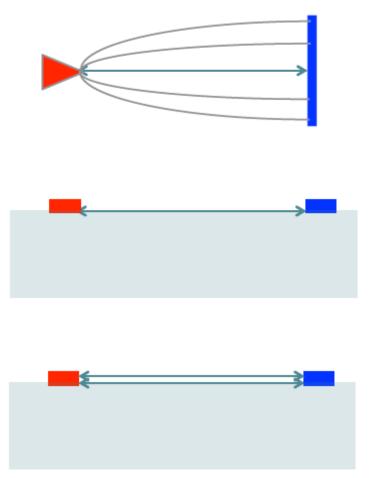

Heat transfer mechanisms

Slide **82**

#### Physical basics

Unsteady/ transient heat conduction

$$> \boldsymbol{\rho} \cdot \boldsymbol{c} \boldsymbol{p} \cdot (\frac{dT}{dt}) + \boldsymbol{\lambda} \cdot \boldsymbol{\nabla}^2 \cdot \mathbf{T} = \mathbf{P}_{\mathbf{V}}$$

Calculation of thermal behaviour in case of overloads/ surge currents

Thermal capacity C<sub>th</sub> of a structure

$$C_{th} = c_{th} \cdot \rho \cdot V$$

$\rho \cdot c_{th}$

|                                  |    | kg′m³ | kJ/kgK | W/mK | 10 <sup>-6</sup> m²/s |

|----------------------------------|----|-------|--------|------|-----------------------|

| Thermal diffusivity $\alpha$     | AI | 2,7   | 0,88   | 237  | 98,8                  |

| $\alpha = \frac{\lambda}{2 + c}$ | Cu | 8,9   | 0,382  | 399  | 117                   |

ρ

α

λ

Cth

### Physical basics

Coupling of a temperature field with structural mechanics

Temperature increase of a material causes a change in length  $\Delta \varepsilon$  or thermal expansion as a function of the thermal expansion coefficient CTE

$$\Delta \varepsilon = CTE \cdot \varepsilon_0 \cdot \Delta T$$

(Thermo-)Mechanical stress 6 as a function of elastic modulus E and thermal strain Δε

Heat dissipation and deformation in power modules

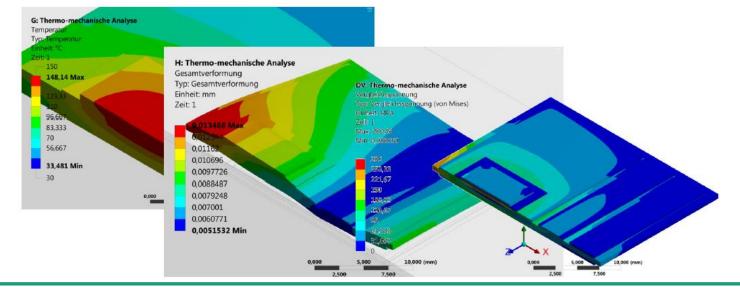

### What can be simulated?

- Temperature distribution (in electronic components)

- Thermal expansion and thermal influence zones

- Calculation of the maximum temperatures of semiconductors and derivation of the thermal resistances of different assembly concepts

- Analysis of heat flows

- Transient temperature distribution

- Cooling curves (Z<sub>th</sub>)

- Accidents/impulse loads

- Thermo-mechanical (stationary/instationary)

- Deformations

- Mechanical stresses and strains (elastic/plastic)

#### Defining boundary conditions

- Obtaining power dissipation

- Heat flow (on surface)

- Heat flux density (on surface)

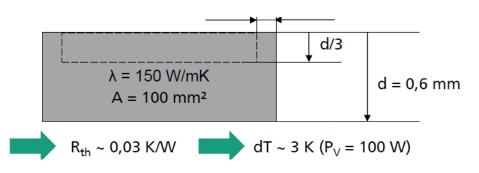

- Internal heat generation (volume) e.g. 150 W Chip volume

- Differentiation active/passive chip area useful for HV chips

#### Defining boundary conditions

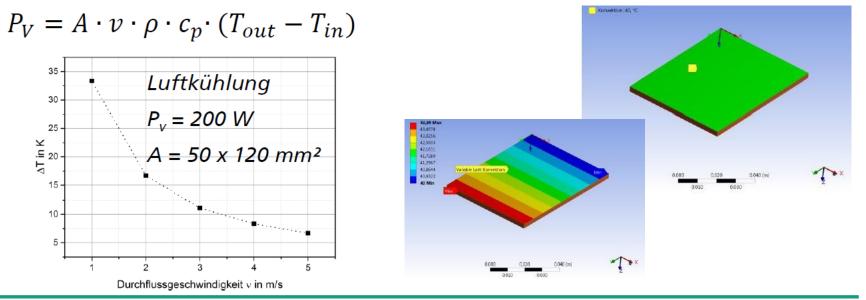

- Assumption of cooling capacities by heat transfer coefficients ( $\alpha$ K)

- Constant coolant temperature

- Variable coolant temperature

Consideration of heat input and inlet/outlet temperature

Slide 87

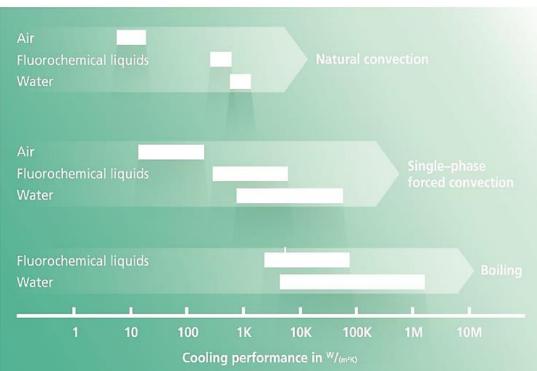

#### **Defining boundary conditions**

- Assumption of cooling capacities through heat transfer coefficients ( $\alpha$ K) versus coolant temperature

- Air cooling

- 5 W/m<sup>2</sup>K (natural horizontal)

- 20 W/m<sup>2</sup>K (natural vertical)

- 500 W/m<sup>2</sup>K (forced, fins)

- Water-cooling

- 5.000 W/m<sup>2</sup>K (4 l/min)

- 20.000 W/m<sup>2</sup>K (12 l/min)

- 2-phase cooling\*

- 80,000 W/m<sup>2</sup>K

\* S. N. Joshi, E. M. Dede; Thermal management of future WBG devices using

two-phase cooling - PCIM 2016

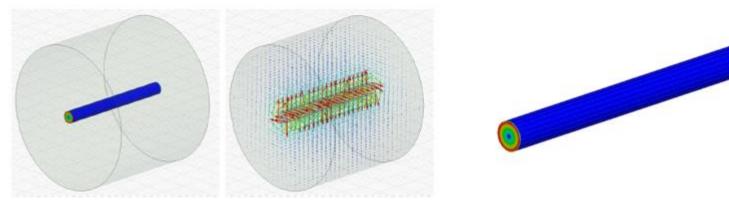

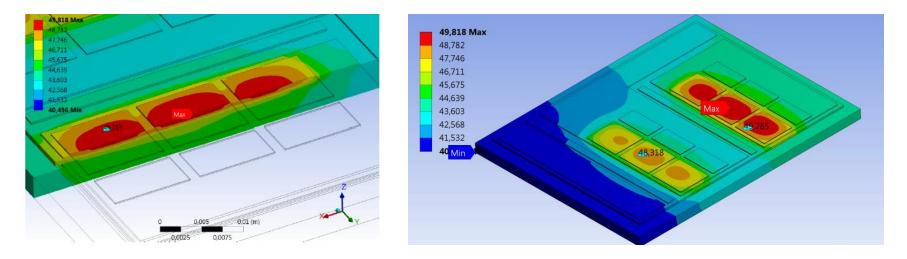

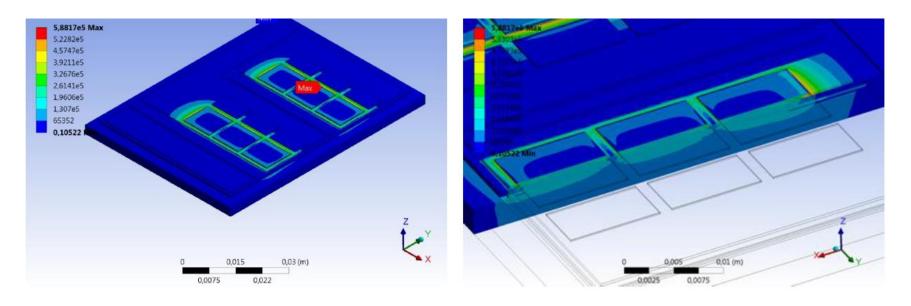

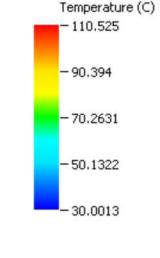

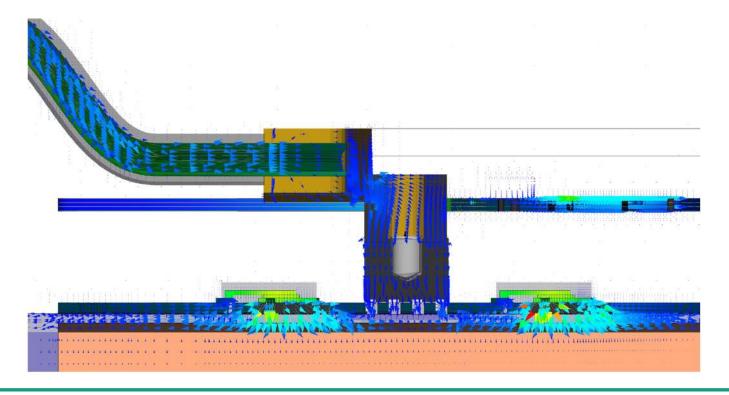

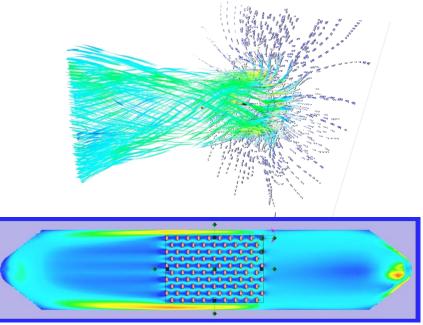

- What can be simulated? (Example in Ansys Workbench)

- Temperature distribution in the power module

- 150 W/chip (internal heat generation)

- $\alpha_{\rm K}$  = 20,000 W/m<sup>2</sup>K against T<sub>min</sub> = 40 °C

#### Slide 89

- What can be simulated? (Example in Ansys Workbench)

- Heat flow

- 150 W/ chip (internal heat generation)

- $\blacksquare \alpha K = 20,000 W/m^2 K against T_{min} = 40 °C$

#### Slide 90

Heat dissipation and deformation in power modules

#### What can be simulated?

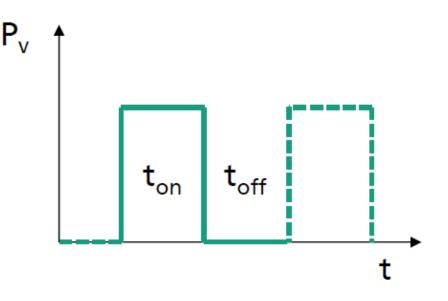

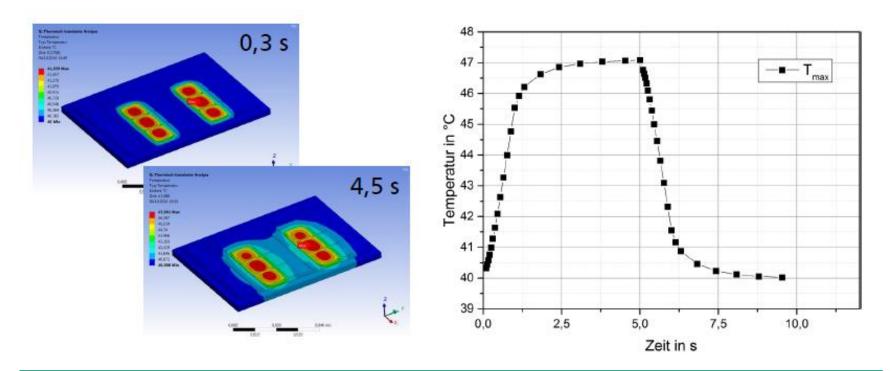

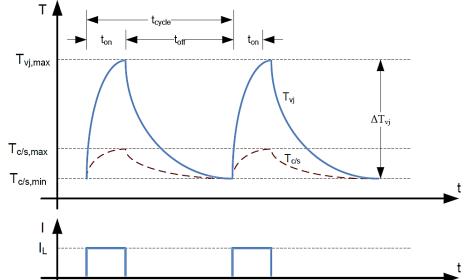

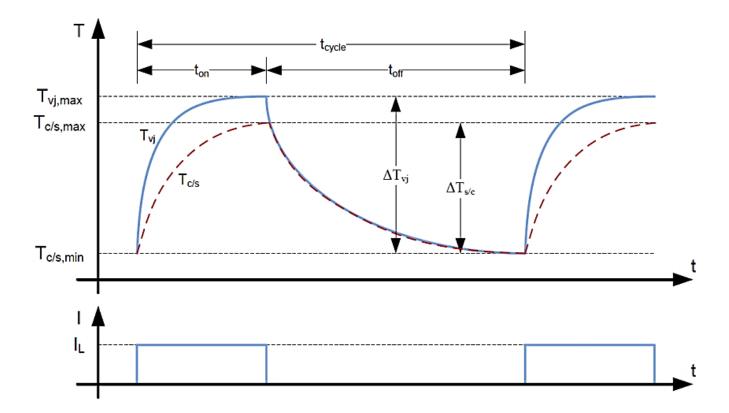

- Transient temperature distribution

- Simulation of a power cycle

- $t_{on}$  /  $t_{off}$  every 5 s

- 150 W/ Chip

- T<sub>min</sub> = 40 °C

- $\mathbf{a}_{\mathrm{K}} = 20 \text{ kW/m}^{2}\text{K}$

- Consider material data

- Spec. thermal capacity

- Density

- Time dependent internal heat generation

- Formula → e.g. sinus function

- Chart  $\rightarrow$  Definition of load steps

#### What can be simulated?

- Transient temperature distribution

- Graphical and chart temperature evaluation as a function of time

#### What can be simulated?

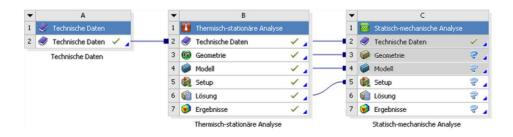

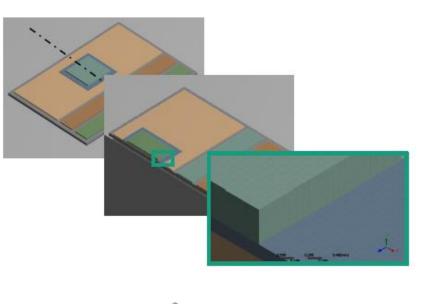

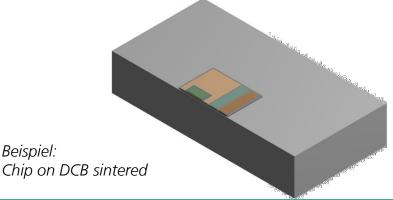

Coupling of a temperature field with structural mechanics

- The thermal simulation results in a change in length of the individual components (deformation), which leads to mechanical tensions/strains

- Contact areas of the individual components influence the stress/strain distribution (example: bond versus frictionless)

- Output temperature and resulting temperature distribution of the bodies serve as input parameters for the mechanical simulation

Beispiel:

#### What can be simulated?

- Static-mechanical analysis

- Temperature field = Imported load

- Bearings

- Model friction-free on base plate

- Base plate fixed

- Gravitational acceleration on geometry

- Technical data

- CTF

- E-Modulus

- What can be simulated?

- Static-mechanical analysis

- CTE- Mismatch of the individual layers leads to

- Deformation of the model

Occurrence of mechanical stresses in the model

#### Slide 95

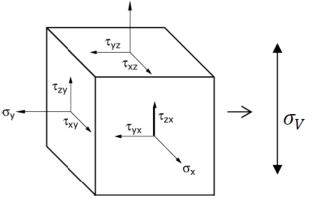

Evaluation

Mises equivalent stress (GEH hypothesis)

The stress tensor

The hypothesis)

$$\begin{bmatrix} \sigma_x & \tau_{xy} & \tau_{xz} \\ \tau_{yx} & \sigma_y & \tau_{yz} \\ \tau_{zx} & \tau_{zy} & \sigma_z \end{bmatrix}$$

with elements of the normal stress  $\sigma i$  and the shear stress  $\tau ij$  can be reduced to a uniaxial stress by means of a comparative stress  $\sigma V \rightarrow$  Comparison with tensile strengths possible

$$\sigma_V = \sqrt{\sigma_x^2 + \sigma_y^2 + \sigma_z^2 - \sigma_x\sigma_y - \sigma_x\sigma_z - \sigma_y\sigma_z + 3(\tau_{xy}^2 + \tau_{xz}^2 + \tau_{yz}^2)}$$

Application for ductile materials  $\rightarrow$  Solder/sinter connections, Cu, etc.

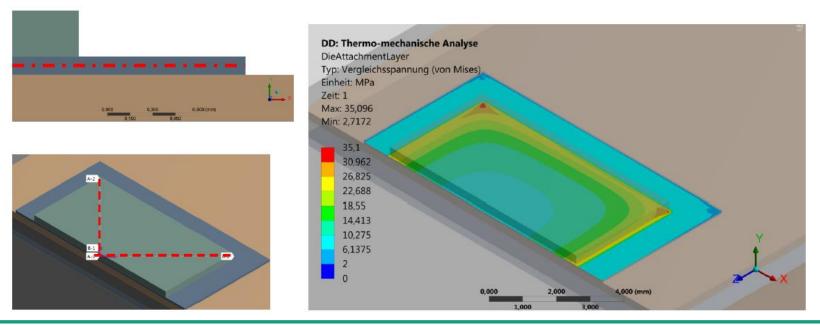

#### Evaluation

- Mechanical stresses in ductile compound layers

- Cutting planes

- Paths

#### Slide 97

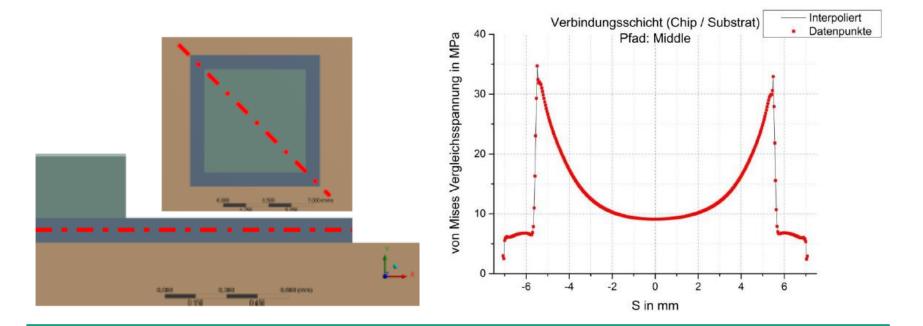

#### Evaluation

- Mechanical stresses in compound layers along diagonal

- Evaluation in the middle of the layer  $\rightarrow$  Boundary layer network-dependent

- Margin area not evaluable  $\rightarrow$  singular

### Fraunhofer

Dr. Christoph F. Bayer et al., Packaging and Modules Departement DEVICES AND RELIABILITY © Fraunhofer IISB

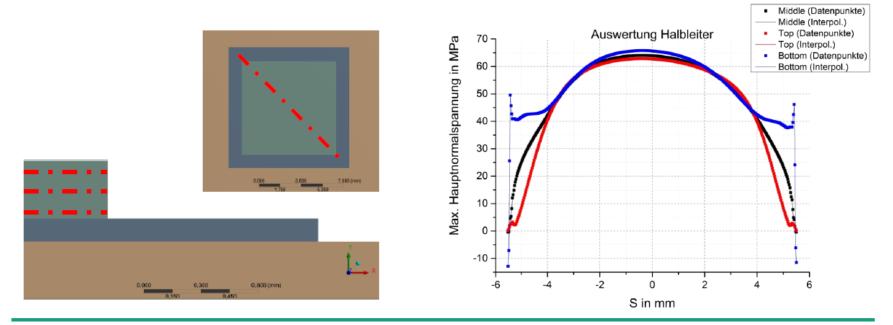

#### Evaluation

Normal stress hypothesis (plane stress state)

$$\sigma_v = \sigma_{1,2} = \frac{1}{2} \left[ \left( \sigma_x + \sigma_y \right) \pm \sqrt{\left( (\sigma_x - \sigma_y)^2 + 4\tau_{xy}^2 \right)} \right]$$

Greatest normal stress = 1. Main stress

- Application for brittle materials  $\rightarrow$  Si-Chip, Ceramic

- Tensile fracture strength of a Si chip is approx. 50 200 MPa\*  $\rightarrow$ Borders not taken into account!

- Evaluation (in Ansys):

- Positive normal stress = tensile stress

- Negative normal stress = compressive stress

#### Evaluation

Mechanical stresses in semiconductors along diagonal

- Evaluation on diagonals in several planes of the chip

- Margin area not analyzable → singular

#### Slide 100

Dr. Christoph F. Bayer et al., Packaging and Modules Departement DEVICES AND RELIABILITY © Fraunhofer IISB 🗾 Fraunhofer

#### Further possibilities

- Thermal simulation

- Unsteady material properties

- Phase transitions

- Latent heat storage

- 2 2 Phase cooling

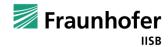

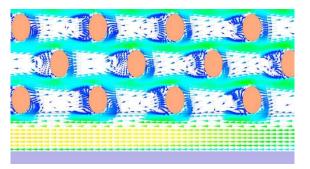

- Flux simulations (CFX/CFD)

- Pressure drop in the cooling channel

- Optimization of cooling structures

- Mechanical simulation

- Plastic properties

- Lifetime modelling

- Crack propagation

Heat dissipation and deformation in power modules

- **Risks**, problems, inaccuracies

- Material data

- Temperature dependence

- Plastic material data difficult to obtain (e.g. "What copper do I really have?"  $\rightarrow$  Cu-OFE? Cu-HCP? Cu-ETP? Cu-DHP?)

- Influence of manufacturing processes?  $\rightarrow$  Recrystallisation

- Network fineness (vs. computing time)

- Cooling capacities/ inflow conditions

- Evaluation at singular points not practical

- Idealization

- Active volume in the chip

- Layer thickness / homogeneity

- Constant heat dissipation via cooling surfaces

- Neglect of temperature-related process steps

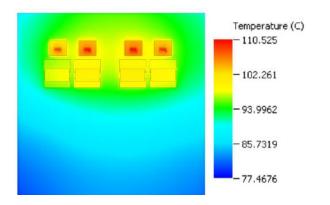

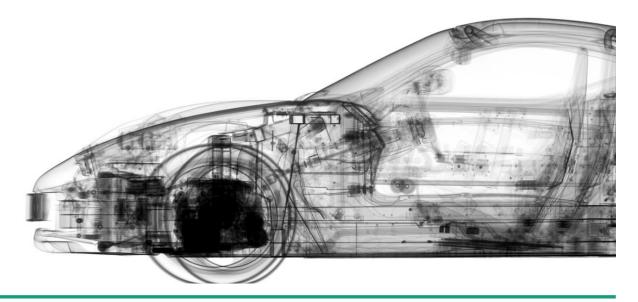

*Thermal simulation of electronic systems during design - Conjugate Heat Transfer*

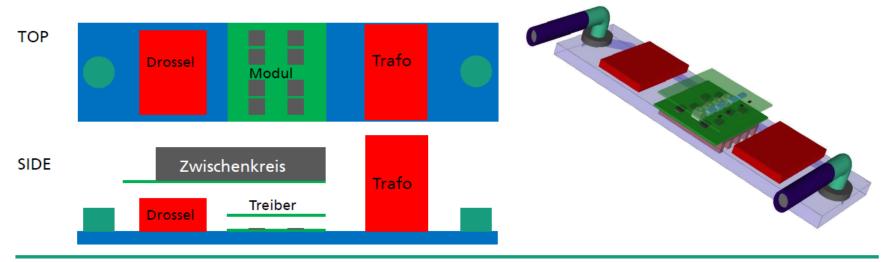

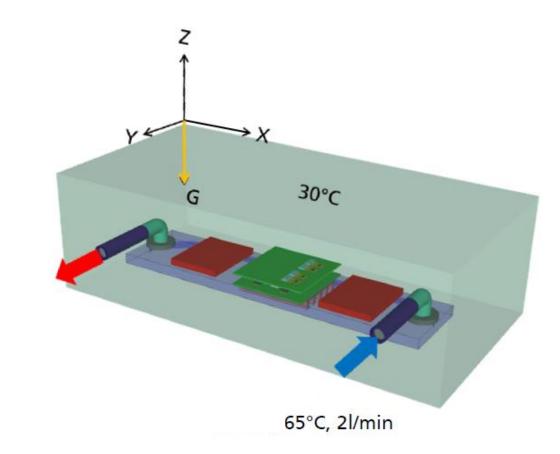

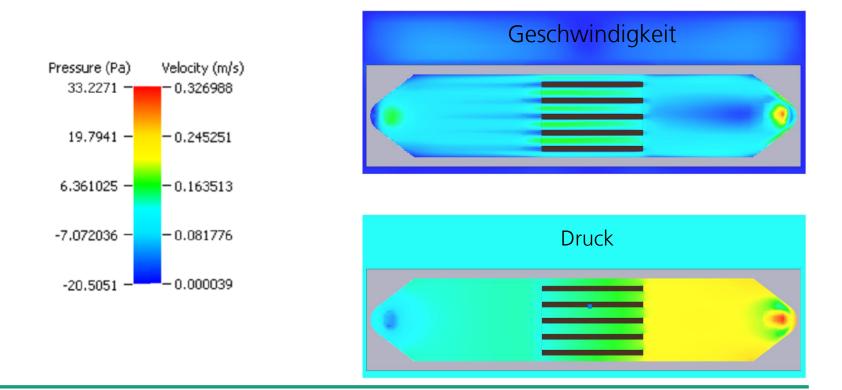

#### Example simulation with 6SigmaET

- Simulation of an isolating DC/DC converter

- Goals

- Compliance with the component-specific boundary conditions

- Identify challenges early on and develop solutions

#### Slide 103

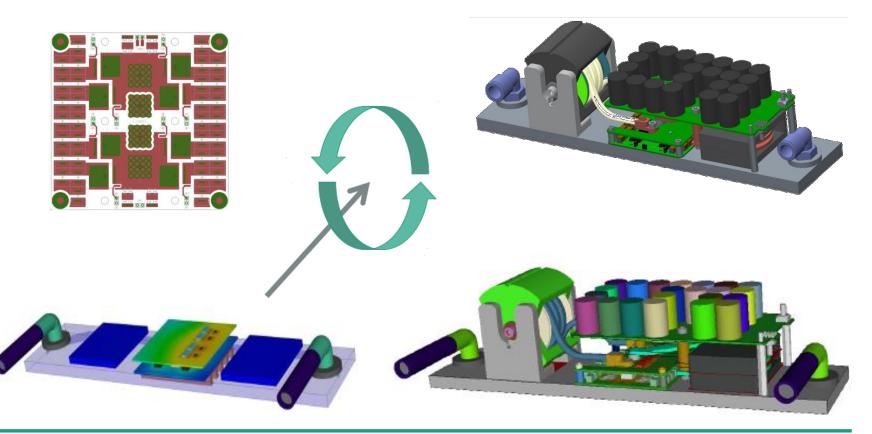

## *Thermal simulation of electronic systems during design - Conjugate Heat Transfer*

- Idealization

- Right-angled edges

- Ideal contact surfaces, solid-solid and fluid-solid

- No roughness (with restriction)

- No rounding (special networking)

- Classification of the components according to their relevance

- Detailed, Flow obstruction, Decorative

- Material data

- Characteristic values for each material suitable for the desired simulation

- See data sheet information

- Verification of the data

Thermal simulation of electronic systems during design - Conjugate Heat Transfer

- Boundary conditions

- Temperature

- **Environment**

- Coolant

- Current

- Components

- Speed

- Volume flow

- Gravitation

- Radiation

Slide 105

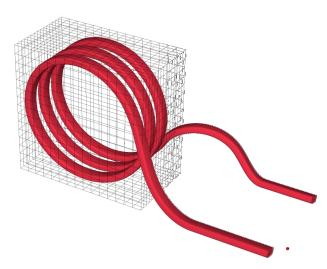

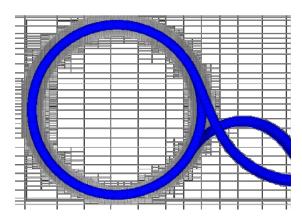

Thermal simulation of electronic systems during design - Conjugate Heat Transfer

- Networking

- Cartesian grid

- Too large elements can lead to unwanted contact points

- Grid Control Variants

- Direction

- Quantity

- Size

- Approximating the geometry

- Size of the cells in the structure

- Size of the cells in the surrounding fluid

- Inflation

- The computing time depends on

- parallelization, number of cells, type of cells, etc.

- Display of results

- Temperature (component, environment, distribution)

- Speed, pressure

- Ohmic losses

Slide 107

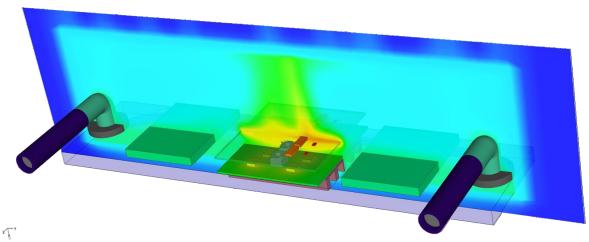

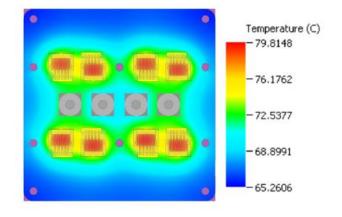

#### Simulation result (example 6SigmaET)

#### List of the temperature of each component

| Owner PCB    | Junction<br>Temperature                                                                                                                                            | Mean Volume<br>Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Driver_Board | 108.1                                                                                                                                                              | 108.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Driver_Board | 110.1                                                                                                                                                              | 110.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Driver_Board | 110.6                                                                                                                                                              | 110.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Driver_Board | 109.2                                                                                                                                                              | 109.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Module       | 87.89                                                                                                                                                              | 87.89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Module       | 87.39                                                                                                                                                              | 87.39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Module       | 87.83                                                                                                                                                              | 87.83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Module       | 87.2                                                                                                                                                               | 87.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Module       | 87.99                                                                                                                                                              | 87.99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Module       | 87.4                                                                                                                                                               | 87.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Module       | 88.43                                                                                                                                                              | 88.43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Module       | 87.69                                                                                                                                                              | 87.69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Driver_Board |                                                                                                                                                                    | 97.97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Driver_Board |                                                                                                                                                                    | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Driver_Board |                                                                                                                                                                    | 100.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Driver_Board |                                                                                                                                                                    | 99.07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | Driver_Board<br>Driver_Board<br>Driver_Board<br>Driver_Board<br>Module<br>Module<br>Module<br>Module<br>Module<br>Module<br>Module<br>Driver_Board<br>Driver_Board | Owner PCBTemperatureDriver_Board108.1Driver_Board110.1Driver_Board110.6Driver_Board109.2Module87.89Module87.39Module87.2Module87.99Module87.4Module87.4Module87.69Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0Driver_Board0 </td |

- Simulation result (example 6SigmaET)

- Flow simulation

#### Slide 109

Model iterations  $\rightarrow$  Import of CAD data, layout programs

Slide 110

Fraunhofer

#### Simulation methods and theoretical consideration Thermal simulation of electronic systems during design - Conjugate Heat Transfer

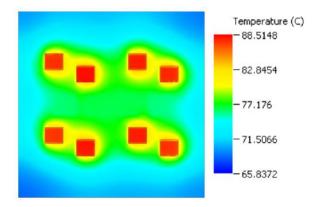

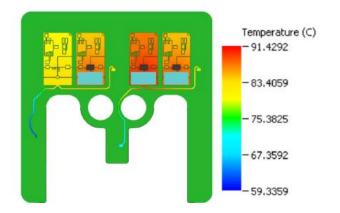

#### Simulation results of the final model (example 6SigmaETO)

DC/DC converters

### Simulation methods and theoretical consideration Thermal simulation of electronic systems during design - Conjugate Heat Transfer

Simulation evaluation (example 6SigmaETO)

Heat flow transformer coiling, connection, module

Slide 112

#### Simulation methods and theoretical consideration Thermal simulation of electronic systems during design - Conjugate Heat Transfer

#### Simulation result (example 6SigmaET)

#### List of the temperature of each component

|                            | Owner PCB    | Junction<br>Temperature | Mean Volume<br>Temperature |

|----------------------------|--------------|-------------------------|----------------------------|

| Gate_switch_1 (Case)       | Driver_Board | 85.3                    | 85.3                       |

| Gate_switch_2 (Case)       | Driver_Board | 89.47                   | 89.47                      |

| Gate_switch_3 (Case)       | Driver_Board | 91.81                   | 91.81                      |

| Gate_switch_4 (Case)       | Driver_Board | 89.82                   | 89.82                      |

| Switch_1 (IPT020)          | Module       | 75.91                   | 75.91                      |

| Switch_2 (IPT020)          | Module       | 76.42                   | 76.42                      |

| Switch_3 (IPT020)          | Module       | 76.55                   | 76.55                      |

| Switch_4 (IPT020)          | Module       | 76.1                    | 76.1                       |

| Switch_5 (IPT020)          | Module       | 76.3                    | 76.3                       |

| Switch_6 (IPT020)          | Module       | 76.49                   | 76.49                      |

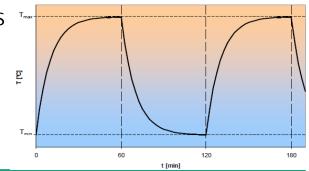

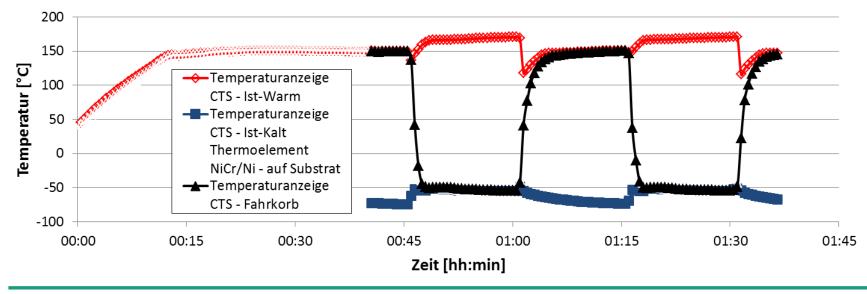

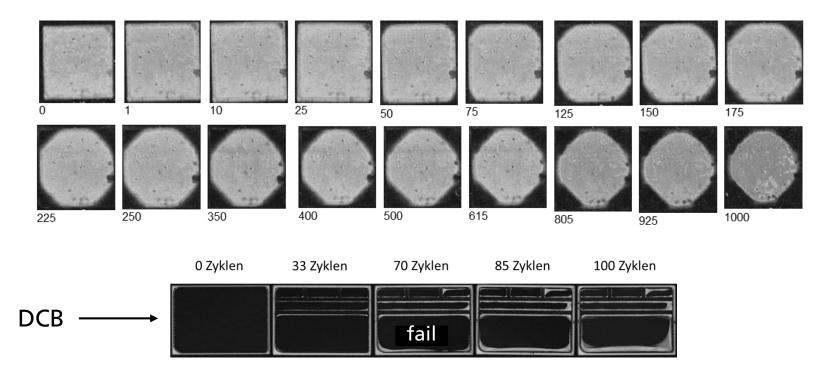

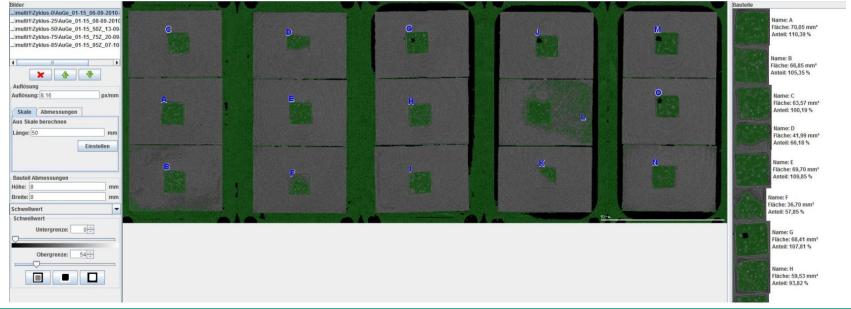

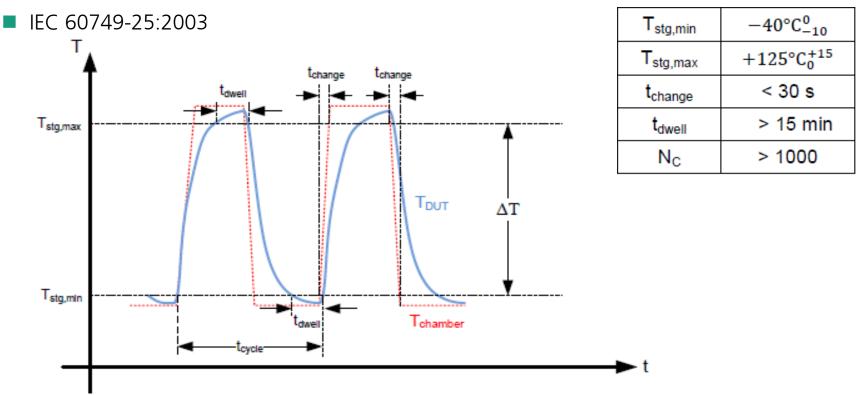

| Switch_7 (IPT020)          | Module       | 76.44                   | 76.44                      |