# Single Event Effects by atmospheric neutrons in commercial (COTS) normally-off GaN HEMT

<u>Dorothea Wölk <sup>1</sup>, Stefan K. Höffgen<sup>1</sup>, Eike Paschkowski<sup>1</sup>, Michael Steffens<sup>1</sup>, Carlo Cazzaniga<sup>2</sup>, Christopher Frost<sup>2</sup></u> <sup>1</sup> Fraunhofer INT, Euskirchen, Germany; <sup>2</sup> Rutherford Appleton Laboratory, Didcot, United Kingdom

Abstract: Results of SEE testing of commercial high power normally-off GaN-devices with an atmospheric-like neutron spectrum at ChipIR are presented. Three different designs of GaN-HEMTs and one SiC-MOSFET were tested at different voltages and the cross sections were determined.

# **Motivation**

# Set up

Normally-off Gallium-Nitride electron high mobility transistors (GaN-HEMT) for high power applications have become available commercially since a few years and have several advantages compared to standard silicon transistors [1]. They are much smaller, lighter and have a higher breakdown field. For lower voltages and normally-on RF devices some testing of radiation effects has been done [2], but for newly developed 600V and 650V normally-off devices testing has just started [3] and most of the experiments were done with protons or (heavy) ions, aiming at space applications. For terrestrial or aviation use the effects induced by atmospheric neutrons are of greater concern. Therefore different kinds of GaN-HEMTs were tested for neutron induced single event effects in an atmospheric-like spectrum at ChipIR, Rutherford Appleton Laboratory.

For this study we tested 3 normally-off high power GaN-HEMT and one SiC n-MOSFET (Rhom SCT3120AL) for comparison with a maximum drainsource Voltage of about 600V (TABLE I.). Two of the GaN-devices (Panasonic PGA26E18BA, GaN-Systems GS66502B) are normally-off by intrinsic design of the GaN HEMT structure. The third GaN-Device (Transphorm TPH3202P) is a normally-on GaN HEMT which is set to normally-off by adding a low voltage silicon MOSFET in the package forming a cascode structure).

The measurements took place at the ChipIR beamline of the ISIS neutron and muon source facility at the Rutherford Appleton Laboratory near Oxford, which features an atmospheric-like neutron spectrum with about  $4.10^6$  n/(cm<sup>2</sup> s) [4].

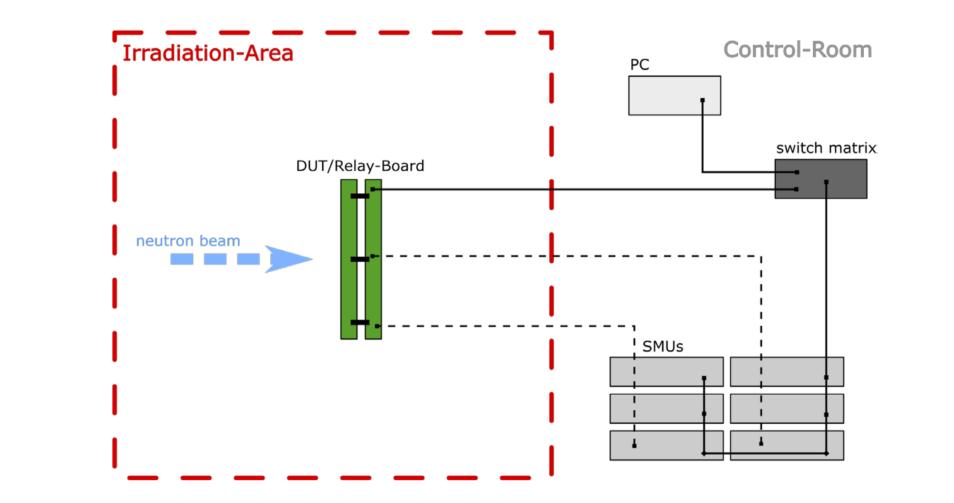

Gate-Voltage and Drain-Voltage were applied separately and the leakage currents were recorded at least every 2 seconds for every device by 6 SMUs (two Keithley 2657A, one Keithley 2410 for the drain currents and three Keithley 2400 for the Gate currents) (Fig. 2).

The upper limit for the drain voltage that could be applied was given by the relays on the board and was 1000 V each. As an indicator of a Single Event Burnout (SEB) we determined the abrupt and permanent rise of the drain leakage current above 1 mA.

Fig. 1. Schematic of the experimental set up at ISIS-ChipIR. The red box symbolizes the irradiation area with the board. The solid connections represent the data-line, the dashed ones the currents.

Fig. 2. Photo of the testboard . The board was aligned in such way, that the beampoint of about 7x7 cm hit one cluster of three at a time and could be moved in the y and z direction.

### Results

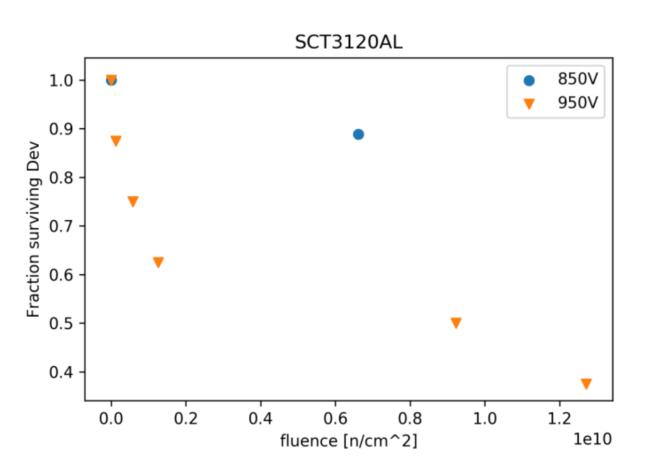

Fraction of surviving SCT3120AL Fig. 4. normalized to the complete sample and plotted against the fluence for different voltages.

| Device Type | Туре             | V <sub>DS</sub> | N  | N              | V <sub>SEE</sub> (min) |

|-------------|------------------|-----------------|----|----------------|------------------------|

|             | туре             | ♥ DS            |    | <b>'</b> ∎fail | SEE(                   |

| GS66502B    | GaN-HEMT         | 650 V           | 21 | 9              | 850 V                  |

| PGA26E19BA  | GaN-HEMT         | 600 V           | 20 | 6              | 800 V                  |

| ТРН3202Р    | Cascodestructure | 600V            | 12 | 0              | > 1000 V               |

| SCT3120AL   | SiC n-MOSFET     | 650V            | 14 | 5              | 850 V                  |

No SEB could be seen below the maximum rating the manufacturer has given in the data sheet. To get more information about the general sensitivity of the devices, they were biased outside their specifications (Tabel).

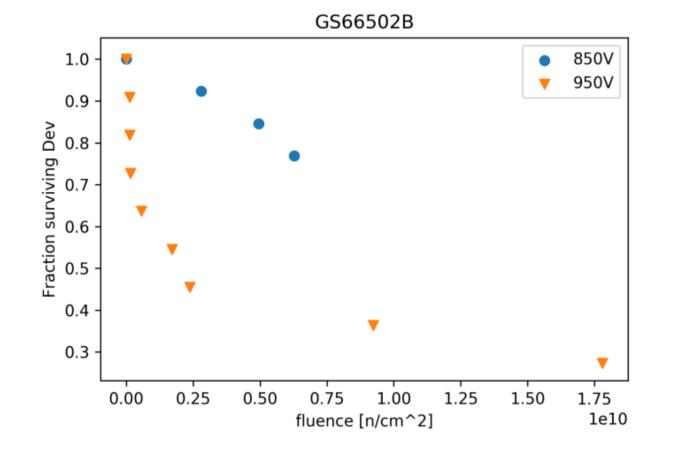

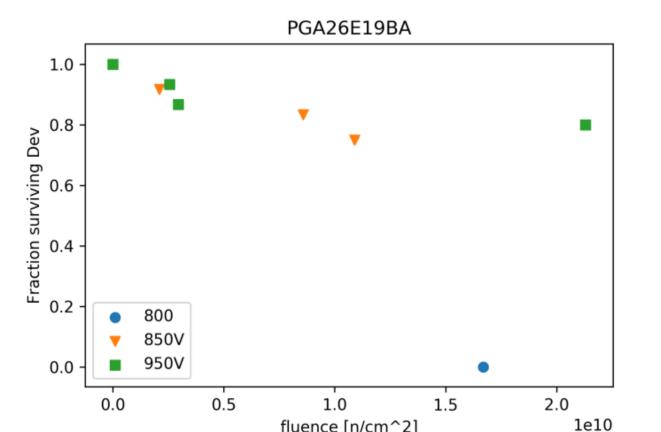

Fig. 3-4 show the number of surviving devices as a function of the fluence, depending on the applied drain voltage.

We also took measurements with a maximum negative gate-voltage applied during the measurement but could not find any effect on the device sensitivity.

For the TPH3202P no SEB was seen up to a  $V_{DS}$  of 1000V, which was the maximum voltage the switching relays on the test board were rated for.

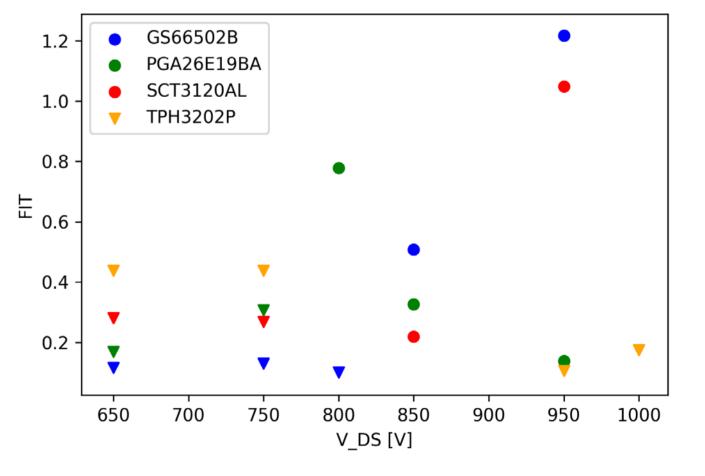

#### FIT

The Failure in time (FIT) rate with respect to the New York fluence (Fig. 9) is calculated for every voltage step and each device type according to [5]. At the voltages, where none of the devices failed, we marked an upper limit of the FIT-rate with a downward arrow. New

fluence [n/cm^2]

Fig. 5. Fraction of surviving PGA26E19BA normalized to the complete sample and plotted against the fluence for different voltages.

Tabel 1: Tested Device-Types and the Minimum voltage at which an see was detected.

It can be shown that for the device-types tested the voltages at which the first SEBs could be observed are at least 200 V above the manufacturers given maximum ratings.

# References

- [1] M. Meneghini, O. Hilt, J. Wuerfl and G. Meneghesso, "Technology and Reliability of Normally-off GaN HEMTs with p-Type Gate", Energies 2017, 10, 153, 2017

- [2] S. J. Pearton, F. Ren, E.Patrick, M. E. Law, and A. Y. Polyakov, "Review Ionizing Radiation Damage Effects on GaN Devices", ECS Journal, 5, Q35-60, 2016

- [3] L. Z. Scheick, "Recent Gallium Nitride Power HEMT Single Event Testing Results", IEEE 978-1-5090-6081-8, 2016

- [4] C. Cazzaniga, and C. Frost, "Progress of the Scientific Commissioning of a fast neutron beamline for Chip Irradiation", IOP Conf. Deries: Journal of Physics: Conf. Series 1021, 2018

- [5] JEDEC Publication No. 151, Test Procedure for the Measurement of Terrestrial Cosmic Ray Induced Destructive Effects in Power Semiconductor Devices, 2015

# Acknowledgements

We want to thank Dr. Carlo Cazzaniga and Dr. Christopher Frost at the ISIS Chip IR for the opportunity and the great support they gave us during the measurements.

# Contact

Appelsgarten 2

Fraunhofer INT

53879 Euskirchen Germany

dorothea.woelk@int.fraunhofer.de