# **A TCAD Process Model with Monte Carlo Ion Implantation for** 4H-SiC JBS Diode Analysis and Design

J. Büttner\*, S. Beuer, S. Petersen, M. Rommel, T. Erlbacher, A. Bauer

Fraunhofer IISB, Schottkystrasse 10, 91058 Erlangen, Germany

\*jonas.buettner@iisb.fraunhofer.de

## Introduction

The electrical characteristics of Junction Barrier Schottky (JBS) diodes are primarily determined by the geometry and dimensions of the junction barrier which is formed by ion implantation. The final doping profile is affected by the implantation parameters and process conditions. Channeling, lateral straggling, as well as flank angle and resolution of the implantation mask have an influence on the profile shape [1]. A TCAD process model was developed to reproduce the parameters and conditions of the ion implantation and to analyze the electrical characteristics of devices depending on the design of the junction barrier.

## **TCAD Process Model**

### **Process Simulation**

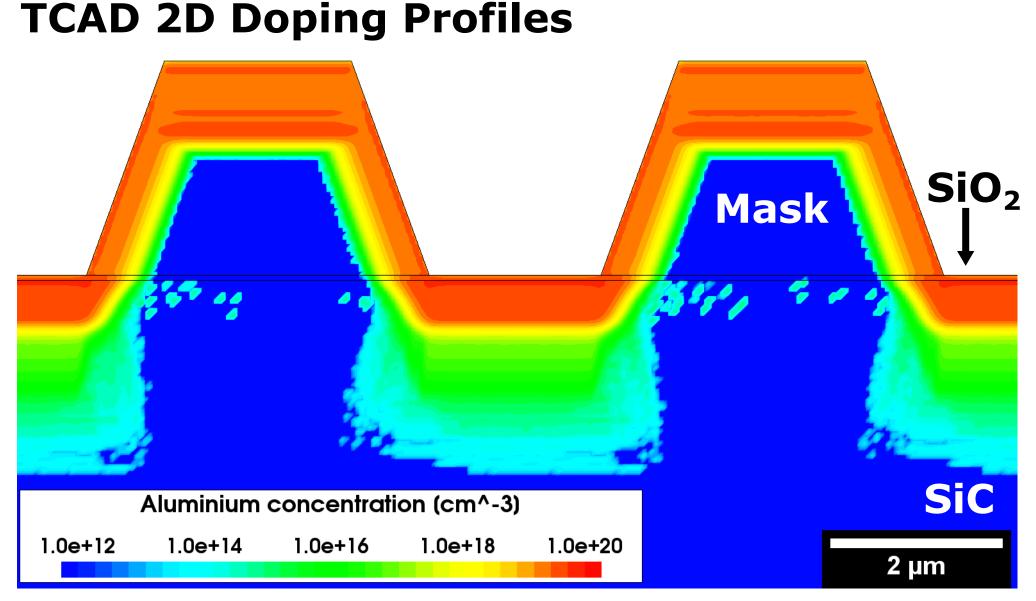

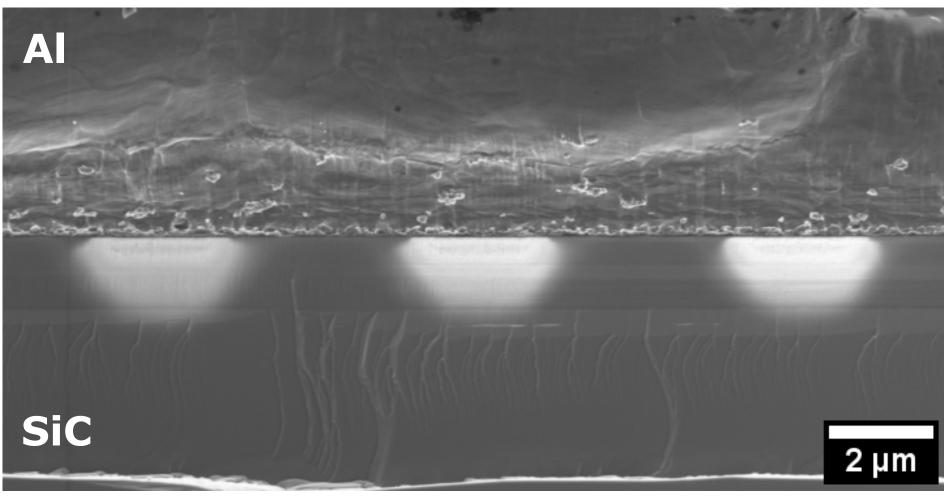

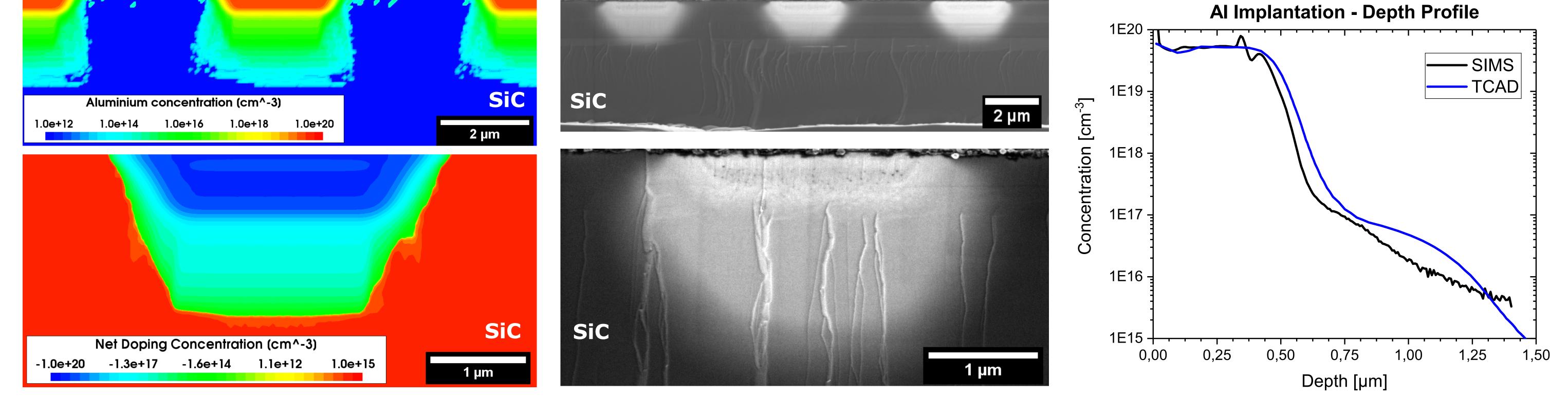

The TCAD model was implemented in Synopsis A simulated 1D doping profile and corres-Sentaurus. The process simulation included ponding SIMS measurement are shown below. deposition of a scattering oxide, aluminium ion The simulation fits well to the data in the implantation, high temperature annealing, plateau region. Diffusion during the activation thermal oxidation and metal deposition. The anneal which is not considered accurately in simulation parameters were taken and the process model might cause the differences adapted from a standard diode process. visible at lower concentrations. Ion channeling Special focus was given to the Monte Carlo below  $1 \times 10^{17}$  cm<sup>-3</sup> is evident in both profiles. (MC) ion implantation. TCAD 2D doping profiles of nominally 2 µm The 4H-SiC n-type substrate and epitaxial wide  $p^+$  stripes implanted with aluminium to layer were cut 4° off the [0001] direction. The form a 500 nm deep box profile are depicted aluminium implantation was performed under next to doping contrast cross-section images a 7° tilt with a dose of 2.6 x  $10^{15}$  cm<sup>-3</sup>. The of a diode. The general shape of the resist mask was implemented with a flank implantation profile is trapezoidal which is due angle of 70° which was extracted from to the low mask flank angle. A higher flank electron images of resist cross-sections. angle leads to a more rectangular shape. The box profile plateau of about 5 x 10<sup>19</sup> cm<sup>-3</sup> is **Doping Contrast Images** surrounded by a larger halo region where channeling and lateral straggling dominate. This increases the width of the junction barrier stripes by about 800 nm compared to the nominal width in the layout.

### MC Ion Implantation

### **Model Verification**

#### **Diode Fabrication**

For verification of the model JBS diodes with a striped junction barrier design were fabricated on 100 mm 4H-SiC wafers with a 11 µm wide, 7.0  $\times$  10<sup>15</sup> cm<sup>-3</sup> n<sup>-</sup> doped epitaxial layer. The implantation parameters were chosen to yield a 5.0  $\times$  10<sup>19</sup> cm<sup>-3</sup> box profile as shown in the figures above. The implantation was annealed at 1700°C for 30 minutes. 100 nm titanium, annealed at 450°C for 30 minutes, was used for the Schottky contact and 4 µm aluminium for the electrode. Two diode variants with 2  $\mu m$  nominal p<sup>+</sup> width and spacing of 3  $\mu m$  and 4  $\mu$ m, respectively, were investigated.

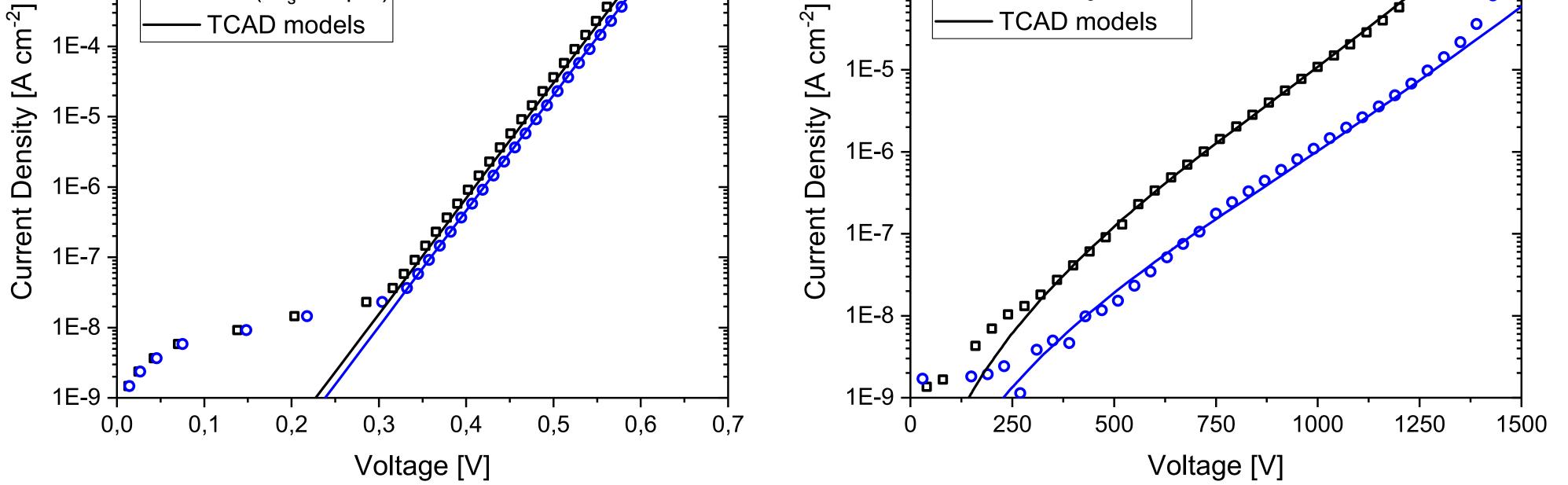

#### **Forward Bias**

Electrical measurements of two nearly ideal JBS diodes with different spacing W<sub>s</sub> are plotted against data from the TCAD simulation. The measurement data confirms the validity of the model. Above the measurement resolution the model data fits well to the diodes in the low current regime. The difference in spacing results in a change of only a few tens of millivolts.

#### **Forward current characteristics Reverse current characteristics** 0,001 0,01 JBS ( $W_s = 4 \mu m$ ) JBS ( $W_s = 4 \mu m$ ) 0,001 JBS ( $W_s = 3 \mu m$ ) JBS ( $W_s = 3 \mu m$ ) 1E-4 -0 0

#### **Reverse Bias**

The model accurately reflects the differences in leakage current between the diode variants. The leakage at 1200 V is below 10  $\mu$ A cm<sup>-2</sup> with 3  $\mu$ m and 100  $\mu$ A cm<sup>-2</sup> with 4  $\mu$ m spacing. The reduced leakage current for the narrow spacing comes with little penalty under forward bias. The avalanche onset at 1300 V is not seen in the simulation due the breakdown being in the edge termination region.

#### **Electrical Simulation**

The device simulation using the developed process model took into account image force barrier lowering and tunneling across the Schottky barrier. The same parameters were used for forward and reverse bias simulations. The work function of the contact metal was calibrated using data from a Schottky Barrier Diode. A Schottky barrier height of about 1.2 V extracted from the simulation which was agrees well with published data.

### References

[1] J. Buettner, T. Erlbacher, et al., Technological Advances Towards 4H-SiC JBS Diodes for Wind Power Applications, Applications in Electronics Pervading Industry, Environment and Society (2018) 83.