### Power Electronics Packaging at Fraunhofer IISB

Double Sided Cooling, Selectively Sintering, Ceramic Embedding and more

### FRAUNHOFER Institute for Integrated Systems and Device Technology (IISB) POWER ELECTRONICS

SIMULATION MATERIALS TECHNOLOGY AND MANUFACTURING DEVICES AND RELIABILITY VEHICLE ELECTRONICS ENERGY ELECTRONICS

Packaging

**Devices**

Christoph F. Bayer, Slide 2 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

Test and

Reliability

#### FRAUNHOFER IISB – FIELDS OF COMPETENCE

### POWER ELECTRONIC SYSTEMS

From Material to Power Electronic Applications

Create Value beyond Borders

SIMULATION MATERIALS TECHNOLOGY AND MANUFACTURING DEVICES AND RELIABILITY VEHICLE ELECTRONICS ENERGY ELECTRONICS

Christoph F. Bayer, Slide 6 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

PART OF

#### FRAUNHOFER IISB – PACKAGING AND RELIABILITY

### **DEVICES AND RELIABILITY** Fields of Competence From Material to Power Electronic Applications

Tobias Erlbacher

Christoph F. Bayer

Devices

Test and Reliability

Over 30 employes and about 30 students

Packaging

PART OF

Christoph F. Bayer, Slide 7 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

Andreas Schletz Head of Department

#### FRAUNHOFER IISB - DEPARTMENT

### **PACKAGING AND RELIABILITY**

New concepts and materials for packaging

High performance joining technologies, sintering

Thermal, electrical, and mechanical characterization

Lifetime characterization, statistical analysis

Analysis of failure mechanism

Lifetime modeling

Christoph F. Bayer, Slide 8 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

#### FRAUNHOFER IISB - DEVICES AND RELIABILITY

### **DEVICES AND RELIABILITY**

Christoph F. Bayer, Slide 9 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

#### FRAUNHOFER IISB – DEVICES AND RELIABILITY

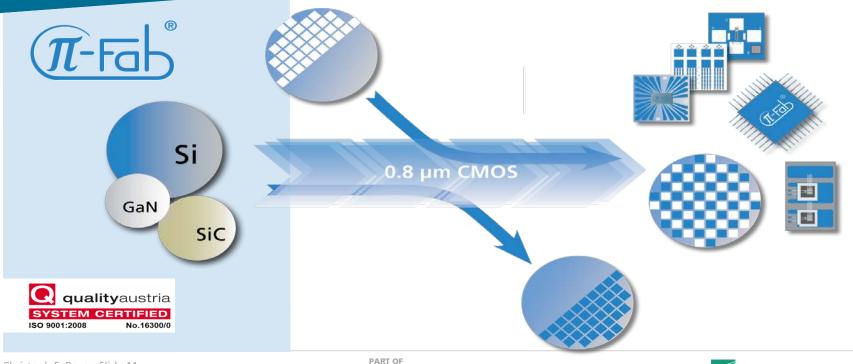

### **DEVICES** Prototype Fabrication: Access to π-Fab

### Fabrication of SiC-devices qualified (ISO 9001) processing environment

- Foundation: 200 mm silicon CMOS line

- Upgraded to: 150 mm SiC pilot line

JITC

Christoph F. Bayer, Slide 10 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

centrother

USHEII

#### FRAUNHOFER IISB – DEVICES AND RELIABILITY

### **DEVICES** Prototype Fabrication: Access to π-Fab

Christoph F. Bayer, Slide 11 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

#### FRAUNHOFER IISB - PACKAGING AND RELIABILITY

### **PACKAGING AND RELIABILITY**

#### FRAUNHOFER IISB – PACKAGING AND RELIABILITY

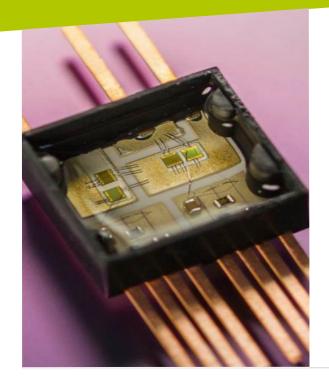

### **PACKAGING** Power and Signal Electronics

#### Power and Signal Electronics

- GaN and SiC power devides

- Integrated gate driver

- Low parasitics

- Silver sintered die-attach for power devices

- High rel. bond wires

- Extended lifetime

- Substrate with metallization for power and signals

Christoph F. Bayer, Slide 15 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

#### FRAUNHOFER IISB – PACKAGING AND RELIABILITY

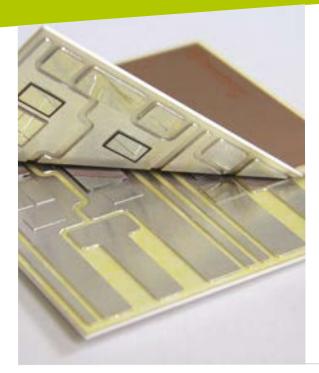

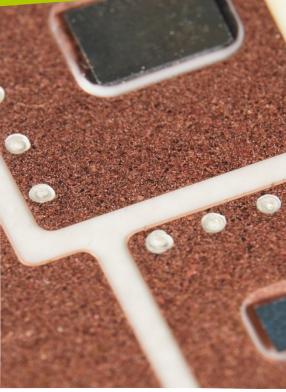

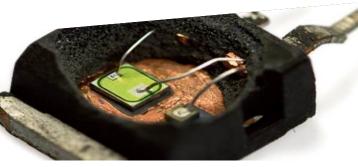

### **PACKAGING** Sintering on Leadframe for Chip Embedding

#### Sintering on Leadframe

- Selective sintering process

- Printing

- Drying

- Chip pick and place

- Transfer to die backside

- Pick and place into cavity

- Final sintering by die servo press

R. Randoll, W.Wondrak, A.Schletz: Dielectric Strength and Thermal Performance of PCB-Embedded Power Electronics, ESREF 2014

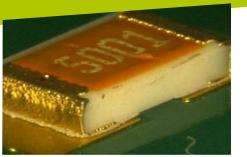

### FRAUNHOFER IISB – PACKAGING AND RELIABILITY **PACKAGING** Selective Sintering on PCB

## Sintering of Bare Die or SMD Devices on pre-populated Circuit Boards

- Selective sintering process

- Printing

- Drying

- Chip pick and place

- Transfer to die backside

- Pick and place

- Final sintering by die placer

Christoph F. Bayer, Slide 17 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

### FRAUNHOFER IISB – PACKAGING AND RELIABILITY **PACKAGING** Top Side Chip Contact

#### Top Side Leadframe

- Ag-Sintering

- Pressure less process

- Stress relieving measures

Christoph F. Bayer, Slide 19 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

#### FRAUNHOFER IISB - PACKAGING AND RELIABILITY

### **PACKAGING** Top Side Chip Contact

#### Double Sided Concept

- Full H-bridge

- Chip on busbar

#### Technologies

- Double sided Ag-sintering

- Sic Fet

- Low inductive communication

- Integrated Si-Snubber

Fraunhofer

#### FRAUNHOFER IISB – PACKAGING AND RELIABILITY

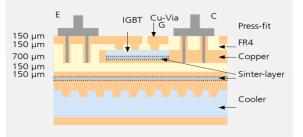

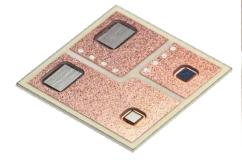

### **PACKAGING** Double Sided Cooling

#### **Double Sided Cooling**

- R<sub>th</sub> down to 50 % vs. standard

- Exceptional power density

- Minimum number of different materials

- Non mechanical stress to material stack induced by module fixing or clamping

- Double sided sintered die attach approach

Christoph F. Bayer, Slide 21 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

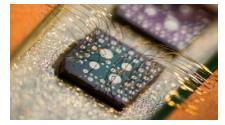

### FRAUNHOFER IISB – PACKAGING AND RELIABILITY **PACKAGING** Ceramic Embedding

#### Project DiaLe

- Diamond for future power electronics applications

- Cooperation of different Fraunhofer institutes

- Diamond wafer manufacture technology for the development of diamond based devices

- Packaging technologies for WBG devices based on ceramic embedding

Christoph F. Bayer, Slide 22 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

WBG embedded in DBC substrate

Diamond Diodes bonded with Au-wires

PART OF Forschungsfabrik Mikroelektronik Deutschland

#### FRAUNHOFER IISB – TEST AND RELIABILITIY

### **TEST AND RELIABILITY**

# FRAUNHOFER IISB – TEST AND RELIABILITY

#### Test and Reliability

- Active power cycling

- Passive temperature test

- Storage tests (HTRB, H3TRB)

- Corrosive gas test

- Damp heat test

- Statistical analysis

- Test plans and methods

- Lifetime modelling

- Soon: preassure cooker, salt spray, highly accelerated stress test (HAST)

Christoph F. Bayer, Slide 30 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

### FRAUNHOFER IISB – TEST AND RELIABILITY **TEST AND RELIABILITY** Active Power Cycling Tests

- 5 independent test benches available

- Up to 20 devices in one test run

- On-line measurement and control system for each device under test (indirect measurement principle)

- Thermal impedance Z<sub>th</sub> measurement during each cycle and all samples

- Individual setting of gate-voltage for every device under test

- Automatic end-of-life-detection

- Heating current from 0.1 A up to 2000 A

- Heating voltage up to 35 V

- Heating and cooling power up to 20 kW

- Coolant temperatures from -60.. +350 °C

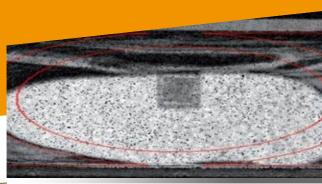

### FRAUNHOFER IISB – TEST AND RELIABILITY **TEST AND RELIABILITY** Non-Destructive Analysis

#### Non-Destructive Analysis

- Optical microscopy

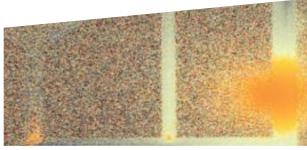

- Ultrasonic microscopy

- Lock-in thermography

- Laser profilometry

- Measurement of electrical parameters

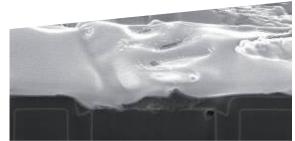

### FRAUNHOFER IISB – TEST AND RELIABILITY **TEST AND RELIABILITY** Destructive Analysis

#### Destructive Analysis

- Cross section

- Shear and pull tests

- FIB-preparation

- Partial discharge measurement

- STA (DSC+TGA), TMA

- Nanoindentation

Christoph F. Bayer, Slide 33 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK

### **THANK YOU FOR YOUR ATTENTION!**

#### Fraunhofer IISB

Schottkystraße 10 91058 Erlangen Germany

andreas.schletz@iisb.fraunhofer.de tobias.erlbacher@iisb.fraunhofer.de christoph.bayer@iisb.fraunhofer.de www.iisb.fraunhofer.de

#### Contact

#### Andreas Schletz Tobias Erlbacher Christoph Friedrich Bayer

Christoph F. Bayer, Slide 35 Power Electronics Packaging at Fraunhofer IISB © Fraunhofer MIKROELEKTRONIK PART OF