# Herausforderungen und Lösungsansätze für die Berücksichtigung des Alterungsverhaltens beim Entwurf integrierter Schaltungen Challenges and approaches to consider ageing behaviour in the design of integrated circuits

Roland Jancke, André Lange, Leif Müller, Christoph Sohrmann Fraunhofer-Institut für Integrierte Schaltungen, Institutsteil Entwurfsautomatisierung, Dresden {roland.jancke; andre.lange; leif.mueller; christoph.sohrmann}@eas.iis.fraunhofer.de

## **Kurzfassung / Abstract**

Die Zuverlässigkeit integrierter Schaltkreise ist seit langem ein wichtiger Aspekt in Forschung und Industrie. Vor allem die Alterung der Schaltungen ist dabei von Interesse. Für viele Teilbereiche von physikalisch motivierter Beschreibung der Effekte bis hin zu Systembetrachtungen wurden Methoden aufgezeigt. Trotzdem sind noch viele Fragen der Alterungsanalyse nicht oder nur unzureichend beantwortet. Dieser Beitrag soll Herausforderungen benennen und prinzipielle Lösungsmöglichkeiten aufzeigen. Deren detaillierte Umsetzung bleibt eine Aufgabe für zukünftige Forschungs- und Entwicklungsarbeiten. Dennoch kann der Nutzen von Alterungssimulationen anhand von Beispielen dargestellt werden.

For a couple of years now, reliability of integrated circuits has been an important topic in research and industry. The main focus has mostly been on degradation due to ageing. A lot of methods were published on different aspects from physical degradation modeling to system-level considerations. However, a lot of open issues remain. Persisting challenges and potential solution approaches are discussed in this paper. Although the detailed implementation of advanced methods is left for future research, simulation examples demonstrate the significance of ageing simulations.

## 1 Einleitung und Motivation

Für den Entwurf integrierter Schaltungen sind neben der eigentlichen Funktion zunehmend nichtfunktionale Eigenschaften zu berücksichtigen. Dazu gehören Variationen aus der Fertigung, elektrothermische Wechselwirkungen, die Alterung von Leitungsstrukturen und insbesondere auch die Degradation von Bauelemente-Eigenschaften aufgrund von Alterungseffekten.

Mit weiter steigendem Integrationsgrad der Fertigungstechnologien treten bekannte Degradationseffekte deutlicher hervor, so dass sie die Funktion der Schaltung bereits unter normalen Einsatzbedingungen wahrnehmbar beeinträchtigen. Hinzu kommen neue Effekte durch neue Materialien im Deep-Submicron-Bereich sowie härtere Umgebungsbedingungen durch innovative Anwendungsbereiche.

Gerade in Bereichen sicherheitskritischer Anwendungen, wie im Transportwesen, der Medizintechnik und der Industrieautomation, sind die Anforderungen an die Langlebigkeit und hochzuverlässige Verfügbarkeit besonders hoch [1]. Die gleichzeitige Forderung nach höchster Energieeffizienz, geringen Kosten und minimalen Abmessungen führt dazu, dass modernste Schaltungstechnik mit höchstskalierten Fertigungstechnologien auch in diesen Bereichen Einzug hält.

Modellierung von Alterungseffekten im Bereich der

Mikro- und Nanoelektronik wird heute bereits vielfach zum Verständnis charakterisierter Datenreihen eingesetzt. Damit können sogenannte Beschleunigungsmodelle erstellt werden, die für eine gegebene Technologie eine Voraussage der erreichbaren Lebensdauer aus kurzzeitigen Stressmessungen ermöglichen. Ziel ist es, die Technologie zu verbessern und sie robust für eine breite Palette von Anwendungen zu machen.

In Zukunft wird hier ein Paradigmenwechsel stattfinden. Dann wird die Simulation des Alterungsverhaltens einer Schaltung Teil des Entwurfs- und Verifikationsablaufs werden. Ursache dafür sind zum einen der zunehmende Einfluss der Degradationseffekte, zum anderen aber auch die Notwendigkeit der Zertifizierung von Schaltungen und Systemen, insbesondere um die Einhaltung von Sicherheitsanforderungen nachzuweisen. Dazu müssen jedoch genaue Modelle und einsatzbereite Simulationsumgebungen für den Designer zur Verfügung stehen.

Die großen kommerziellen Designsysteme besitzen bereits heute die Möglichkeit der Alterungssimulation. Bekannte Systeme sind der RelXpert von Cadence [2], die Interfaces UDRM von Mentor [3] und MOSRA von Synopsys [4]. Eine Verwendung der Tools kann jedoch nur mit entsprechenden technologieabhängigen Modellen erfolgen. Die Tools selbst bringen üblicherweise nur sehr einfache Alterungsmodelle bzw. eine Schnittstelle zur Integration eigener Modelle mit. Es

klafft daher eine beachtliche Lücke zwischen den in der Praxis durchführbaren Charakterisierungsmessungen, den in der Forschung diskutierten aktuellen Alterungsmodellen [5], [6] und den Simulationsmöglichkeiten der Entwurfssysteme.

In diesem Beitrag werden zunächst die Anforderungen an die Alterungsmodellierung dargestellt und dann einige Ansätze aufgezeigt, um die Herausforderungen anzugehen. Kapitel 3 zeigt erste Ergebnisse bei der Anwendung der Alterungsmodellierung für die Unterstützung der Schaltungssimulation.

## 2 Alterungsmodellierung

Die Zuverlässigkeit ist ein wichtiges Thema im Schaltungsentwurf mit aktuellen und zukünftigen IC-Fertigungstechnologien. Wichtig sind dabei sowohl Angaben zur erreichbaren Zuverlässigkeit eines vorhandenen Schaltungsentwurfs, wie auch Hinweise auf geeignete Maßnahmen zur Erhöhung der Zuverlässigkeit im Hinblick auf eine gegebene Spezifikation.

Für die Untersuchung der Zuverlässigkeit einer integrierten Schaltung spielen sowohl Fertigungsvariationen als auch thermische und elektromagnetische Verkopplungen auf dem Chip sowie mit der Umgebung eine Rolle. Einen wichtigen Einfluss haben insbesondere die Alterungsvorgänge der integrierten Bauelemente und der Verbindungsleitungen auf dem Chip. Dabei wird hier nur die elektrische Alterung durch den normalen Betrieb einer Schaltung betrachtet. Darüber hinaus gibt es weitere Degradationseffekte, wie die Alterung von Materialen sowie Aufbau- und Verbindungselementen.

Eine Reihe von elektrischen Alterungsvorgängen integrierter Devices ist bekannt und in der Literatur ausführlich beschrieben. Dazu gehören

- Hot Carrier Injection (HCI),

- Bias Temperature Instability (BTI),

- Stress Induced Leakage Current (SILC) und

- Time Dependent Dielectric Breakdown (TDDB).

Bei der Umsetzung der genannten Alterungseffekte in simulationsfähige Modelle, die eine Vorhersage des Schaltungsverhaltens über mehrere Jahre hinaus ermöglichen, sind unterschiedliche Probleme zu lösen. Im Folgenden sollen einige davon beleuchtet werden.

#### 2.1 Herausforderungen

Die Nutzung von Alterungsmodellen für den Entwurf integrierter Schaltungen läuft üblicherweise in den folgenden Schritten ab:

- Verständnis der zugrundeliegenden physikalischen Alterungsmechanismen

- Erstellung von Modellansätzen für das prinzipielle beobachtete Verhalten

- Parametrisierung des Modells anhand von Messdaten aus der Charakterisierung einer vorhandenen Technologie

- Einsatz des Modells in einer angepassten Simulationsumgebung zur Untersuchung des Einflusses der Alterung auf Systemcharakteristiken

Die Abarbeitung dieser Schritte stellt den Modellierer jedoch vor eine Reihe von Herausforderungen, von denen einige im Folgenden näher betrachtet werden.

#### 2.1.1 Zeitvariabler Stress

Ein typisches Alterungsmodell für den PBTI-Effekt in einer modernen Technologie wird von Kerber angegeben [7]:

$$\Delta U_{\rm th} = A \cdot t^n \cdot U_{\rm gs}^m \tag{1}$$

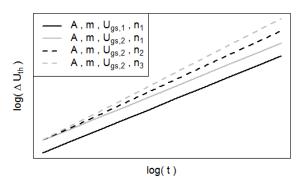

Es beschreibt die Veränderung der Schwellspannung  $U_{\rm th}$  eines NMOS-Transistors in Abhängigkeit von der Länge des Stresses, also der Lebensdauer t, und der Menge des Stresses, hier der Gate-Source-Spannung  $U_{\rm gs}$ , mit den Koeffizienten A, m und n. Zu erkennen ist die exponentielle Abhängigkeit von beiden Faktoren, die im doppelt logarithmischen Maßstab zu einer linearen Abhängigkeit führt, wie in Bild 1 dargestellt.

Bild 1 Prinzipdarstellung des Alterungsmodells in (1) mit den Koeffizienten A und m sowie  $n_1\!<\!n_2\!<\!n_3$  und  $U_{\rm gs,1}\!<\!U_{\rm gs,2}$

Allerdings gilt dieses Modell nur für eine konstant anliegende Gate-Source-Spannung (Constant Voltage Stress – CVS), wie sie in der Charakterisierung auftritt. Auch spezielle Stress-Signale, wie Rampensignale (Voltage Ramp Stress – VRS) werden von Kerber untersucht. Es wird aber betont, dass sich diese Modelle nur für die Prozessüberwachung und nicht für die Simulation eignen. Dazu müssten sie beliebige Stress-Signale verarbeiten können. Ein Modell dafür wurde in [8] abgeleitet: Wird (1) nach der Zeit umgestellt,

$$t = A^{-1/n} \cdot \Delta U_{th}^{1/n} \cdot U_{gs}^{m/n},$$

kann die Zeit t in der Zeitableitung der Schwellspannungsverschiebung ersetzt werden.

$$\frac{\mathrm{d}}{\mathrm{dt}} \Delta U_{\mathrm{th}} = n \cdot A \cdot U_{\mathrm{gs}}^{m} \cdot t^{n-1}$$

$$= n \cdot A^{1/n} \cdot \Delta U_{\mathrm{th}}^{(n-1)/n} \cdot U_{\mathrm{gs}}^{m/n} \quad (2)$$

Wird das bisher als konstant angenommene Stress-Signal in Form der Gate-Source-Spannung  $U_{\rm gs}$  durch zeitvariablen Stress  $u_{\rm gs}(t)$  ersetzt, kann eine explizite Lösung für die Schwellspannungsverschiebung  $\Delta U_{\rm th}$  durch Separation und Integration von (2) gefunden werden.

$$\Delta U_{\rm th} = A \cdot \left[ \int u_{\rm gs}(t)^{m/n} \, \mathrm{dt} \, \right]^n$$

(3)

In dieser Gleichung ist nun ein kontinuierliches, zeitabhängiges Stress-Signal enthalten, wodurch beliebige Zeitverläufe als Eingang simulierbar werden. Für den Sonderfall konstanten Stresses,  $u_{\rm gs}(t) = U_{\rm gs}$  ergibt sich direkt (1).

Auch andere Autoren gehen von zeitkonstantem Stress aus oder nehmen eine Unterteilung in DC- und AC-Stress vor, wobei der AC-Stress durch Frequenz und Duty-Faktor des Pulssignals beschrieben wird. Diese rein digitale Denkweise hat ihre Berechtigung, da viele der kritischen Alterungseffekte in hochskalierten Technologien für die Digitaltechnik auftreten. Sobald aber analoge Schaltungsteile betrachtet werden oder die Frequenzen der Digitalschaltung so groß werden, dass die Pulse deutlich verschliffen sind, sind die Voraussetzungen für die Anwendung der CVS-Modelle nicht mehr gegeben. Diese rein digitale Betrachtungsweise erscheint auch aufgrund anderer Aspekte fragwürdig. Einerseits kann sich die Versorgungsspannung mit der Zeit ändern, entweder schaltungstechnisch gewollt durch Dynamic Voltage Scaling (DVS) oder ungewollt durch IR-Drop. Andererseits altern in Reihe geschaltete Transistoren unterschiedlich, weil sich das Stress-Signal als Differenz von Gate- und Source-Potenzial ergibt.

#### 2.1.2 Komplexe Abhängigkeiten

Als eine weitere wichtige Voraussetzung des genannten Alterungsmodells müssen Spannungs- und Zeitabhängigkeit separierbar sein. Nur dann lässt sich eine solche explizite Darstellung des Lösungsintegrals wie in (3) angeben.

In Messdaten aus der Zuverlässigkeitscharakterisierung moderner Technologien lassen sich jedoch deutlich komplexere Abhängigkeiten erkennen. Es werden neuerdings vielfach ein Sättigungsverhalten in der Zeitabhängigkeit und/oder eine Spannungsabhängigkeit in deren Exponenten n in (1) beschrieben [7].

In diesem Fall sind die Voraussetzungen für die Lösung einer Differentialgleichung, wie z.B. (2), mit einem Zeitintegral nicht mehr gegeben. Die Differentialgleichung zur Beschreibung des Alterungsverhaltens muss in jedem Zeitschritt gelöst werden.

Die Näherung mit konstantem Exponenten in der Zeitabhängigkeit muss auch insofern kritisch betrachtet werden, als dass die Modelle die Grundlage für eine Zeitextrapolation über mehrere Dekaden darstellen: üblicherweise von Messzeiten im Bereich von  $10^0-10^3~\mathrm{s}$  auf Lebensdauern  $t_\mathrm{age}$  von  $10^5-10^8~\mathrm{s}$ . Dabei wirken sich Ungenauigkeiten im Exponenten der betrachteten Abhängigkeiten zunehmend fehlerhaft aus und können zu einer deutlichen Fehleinschätzung bei der zeitlichen Extrapolation auf die tatsächliche Lebensdauer führen.

#### 2.1.3 Zeitextrapolation

Für die Alterungssimulation ist die Extrapolation auf die Lebensdauer eine besondere Herausforderung. Die betrachtete Simulationszeit liegt hier nicht selten im Bereich von nur  $10^{-9} \! \leq \! t_{\rm sim} \! \leq \! 10^{-6} \; {\rm s.}$  Damit ergibt sich eine Extrapolation um 11–17 Dekaden um auf eine realistische Größenordnung für die Lebensdauer  $t_{\rm age}$  zu kommen. Eine Beschleunigung der Degradation durch erhöhte Stressbedingungen wie in der Charakterisierung von Einzeltransistoren funktioniert hier nicht mehr, da die Funktion der Schaltung dann im Allgemeinen nicht mehr gegeben ist und der Stress ja anhand einer konkreten Anwendung der Schaltung ermittelt werden soll.

Eine Simulationszeit in der Größenordnung von Monaten und Jahren ist für praktisch sinnvolle Schaltungen nicht machbar.

Solange sich die Abhängigkeit der Degradation von der Stressbedingung in geschlossener Form angeben lässt, wie in (1), ist keine Extrapolation notwendig. Wie erwähnt gilt diese Beziehung jedoch nur für zeitkonstanten Stress, was im Allgemeinen nicht gegeben ist. Die Bestimmung eines Zeitintegrals für die Degradation, wie in (3), ermöglicht die Verarbeitung beliebiger Stress-Signale. Die Integration erfolgt für jedes Signal über die kurze Simulationszeit  $t_{\rm sim}$  und wird hochgerechnet auf die tatsächliche Lebensdauer  $t_{\rm age}$ .

$$\Delta U_{\rm th} = A \cdot \left[ \frac{t_{\rm age}}{t_{\rm sim}} \cdot \int_0^{t_{\rm sim}} u_{\rm gs}(t)^{m/n} \, dt \right]^n \tag{4}$$

Dabei geht man von einer periodischen Fortsetzung des Signals über die gesamte Lebensdauer aus [8], [9]. Daraus ergeben sich besondere Anforderungen an die Auswahl typischer Testsignale für die Alterungssimulation.

Auch bei der beschriebenen Art der Hochrechnung von der Simulationszeit auf die Lebenszeit durch einfache Multiplikation des Stressintegrals können sich deutliche Fehler ergeben. Dies ist der Fall, wenn sich durch die Degradation einzelner Transistorkennwerte der Arbeitspunkt der Schaltung verschiebt, was wieder Einfluss auf das Stress-Signal selbst hat. Diesem Problem begegnen kommerzielle Werkzeuge durch Unterteilung der Lebensdauer in Abschnitte und eine abschnittsweise Alterungssimulation.

Für den allgemeinen Fall, in dem sich das Stressintegral weder lösen noch explizit aufstellen lässt, ist im Prinzip keine derartige Zeitextrapolation möglich. Hier müssen andere Wege gefunden werden, den enorm großen Abstand der Zeitkonstanten zu überbrücken.

#### 2.1.4 Schaltungskomplexität

Neben den bis hierher genannten Herausforderungen spielt auch die Anzahl der im Schaltkreis integrierten Transistoren eine große Rolle. Eine Alterungsanalyse für mehrere zehntausend Devices über einen langen Zeitbereich ist mit heutigen Mitteln kaum realisierbar. Hier sind Alterungskenngrößen zu definieren und zu abstrahieren um die Menge an Daten zu reduzieren. Im Bereich digitaler Schaltungen wird dies bereits für die niedrigste Abstraktionsebene getan, da sich die typischen Kenngrößen eines Gatters, wie Laufzeit und Treiberfähigkeit, gut in Abhängigkeit vom Alter der Schaltung ausdrücken lassen [10]. Für analoge Schaltungen sind solche Untersuchungen bisher kaum durchgeführt worden.

Obwohl eine Reihe von Möglichkeiten zur Beschleunigung der Simulation vorgeschlagen wurden, ist dennoch für einigermaßen komplexe Schaltungen eine Alterungsanalyse über mehrere Zeitdekaden hinweg nicht machbar. Daher besteht eine weitere Aufgabe darin, aus der Vielzahl der integrierten Bauelemente diejenigen herauszufiltern,

- deren Verhalten sich signifikant ändert und

- die außerdem erheblichen Einfluss auf eine Änderung der Schaltungseigenschaften haben.

Hier kann eine Sensitivitätsanalyse ansetzen, um den relativen Einfluss einzelner Bauelemente zu quantifizieren und die Anzahl der zu untersuchenden Devices deutlich zu reduzieren.

Die Komplexität der Analyse von Schaltungen lässt sich auch mit der Aufstellung von Designregeln reduzieren, die per se für eine Einhaltung von Lebensdauervorgaben sorgen. Die Ableitung von alterungsbezogenen Designregeln aus den angegebenen komplexen Modellen ist jedoch ein offenes Problem.

### 2.1.5 Weitere Einflussfaktoren

Umgekehrt müssen auch die Anforderungen aus einer anvisierten Zielanwendung auf Stressbedingungen in der Schaltung heruntergebrochen werden. Aus typischen Lastzyklen und sogenannten Mission Profiles sind Stress-Signale an den Anschlüssen der Transistoren abzuleiten.

Neben der Alterung des Nominalwertes einer Transistor- oder Schaltungseigenschaft ist es häufig auch von Bedeutung die statistische Verteilung der Charakteristiken zu betrachten [11]. Diese wirkt sich auf Symmetrieeigenschaften einer Schaltung aus und muss bei der Analyse des Alterungsverhaltens großer Blöcke mit einer Vielzahl gleichartiger Zellen untersucht werden. Für die Analyse der Entwicklung von statistischen Verteilungen unter Degradation müssen eine Vielzahl von Devices charakterisiert werden, was heute selten der Fall ist.

#### 2.2 Lösungsansätze

Ein allgemeiner Ansatz zur Untersuchung des Alterungsverhaltens einer Schaltung, mit dem auch komplexe Zeit/Spannungs-Abhängigkeiten berücksichtigt werden können, wird im Folgenden präsentiert. Dazu muss die Änderung der Degradation über der Zeit betrachtet werden. Dies führt jedoch nicht mehr auf eine algebraische sondern auf eine gewöhnliche Differentialgleichung.

$$\frac{d}{dt}\Delta U_{\rm th}(t) = f_{\rm deg}\left(\Delta U_{\rm th}(t), u_{\rm gs}(t)\right) \tag{5}$$

Dieses Degradationsraten-Modell verlangt zusätzlich zur Lösung der Netzwerkgleichungen die Lösung einer weiteren Differentialgleichung für das Alterungsverhalten. Letztere ist allerdings auf der Lebensdauerzeitachse und damit verglichen mit den Netzwerkgleichungen auf einer komplett anderen Skala zu berechnen. Aufgrund der extrem verschiedenen Zeitkonstanten ist eine Lösung mit dem gleichen Solver nicht ratsam bzw. unmöglich. Einen Lösungsansatz bietet die Kopplung des internen Netzwerksimulators mit einem externen Löser für die Alterungsgleichung. Wichtig sind dabei eine geeignete Schrittweitensteuerung und die Synchronisation der Datenübergabe.

Zu den praktisch bedeutsamen Alterungseffekten gehört auch der BTI-Effekt, bei dem die Wegnahme des Stresses zu einer teilweisen Erholung des Bauelements führt. In einem solchen Fall ist neben der Degradation auch die Relaxation zu betrachten. Auch hier ist eine Beziehung für die Änderung der Degradation über der Zeit aufzustellen, in diesem Fall mit umgekehrtem Vorzeichen, also als ein Relaxationsraten-Modell. Dabei tritt im Allgemeinen ein völlig anderes Zeitverhalten als im Stressfall auf. Da die Degradationsrate bei Relaxation von der Vorgeschichte abhängt, ist die Differentialgleichung der Relaxation in der Regel von höherer Ordnung als die des Stressfalls.

$$\frac{d^2}{dt^2} \Delta U_{\rm th}(t) = f_{\rm rel} \left( \frac{d}{dt} \Delta U_{\rm th}(t), \Delta U_{\rm th}(t), u_{\rm gs}(t) \right)$$

(6

Legt man reale Stresspattern mit zeitvariablen Signalverläufen an die Schaltung an, treten Stress und Relaxation gleichzeitig auf. Demzufolge müssen auch beide genannten Abhängigkeiten in einem Modell vereinigt werden. Ein einfacher Weg der Ableitung des gemeinsamen Modells aus den heute üblichen getrennten Charakterisierungen ist nicht bekannt. Beschränkt man sich auf ein linearisiertes Modell, kann ein allgemeiner Ansatz zur Vereinigung der beiden Differentialgleichungen gefunden werden. Dabei werden die Gleichungen verschiedener Ordnung auf mehrere, lineare Gleichungen erster Ordnung zurückgeführt. Es treten zusätzliche, innere Zustände auf, wie sie auch bei physikalisch motivierten Ansätzen gefunden wurden [5].

Das folgende Mehrzustandsratenmodell stellt einen solchen linearen Ansatz zur Verknüpfung von Stress

und Relaxation dar.

$$\dot{\mathbf{p}}(t) = \mathbf{A}(t)\mathbf{p}(t) + \mathbf{b}(t), \ \mathbf{p}(0) = \mathbf{p}_0 \tag{7}$$

mit  $\mathbf{p}(t) \in \mathbb{R}^N$ ,  $\mathbf{A}(t) \in \mathbb{R}^{N \times N}$ ,  $\mathbf{b}(t) \in \mathbb{R}^N$ . Dabei ist  $\mathbf{p}(t)$  ein Vektor der internen Zustände der Länge N. Ein Element dieses Vektors ist die Degradation, beispielsweise modelliert durch  $\Delta u_{\rm th}(t) = p_1(t)^n$ . Bereits mit einem Zweizustandsmodell konnte eine recht gute Übereinstimmung der simulierten Werte mit Messungen erreicht werden. Die Herausforderung besteht jedoch darin, die Modellparameter zu bestimmen.

Der entscheidende Vorteil eines linearen Ansatzes besteht darin, eine analytische Lösung angeben zu können. Damit wird die Zeitextrapolation ermöglicht. Die Lösung der Gleichung (7) ergibt sich zu

$$\mathbf{p}(t) = \exp\left(\int_0^t \mathbf{A}(t')dt'\right) \times \left[\mathbf{p}_0 + \int_0^t e^{-\int_0^{t'} \mathbf{A}(t'')dt''} \mathbf{b}(t')dt'\right]$$

(8)

Eine alternative Möglichkeit, den Zusammenhang zwischen Stress und Relaxation zu charakterisieren, stellt die von Grasser vorgestellte "Time Dependent Defect Spectroscopy (TDDS)" [12] dar. Eine schaltungstechnische Realisierung für die stressbedingte Ladung und Entladung einzelner Defekte wurde von Reisinger [13] vorgeschlagen.

In 2.1.4 wurde bereits auf die Möglichkeit der Erstellung von Designregeln zur Unterstützung eines alterungsgerechten Schaltungsentwurfs hingewiesen. Im Bereich von Leistungshalbleitern ist die Angabe sogenannter Safe Operating Areas (SOAs) sowohl unter thermischen wie auch unter elektrischen Gesichtspunkten eine bekannte Methode [14]. Für einfache Zusammenhänge können SOA-Diagramme unmittelbar aus dem Alterungsmodell im Sinne einer inversen Funktion abgeleitet werden [15], [8]. Sie zeigen die zu erwartende Lebensdauer eines Devices in einem bestimmten Arbeitspunkt, sollte sich das Device dort dauerhaft aufhalten. Als Designregel lassen sich die SOA-Darstellungen einsetzen, indem bestimmte Bereiche der Betriebsbedingungen bereits von vornherein ausgeschlossen werden ("Forbidden Area") oder Bereiche als "nur eingeschränkt nutzbar" für manche langlebige oder sicherheitskritische Anwendungen gekennzeichnet sind.

Ein Weg zur Nutzung der SOAs für den zuverlässigkeitsgerechten Entwurf ist die Untersuchung der Aufenthaltsdauer einzelner Devices in den Bereichen mit unterschiedlicher Lebensdauer. Dazu sind die Vorgaben zu typischen Einsatzszenarien eines ICs auf Stressbedingungen an den Einzeldevices herunterzubrechen. Umgekehrt ergibt sich die Gesamtlebensdauer des Devices dann aus den Aufenthaltsdauern in den verschiedenen Bereichen. Damit können SOA-Diagramme auch zur Abschätzung der Gesamtlebensdauer unter gegebenen Einsatzszenarien eingesetzt

werden. In Grenzen überträgt dieses Vorgehen die Lebensdauerberechnung anhand von Wöhlerlinien [16] aus der Werkstofftechnik auf die Mikroelektronik.

### 2.3 Schnittstellen zur Implementierung

Wie in der Einleitung angedeutet, wird die Alterungsmodellierung heute vielfach im Zuge der Technologiecharakterisierung eingesetzt. Damit lässt sich ein

Großteil der Auswirkungen abfangen. Die verbleibenden, durch technologische Maßnahmen nicht zu beseitigenden Degradationseffekte müssen dem Designer

von integrierten Schaltungen bekannt sein, damit er

die Auswirkungen auf das Verhalten seiner Schaltung

untersuchen kann. Dazu sind die Informationen aus

der technologischen Charakterisierung dem Entwerfer

in dessen Entwurfssystem zur Verfügung zu stellen.

Modellierung und Simulation von Alterungseffekten

müssen Teil der Entwurfsunterstützung werden.

Für die Implementierung von Alterungsinformationen müssen verschiedene Akteure zusammengebracht und Schnittstellen zwischen ihnen definiert werden. Die Technologen stellen die Informationen zu relevanten Degradationseffekten für die Bauelemente in komprimierter Form bereit. Als Schnittstelle bietet sich das Prozess Design Kit (PDK) an, da dort bereits die relevanten Parameter für das Nominalverhalten der Bauelemente sowie deren statistisches Verhalten abgelegt sind. Ein Format dafür ist bislang nicht standardisiert. Erste Anstrengungen in dieser Richtung werden in Form des iPDK und des OpenPDK unternommen. Mit der Frage, wie sich das Degradationsverhalten in Bauelementemodellen abbilden lässt, beschäftigt sich auch das Compact Modelling Council (CMC).

Die Hersteller der verschiedenen Designumgebungen müssen die Zuverlässigkeitsinformationen aufnehmen, um sie in der jeweiligen Alterungsanalyse verwenden zu können. Der Entwerfer schließlich möchte unabhängig von der genutzten Foundry und dem EDA-Tool-Anbieter in der Lage sein, die Anforderungen aus seiner Spezifikation mit den Möglichkeiten der Technologie gegeneinander abzuwägen.

Ein Format für die Ablage von Zuverlässigkeitsinformationen auf verschiedenen Abstraktionsebenen wurde im vergangenen Jahr von Evans et. al. [17] vorgeschlagen. Das sogenannte Reliability Information Interchange Format (RIIF) ist eine eigenständige Beschreibungssprache mit eigener Syntax und soll Standard zum Austausch von Zuverlässigkeitsinformationen werden. Es nutzt eine parametrische Beschreibung von Fehlerwahrscheinlichkeiten und ist modular und hierarchisch angelegt. Durch die Nutzung von Templates ist das Format sehr allgemeingültig.

## 3 Anwendungen & Ergebnisse

Nachfolgend sollen Anwendungsbeispiele die Alterungssimulation illustrieren. Die Transistoren

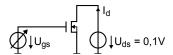

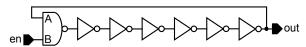

Bild 2 Simulationstestbench für den Einzeltransistor

werden beispielhaft durch prädiktive Low-Power-Transistormodelle für eine 45-nm-Technologie beschrieben [18].

Ursprünglich war der Ansatz (1) zur Beschreibung von PBTI-Alterung für die Prozessüberwachung vorgesehen [7]. Ob er auch in Schaltungssimulationen eingesetzt werden kann, soll durch einen Vergleich von Messungen und Simulationen untersucht werden. Dazu werden aus den Ergebnissen aus [7] die Modellkoeffizienten

$$\begin{array}{rcl} A & = & 0,0016 & \frac{1}{V^{m-1} \cdot s^n}, \\ m & = & 5,46 \text{ und} \\ n & = & 0.18 \end{array}$$

abgelesen [8], [9], [19]. Diese werden in der Alterungssimulation mit der Testbench in Bild 2 verwendet. Dabei werden wie bei der Messung die Schwellspannungsverschiebungen  $\Delta U_{\rm th}$  für zwei Fälle untersucht [9], [19].

- Statischer Stress: Der Stress in Form der Gate-Source-Spannung wird konstant gehalten. Zwei Simulationen unterscheiden sich jedoch in der Höhe der Stressspannung.

- Dynamischer Stress: Der Stress wird durch eine von 0 ansteigende Gate-Source-Spannung erzeugt. Dabei können die Anstiegsgeschwindigkeit und der Maximalwert der Gate-Source-Spannung verändert werden.

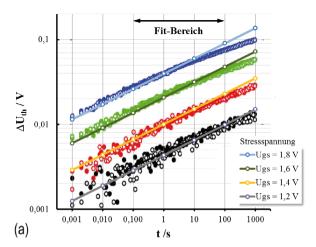

Die in Bild 3 gegenübergestellten Messwerte und Simulationsergebnisse stimmen gut überein. Das gilt vor allem für die von Kerber definierten Fit-Bereiche sowohl für statischen als auch für dynamischen Stress. Allerdings geht aus den Grafiken in Bild 3 auch hervor, dass der einfache Modellansatz in (1) nicht ausreicht. Die Messwerte deuten auf eine Sättigung der Degradation hin, was mit dem in der Simulation verwendeten Modell nicht nachgebildet werden kann.

Es ist jedoch zu beachten, dass das vorliegende PBTI-Modell keine Relaxation beinhaltet. Dieses Verhalten wird im vorliegenden Belastungsfall des Einzeltransistors jedoch auch nicht benötigt, weil die zur Prozessüberwachung angedachten Belastungsmuster keine stressfreien Phasen beinhalten.

Mit diesem Beispiel konnte nachgewiesen werden, dass das PBTI-Modell zumindest in Simulationen von Einzeltransistoren mit den betrachteten Stressbedingungen eingesetzt werden kann. Ob es sich auch für Transistorschaltungen eignet, wird an einem 7-stufigen digitalen Ringoszillator untersucht. Wie in der Gatterschaltung in Bild 4 dargestellt, besteht der Oszillator

**Bild 3** Vergleich von Messungen (Punkte) und Simulationen (durchgezogene Geraden) am Einzeltransistor bei  $T=125^{\circ}\mathrm{C}$ , (a) statischer (konstanter) Stress unterschiedlicher Höhe, (b) dynamischer Stress durch linear ansteigende Gate-Source-Spannung mit unterschiedlicher Anstiegsgeschwindigkeit [9], [19]

aus einem NAND2-Gatter und 6 Invertern. Über das Steuersignal *en* kann er aktiviert und deaktiviert werden.

Weil der Oszillator nicht für seine gesamte Betriebsdauer simuliert werden kann, dient das folgende Szenario als typischer Anwendungsfall für die Extrapolation.

- Betriebsspannung  $U_{\mathrm{dd}} \!=\! 1,\! 1\ \mathrm{V}$

- Temperatur T = 125 °C

- Steuersignal: für  $0 \le t \le 10~\mathrm{ps}~U_\mathrm{en}\!=\!0$ , für  $10~\mathrm{ps} < t \le 11~\mathrm{ps}$  linear auf 1,1~V ansteigend, danach konstant auf  $U_\mathrm{en}\!=\!1,1~V$

- Simulationsdauer  $t_{\rm sim}\!=\!2,\!2~{\rm ns}$  und Extrapolation nach (4)

Das vorgestellte PBTI-Modell wird auf alle NFETs des Oszillators angewendet. Als Ergebnisse werden

Bild 4 Gatterschaltung des digitalen Ringoszillators aus einem NAND2-Gatter und 6 Invertern

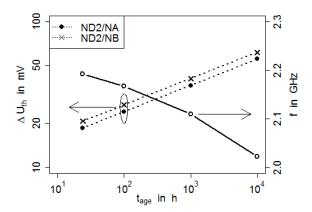

$\mbox{Bild 5}$  Schwellspannungsverschiebungen der NFETs des NAND2-Gatters (ND2/NA UND ND2/NB) und Oszillatorfrequenz über der Lebensdauer; für  $t_{\rm age}\!=\!0$  gelten  $\Delta U_{\rm th}\!=\!0$  und  $f\!=\!2,278{\rm GHz}$

die Schwellspannungsverschiebungen  $\Delta U_{\rm th}$  der beiden NFETs des NAND2-Gatters betrachtet. Sie sind anhand der zugehörigen Pins des Gatters mit ND2/NA und ND2/NB bezeichnet. Es ist zu beachten, dass der Transistor ND2/NA an der Oszillation beteiligt ist, während der Transistor ND2/NB vorrangig statischen Stress durch das Steuersignal en erfährt. Die Vermutung, dass der letztgenannte Transistor deshalb einer stärkeren Schwellspannungsverschiebung unterliegt, wird durch die Zeitverläufe in Bild 5 bestätigt. Die Schwellspannungsverschiebung des Transistors ND2/NA (ND2/NB) beträgt z.B. nach  $t_{\rm age} = 24h$   $18.66 {\rm mV}$  ( $20.81 {\rm mV}$ ) und nach  $t_{\rm age} = 10^4 {\rm h}$   $55.28 {\rm mV}$  ( $61.64 {\rm mV}$ ).

Das Bild 5 zeigt auch die Entwicklung der Oszillationsfrequenz f mit der Zeit. Sie nimmt von Zeitpunkt  $t_{\rm age}\!=\!0$  mit  $f\!=\!2,278{\rm GHz}$  im Betrieb kontinuierlich ab. Dieser Effekt ist auch zu erwarten, weil die ansteigenden Schwellspannungen der NFETs durch PBTI-Alterung deren Schaltgeschwindigkeiten verringern. Ob die ermittelte Frequenzverringerung um 4.9% nach  $t_{\rm age}\!=\!10^2h,~7.4\%$  nach  $t_{\rm age}\!=\!10^3h$  und 11.2% nach  $t_{\rm age}\!=\!10^4h$  für die Schaltungsfunktion kritisch sind, hängt von der jeweiligen Spezifikation ab. Wie sich die Alterung auf das Schaltungsverhalten auswirkt, kann demnach nur für die konkrete Applikation bewertet werden.

Wiederum ist zu beachten, dass der Modellansatz in (1) keine Relaxation berücksichtigt. Vor allem für die an der Oszillation beteiligten NFETs wird die Schwellspannungsverschiebung dadurch ungenau, nämlich zu groß bestimmt. Durch diesen Aspekt ist die Abschätzung der PBTI-Alterung mit dem vorliegenden Modell pessimistisch. Der Oszillator wird durch PBTI-Alterung in der Realität also weniger stark degradieren, als per Simulation bestimmt. Es ist jedoch offensichtlich, dass auch andere Alterungseffekte, wie HCI an den NFETs oder NBTI an den PFETs, den Oszillator beeinflussen. Diese Effekte müssen in zukünftigen Modellen also ebenfalls berücksichtigt werden.

## 4 Danksagung

Diese Arbeit wurde mit Mitteln des Bundesministeriums für Bildung und Forschung (BMBF) im Rahmen des Projekts "Design for Reliability of SoCs for Applications like Transportation, Medical, and Industrial Automation" (RELY) unter dem Förderkennzeichen 16M3091C gefördert.

## 5 Literatur

- [1] B. Mesgarzadeh, I. Söderquist, and A. Alvandpour, "Reliability challenges in avionics due to silicon aging," in *IEEE International Symposium on Design and Diagnostics of Electronic Circuits Systems (DDECS)*, 2012.

- [2] http://www.cadence.com.

- [3] http://www.mentor.com.

- [4] http://www.synopsys.com.

- [5] T. Grasser et al., "A two-stage model for negative bias temperature instability," in *IEEE International Reliability Physics* Symposium (IRPS), 2009.

- [6] V. Huard, M. Denais, and C. Parthasarathy, "NBTI degradation: From physical mechanisms to modelling," *Microelectro*nics Reliability, vol. 46, no. 1, 2006.

- [7] A. Kerber, S. Krishnan, and E. Cartier, "Voltage Ramp Stress for Bias Temperature Instability Testing of Metal-Gate/High-k Stacks," *IEEE Electron Device Letters*, vol. 30, no. 12, 2009.

- [8] C. Sohrmann et al., "The DECO framework: Reliability simulation based on a general design-environment communication approach," in EdaWorkshop 2013, W. Rosenstiel, Ed. Berlin: VDE VERLAG, Mai 2013.

- [9] L. Müller et al., "CHRONOS: Ein Werkzeug zur Berücksichtigung von Alterungseffekten in Schaltungssimulationen," in DASS 2013 – Tagungsband, P. Schneider and T. Klotz, Eds. Stuttgart: FRAUNHOFER VERLAG, April 2013.

- [10] D. Lorenz, G. Georgakos, and U. Schlichtmann, "Aging analysis of circuit timing considering NBTI and HCI," in *IEEE International On-Line Testing Symposium (IOLTS)*, 2009.

- [11] E. Maricau and G. Gielen, "Efficient Variability-Aware NBTI and Hot Carrier Circuit Reliability Analysis," *IEEE Transac*tions on Computer-Aided Design of Integrated Circuits and Systems, vol. 29, no. 12, 2010.

- [12] T. Grasser et al., "The time dependent defect spectroscopy (TDDS) for the characterization of the bias temperature instability," in IEEE International Reliability Physics Symposium (IRPS), 2010.

- [13] H. Reisinger et al., "The statistical analysis of individual defects constituting NBTI and its implications for modeling DC-and AC-stress," in IEEE International Reliability Physics Symposium (IRPS), 2010.

- [14] P. Moens and G. Van den Bosch, "Characterization of Total Safe Operating Area of Lateral DMOS Transistors," *IEEE Transaction on Device and Materials Reliability*, vol. 6, no. 3, 2006.

- [15] R. Jancke, C. Ellmers, and R. Gaertner, "Design of reliable circuits by determination of SOA borders as part of the degradation analysis," in *Semiconductor Conference Dresden (SCD)*. Martinsried: Gerotron Communication, 2009.

- [16] E. Haibach, Betriebsfestigkeit: Verfahren und Daten zur Bauteilberechnung, 3rd ed., ser. VDI. Berlin: Springer, 2006.

- [17] A. Evans *et al.*, "RIIF Reliability information interchange format," in *IEEE International On-Line Testing Symposium* (*IOLTS*), 2012.

- [18] Arizona State University, Nanoscale Integration and Modeling Group, "Predictive Technology Model. 45nm PTM LP model: V2.1," http://ptm.asu.edu/modelcard/HP/45nm\_HP.pm, Februar 2008

- [19] L. Müller, "Aufbau einer Umgebung für die Simulation des Alterungsverhaltens von integrierten elektronischen Schaltungen," Technische Universität Dresden, Diplomarbeit, März 2013.