# Robuste und zuverlässige Leistungselektronik: Umwelt- und Lebensdauertests

8. Kooperationsforum Leistungselektronik Novum Businesscenter Würzburg

Andreas Schletz

#### 01.10.2019

### Contents

- Definition of robustness, reliability and lifetime

- Challenges for the testing WBG

- Semiconductor

- Capacitors

- Summary

Slide 2 01.10.2019 Andreas Schletz © Fraunhofer IISB

### Definition

- Robustness is the probability that a product performs its intended function for a specified period of time under a specified set of operating conditions.

- Reliability is the probability that a product performs its intended function for a <u>specified</u> period of time under a specified set of operating conditions. (VDI guideline 4001)

- Robustness and Reliability are a function of time, whereby the "time" is measured differently

- Operating time

- Mileage (automotive)

- Durability

- Load cycles

- Not directly measureable

- Described by survival probability

### **Reliability Testing**

- Lifetime is tested by (accelerated) lifetime tests

- Acceleration is made by overload

- Important: Failure mechanism must not be changed by the overload testing

- Reliability is the statistical lifetime

- Robustness compares the reliability to the mission profile and defines a robustness margin

Slide 4 01.10.2019 Andreas Schletz © Fraunhofer IISB

### **Reliability and Lifetime of Wide Bandgap technology**

- Low R<sub>DS,ON</sub> or low chip size, high current density

- High switching speed, availability of high voltage unipolar devices

- High switching frequency  $\rightarrow$  stress for passive components

- (High temperature operation)

Slide 6 01.10.2019 Andreas Schletz © Fraunhofer IISB

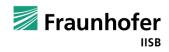

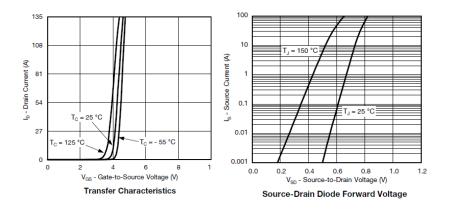

#### Static Losses of FETs

- Heating is done by DC current (state of the art)

- $\blacksquare P = I^2 * R_{DS,ON}$

- Extremely low R<sub>DS,ON</sub> limits the power losses

- dT is hard to achieve by heating current only current; may be limited by package or semiconductor die

- Gate voltage has to be reduced down to the limits (has to be well above threshold under all circumstances)

- Solution

- Use body diode for heating (approx. 3V forward voltage)

- Use switching losses as additional heat source  $\rightarrow$  complicated setup

www.leickel.de

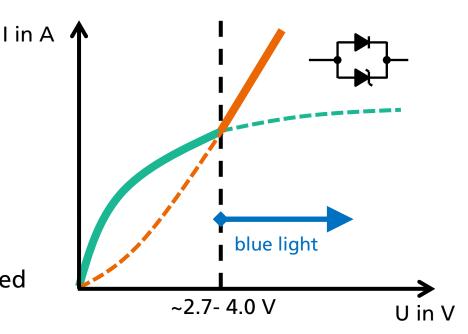

- Electric performance of the semiconductor devices under test

- Example

- Small device → excellent heat spreading → high power loss needed

- High heating current needed

- SiC schottky used

- Device operating the merged pn structure (overcurrent protection)

- Exceeding datasheet values ...

Slide 8 01.10.2019 Andreas Schletz © Fraunhofer IISB

A.Hutzler et.al., Increasing the lifetime of electronic packaging by higher temperatures: solders vs. silver sintering, 64th Electronic Components and Technology Conference, ECTC 2014 : 27-30 May 2014, Orlando, Florida, USA

- For FETs: Use low gate voltage

- Higher forward voltage, lower current, higher losses → higher temperature swing

Drawback

- Negative temperature coefficient of threshold voltage

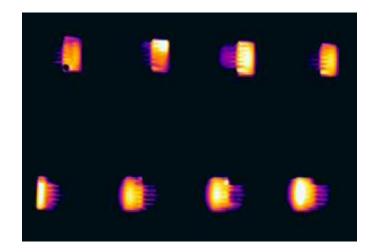

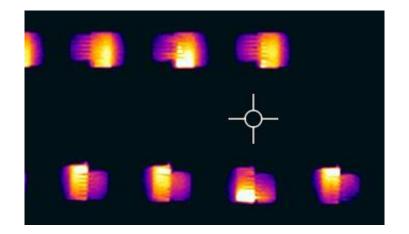

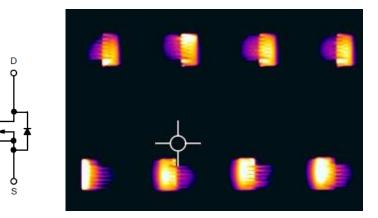

- Different heating of semiconductors according to they local electrical and thermal performance

- No application relevant situation

- Virtual temperature measurement becomes free to interpret

- Inhomogeneous temperature distribution over chip surface

- Possible overheating in the first ms

- For FETs: Use body diode for heating

- Higher forward voltage, lower current, higher losses  $\rightarrow$  higher temperature swing

Drawback

- Negative temperature coefficient

- Different heating of semiconductors according to they local electrical and thermal performance

- No application relevant situation

- Virtual temperature measurement becomes free to interpret

- No control no fine tuning

- Inhomogeneous temperature distribution over chip surface

Slide 11 01.10.2019 Andreas Schletz © Fraunhofer IISB

Funded by FuE-Program "Elektronische Systeme" Freistaates Bayern/ Germany; Input taken from Fabian Dresel/ Fraunhofer IISB

- Work around #1 (for FETs only):

- Use body diode for heating and slightly open FET channel at the same time

- During the heating up: application of a positive gate voltage near the threshold

- Temperature difference between chip is much better

- More homogeneous temperature distribution on chip

- Operating principle

- PN diode is in parallel to the FET

- FET's threshold decreases with increasing temperature → channel opens at hot regions, cutting down temperature self-controlled

- But: 2. theoretical possibility: dominant heating current flows through FET channel intensifying the hot spot

- Behavior dependent on electro-/ thermal performance of the semiconductor

- Drawback: No common mind, no standard

Slide 12 01.10.2019 Andreas Schletz © Fraunhofer IISB

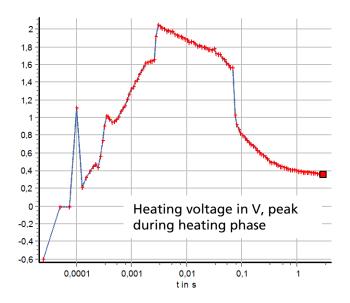

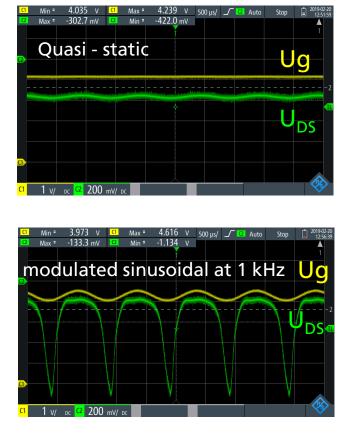

- Work around #2 (for FETs only):

- Operating principle

- Simple applied "Switching losses"

- Heating in forward direction

- gate voltage with AC (any waveform) plus DC offset

- Heating power is equivalent to the area below U<sub>DS</sub> curve

- Very stable operating point

- No inhomogeneous chip temperature

- Drawback: No common mind, no standard

Slide 13 01.10.2019 Andreas Schletz © Fraunhofer IISB

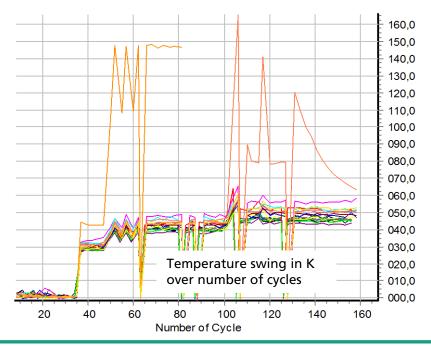

## **Drift of FET's Gate Threshold Voltage**

#### Drift of gate threshold voltage

- Heating power @ static gate voltage changes due to the effect

- Dependent on test parameters

- t<sub>on</sub> t<sub>off</sub> ratio

- Temperature

- Voltage levels for heating and cooling

- Maybe pos./ neg. gate voltage impact different

- Reversible, particular during test system shut down (undefined down time)

- Solution

- Identify drift and re-adjust gate voltage during test

- Develop new end of life failure criterion

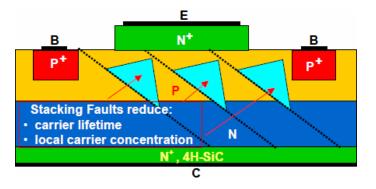

### **SiC Bipolar Degradation**

- SiC MOSFETs have bipolar body diodes

- SiC bipolar devices suffer from material defects

- Failure cause: Current and temperature

Qingchun (Jon) Zhang et.al.: Degradation Mechanisms in SiC Bipolar Junction Transistors

Slide 16 01.10.2019 Andreas Schletz © Fraunhofer IISB

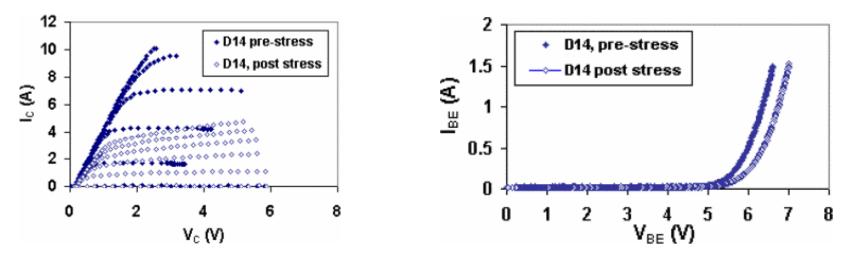

### SiC Bipolar Semiconductor Parameter Drift

- SiC body diode my suffer from degradation (some manufacturers use a pre-scanning of wafers to sort out infected areas)

- Problem

- Temperature sensor is drifting away

- Poor results by indirect temperature measurement

- Solution

- Recalculate temperature by voltage offset (error prone)

- Recalibration of sensor voltage

- Develop new end of life failure criterion

- Just wait (seems to be a solved issue because of improved wafer quality)

### **WBG Semiconductors Challenges Summary**

- Big variety of challenges

- The test acceleration limit is a general problem for WBG

- The drift of the semiconductor parameters cause poor accuracy of the indirect temperature measurement

- Solutions are available

- No common understanding for testing of WBG devices at the acceleration limit

#### Good news:

The aging of semiconductors is an additional test result which is gained free of charge!

$\rightarrow$  why not use it and define new EOL criteria

### **Power Cycling Lifetime - SiC**

|                                                     | Si @ 20°C                          | SiC-4H 20°C                          | Lifetime compared to Si                                                      |

|-----------------------------------------------------|------------------------------------|--------------------------------------|------------------------------------------------------------------------------|

| Thermal<br>conductivity in<br>W/(m*K)               | 150                                | 380                                  | Chip have higher<br>temperature due to better<br>heat spreading <sup>1</sup> |

| Specific heat<br>capacity in J/kg*K                 | 700                                | 690                                  | Not a big difference                                                         |

| CTE in ppm/K                                        | 3                                  | 4,3                                  | Better "matching" to packaging materials                                     |

| Youngs Modulus in<br>GPa                            | 162                                | 507/547/<br>159/108<br>(anisotropic) | ⊗ Increased stress                                                           |

| Die thickness in µm<br>for 650V                     | 40120                              | 180325<br>+/-40µm                    | <ul><li>Increased stress</li><li>Wider distribution</li></ul>                |

| Normalized die size<br>in mΩcm <sup>2</sup> @ 25°C  | 142mm²*11mΩ<br>= 15,6 <sup>3</sup> | 26mm²*25mΩ<br>= 6,5 <sup>2</sup>     | ☺ or ⊗<br>2,4x smaller die size                                              |

| Normalized die size<br>in mΩcm <sup>2</sup> @ 150°C | 142mm²*14mΩ<br>= 19,9 <sup>3</sup> | 26mm²*25mΩ<br>= 11,1 <sup>2</sup>    | ☺ or ⊗<br>1,8x smaller die size                                              |

Slide 19 01.10.2019 Andreas Schletz © Fraunhofer IISB

<sup>1</sup> Ch. Herold et.al.: Power cycling capability of Modules with SiC-Diodes, CIPS 2014, February, 25 – 27, 2014, Nuremberg/Germany <sup>2</sup> Wolfspeed CPM2-1200-0025B

<sup>3</sup> Infineon IGC142T120T8RH

## **Power Cycling Lifetime - SiC**

- Lifetime of SiC is about 30%..40%<sup>1</sup> than of Si (Sn solder, Al bond wires)

- Application

- Temperature swing has to be lower in order to fulfill lifetime requirements

- Bigger chip size is needed

- Outlook to the future

- R<sub>DS,ON</sub> reduction will go on

- Improvement is based on technology improvements and back grinding of SiC-Wafers

- Dies will be less thick  $\rightarrow$  thermo-mechanical lifetime will increase

- At the same time the current density will increase  $\rightarrow$  smaller die

## Testing...

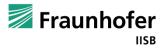

### **Capacitors for power electronics**

Applications

DC-Link

Snubber

Technologies

Film

- Electrolytic

- Ceramic

- Silicon

Maximum efficiency for inverters Reference design, TDK Electronics AG, 2017

Fraunhofer IISB

RONG Rui , "AN-Power stage of 48V BSG inverter Reference design with TOLL & TOLG MOSFET", <u>www.infineon.com</u>, 2018

### Worth to test

Slide 23 01.10.2019 Andreas Schletz © Fraunhofer IISB

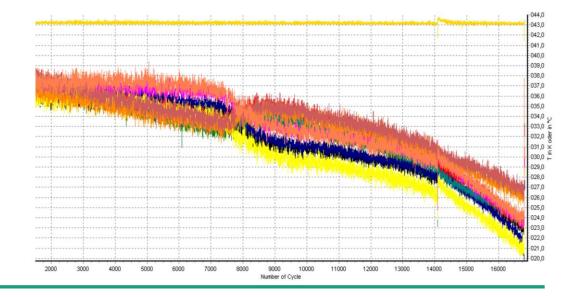

### **Example: Film Capacitor**

- Test with application near self heating

- Materials have different mechanical properties

- Coefficient of thermal expansion (CTE)

- PP: 100ppm/K; Zn: 30ppm/K; Cu: 17ppm/K

- Young's Modulus, fracture toughness, ... (all temperature dependent)

- Result: Thermo-mechanic ageing

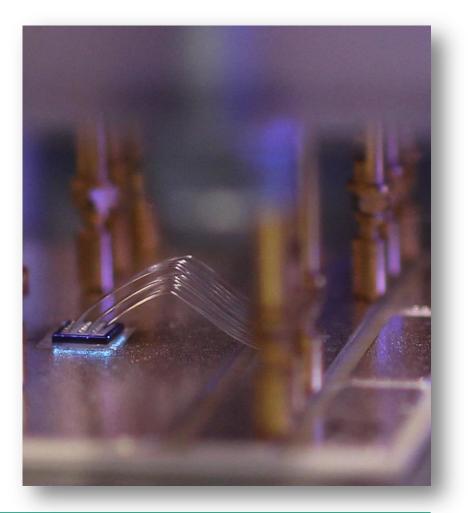

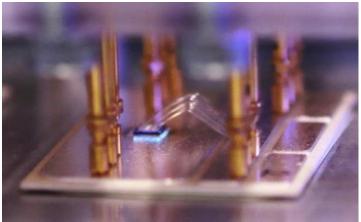

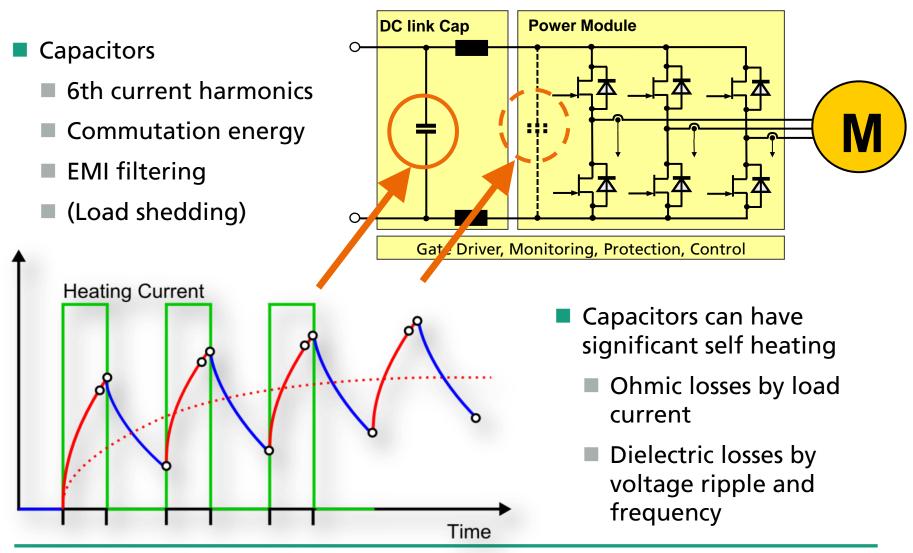

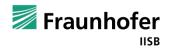

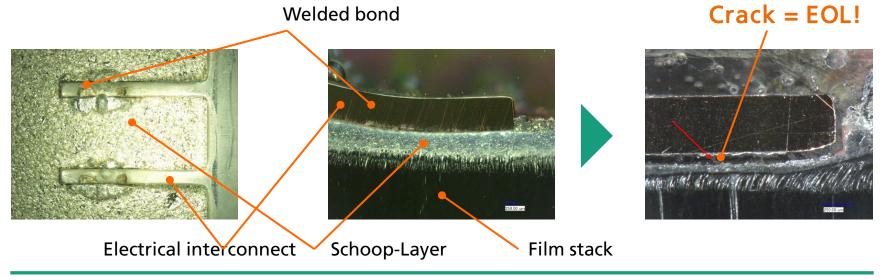

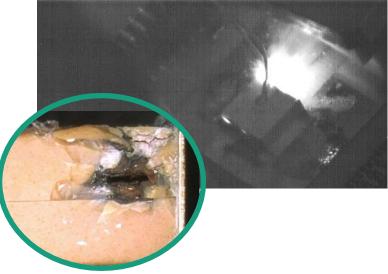

### **Example: Ceramic Capacitor – Module Integrated**

- Test with application near self heating

- "Commutation capacitor" to reduce the parasitic inductance of the commutation cell in snubber or dc-link configuration

- Ceramic capacitors have no ductile materials (capacitor crack is a well known failure mechanism)

- Capacitors can have significant heating

- passively by the power semiconductor → active PCT of active devices

- active by own power losses → active PCT of passive devices

Ceramic DC link capacitor at end of life

### **Capacitors summary**

- Current test for (power)capacitors: AEC-Q200/ JEDEC

- Standards made for small signal components, mainly SMD on PCB

- Based on constant failure rate

- Passive temperature shock test used

- No application near (inhomogenious) temperature distribution

- Robustnesss margin unknown (qualification, no EOL testing)

- 1. step to improve standardisation for testing of DC link film capacitors "Qualifikation von Zwischenkreis-kondensatoren für den Einsatz in Komponenten von Kraftfahrzeugen, ZVEI", 2017

- No data basis for thermo-mechanic wear out failures for power capacitors available → reduction of over engineering not possible

- Outlook: Testing with application near temperature distribution (=self heating) to EOL

- Determination of failure mechanisms

- Identification of weak points

- Development of systematic technology improvements

- Definition of end of life criteria

- Life time modelling, based on physics of failure

Slide 26 01.10.2019 Andreas Schletz © Fraunhofer IISB

### Summary

- Wide band gap (SiC presented) has some issues not known from Si

- Parameter drift

- Problematic thermo-mechanical testability due to extremely low R<sub>DS,ON</sub>

- Overall power cycling lifetime is 30% of Si caused by material and device thickness

- Power cycling testing shows most of the mechanisms for free !

- Fast switching moves passives into the focus

- Capacitors get significant self heating

- Especially power module integrated snubbers may have high power losses

- Cyclic self heating degrades interfaces and dielectric

- No data basis and models available  $\rightarrow$  a lot of research work to do

### Fraunhofer IISB

#### **Energy Electronics**

Materials

### **POWER ELECTRONIC SYSTEMS**

From Material to Power Electronic Applications • Everything from One Partner •

Technologies

Devices, Moduls and Reliability Vehicle Electronics

Andreas Schletz Andreas.Schletz@iisb.fraunhofer.de Tel. +49 9131 761 187 Schottkystr. 10 91058 Erlangen www.iisb.fraunhofer.de

Slide 28 01.10.2019 Andreas Schletz © Fraunhofer IISB

# References

- [1] BAYER, Christoph: High Temperature in Power Electronics for Automotive Applications. Erlangen, 2015

- **[2]** YOLE DÉVELOPPEMENT: SiC and GaN devices for the power electronics market. In: *i*-Micronews (2017)

- [3] MANTOOTH, H. Alan ; MOJARRADI, Mohammad M. ; JOHNSON, R. Wayne: Emerging Capabilities in Electronics Technologies for Extreme Environments. In: IEEE Power Electronics Society Newsletter 9 (2006)

- [4] BAILEY, Chris: Co-Design and Reliability Modelling for Power Electronics Modules: Current Status and Future Challenges. In: ECPE Workshop Thermal and Reliability Modelling and Simulation of Power Electronics Components and Systems 2016

- [5] CERAMTEC: Advanced Ceramic Material Properties for the Electronics Industry. URL https://www.ceramtec.com/files/el\_advanced\_ceramic\_material\_properties\_en.pdf – Check date 2016-12-19

- [6] RASTJAGAEV, Eugen ; WILDE, Jürgen ; WIELAGE, Bernhard ; GRUND, Thomas ; KÜMMEL, Sabine: Development and testing of cold gas sprayed circuit boards for power electronics applications. In: Integrated Power Electronics Systems (CIPS), 2012 7th International Conference on, 2012

- [7] SYED-KHAJA, Aarief; PEREZ, Philip Patino; FRANKE, Joerg: Production and Characterization of Hightemperature Substrates through Selective Laser Melting (SLM) for Power Electronics. In: CPMT Symposium Japan (ICSJ), 2016 IEEE, 2016, S. 255–258

- [8] NING, X. S. ; OGAWA, Y. ; SUGANUMA, K.: Interface of Aluminum/Ceramic Power Substrates manufactured by Casting-Bonding Process, Bd. 445. In: MATERIALS RESEARCH SOCIETY SYMPOSIUM PROCEEDINGS, 1997, S. 101– 106

- [9] TT ELECTRONICS: Anotherm Plus. URL www.ttelectronics.com Check date 2016-12-20

- [10] TROEGER, K.; DARKA, R. Khanpour; NEUMEYER, T.; ALTSTAEDT, V.; ALTSTÄDT, V.; KELLER, Jan-Hendrik; FATHI, Amir: Tailored Benzoxazines as Novel Resin Systems for Printed Circuit Boards in High Temperature E-mobility Applications, Bd. 1593. In: AIP Conference Proceedings, 2014, S. 678–682

- [11] CURAMIK ELECTRONICS GMBH: DBC technology : Design Rules Version 12/2014, 2014

# References

- [12] KYOCERA: AMB Cu-Bonded Ceramic Substrates for Power Modules, 2014

- [13] HERAEUS ELECTRONICS: Heraeus Thick Copper Conductor Pastes. URL https://www.heraeus.com/media/media/het/doc\_het/products\_and\_solutions\_het\_documents/thick\_film/Brochur e\_Heraeus\_Thick\_Copper\_Conductor\_Pastes.pdf – Check date 2017-01-20

- [14] HUTZLER, Aaron ; TOKARSKI, Adam ; SCHLETZ, Andreas: High Temperature Die-attach Materials for Aerospace Power Electronics: Lifetime Tests and Modeling. In: Aerospace Conference, 2015 IEEE, 2015

- [15] DERIX, David ; ZISCHLER, Sigrid ; REINER, Richard: Projekt: GaNPV Einsatz von monolithischen GaN-Halbleitern in PV-Wechselrichtern zur Verbesserung von Lebensdauer und Effizienz. Freiburg, 2015

- [16] RANDOLL, Richard ; WONDRAK, Wolfgang ; SCHLETZ, Andreas: Dielectric strength and thermal performance of PCB-embedded power electronics. In: Microelectronics Reliability 54 (2014), Nr. 9, S. 1872–1876

- [17] BAYER, Christoph Friedrich; WALTRICH, Uwe; SOUEIDAN, Amal; BAER, Eberhard; SCHLETZ, Andreas: Partial Discharges in Ceramic Substrates-Correlation of Electric Field Strength Simulations with Phase Resolved Partial Discharge measurements. In: Transactions of The Japan Institute of Electronics Packaging 9 (2016), E16-003

- [18] TSENG, Tsan-Hsien; WU, Albert T.; CHANG, Yu-Ting; SHI, H. C.; LEE, Jeffrey: Creep Corrosion on High Reliability Printed Circuit Boards. In: *Microsystems, Packaging, Assembly and Circuits Technology Conference* (*IMPACT*), 2016 11th International, 2016, S. 156–158

- [19] ZORN, Christian ; KAMINSKI, Nando: Temperature-humidity-bias testing on insulated-gate bipolartransistor modules-failure modes and acceleration due to high voltage. In: IET Power Electronics 8 (2015), Nr. 12, S. 2329– 2335

- [20] STAHR, H.; UNGER, M.; NICOLICS, J.; MORIANZ, M.; GROSS, S.; BÖTTCHER, L.: Thermal Benchmark of a Classic and Novel Embedded High-Power 3-Phase Inverter Bridge. In: *Electronic System-Integration Technology Conference ESTC 2016*

- [21] KYOCERA: AMB Cu-Bonded Ceramic Substrates for Power Modules, 2014

- [22] Curamik Electronics GmbH: Patentschrift, 2012